- •Системы автоматического управления (сау)

- •Сумматоры

- •Системы обработки информации

- •Обобщённая структурная схема вычислительной системы

- •Сравнительная оценка цифровых и аналоговых устройствмикроэлектронной техники

- •Достоинства технических средств цифровой техники

- •Мультиплексоры Демультиплексоры

- •Классификация микроэлектронных устройств.

- •XI равна 1только еслиAi и Bi равны.

- •Синхронные rs-триггеры.

- •Классификация интегральных схем (плис)

- •Комбинационные плис

- •Системы на кристале

- •Синхронные и асинхронные счётчики

- •Карты карно

- •Risc-процессоры

- •Системы счисления

- •Гарвардская архитектура

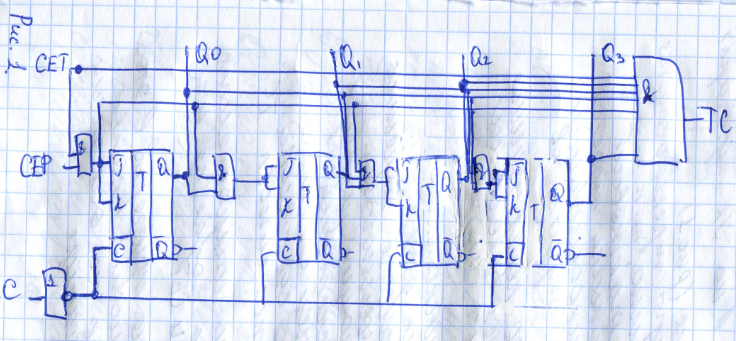

Синхронные и асинхронные счётчики

Принципиальная схема одного из вариантов синхронных двоичных счётчиков на JK-тригерах. В этой схеме все тригеры переключаются одновременно, т.к. выходной тактовый сигнал счётчика подаётся на вход синхронизации сразу всех тригеров. Разрешение переключения формируется схемами «И». При исполнении нескольких микросхем для формирования переноса, предназначенного для последующих разрядов двоичного счётчика в приведённой схеме синхронного счётчика формируется сигнал ТС.

В следующих микросхемах этот сигнал подаётся на выходы СЕР и СЕТ. Переключение тригеров в этой схеме возможно только при подаче на оба этих выхода единицы.

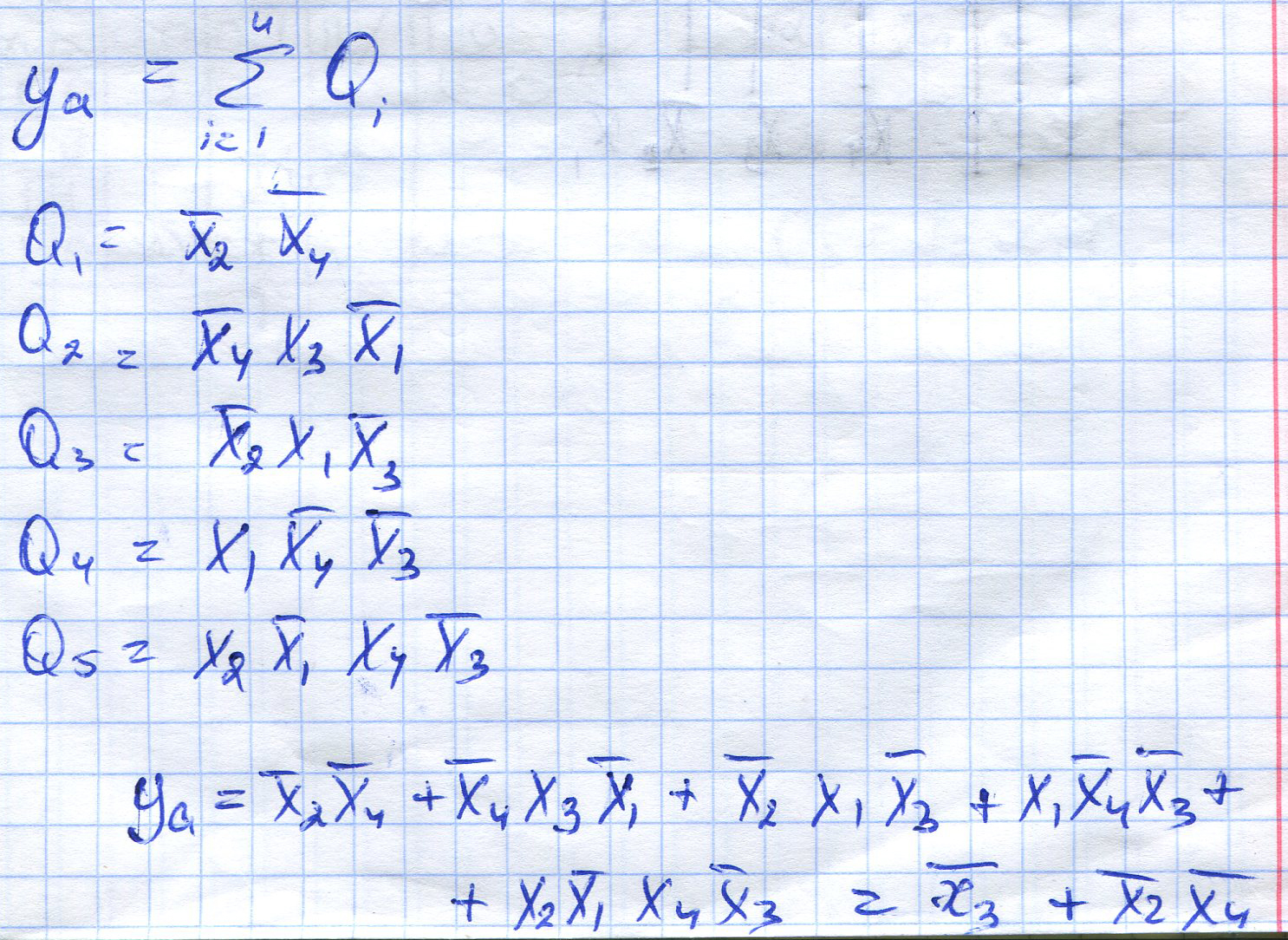

Карты карно

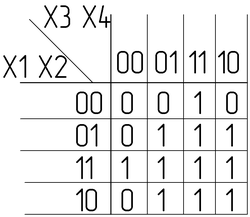

Минимизация входной логической ф-ции осуществляется с помощью карт Карно.

По этим картам Карно минимизированные лог.ф-ции выглядят спец образом. Выбираем максимальное симметричное четное значение 1

Меняющиеся не учитываем, считаем только постоянные.

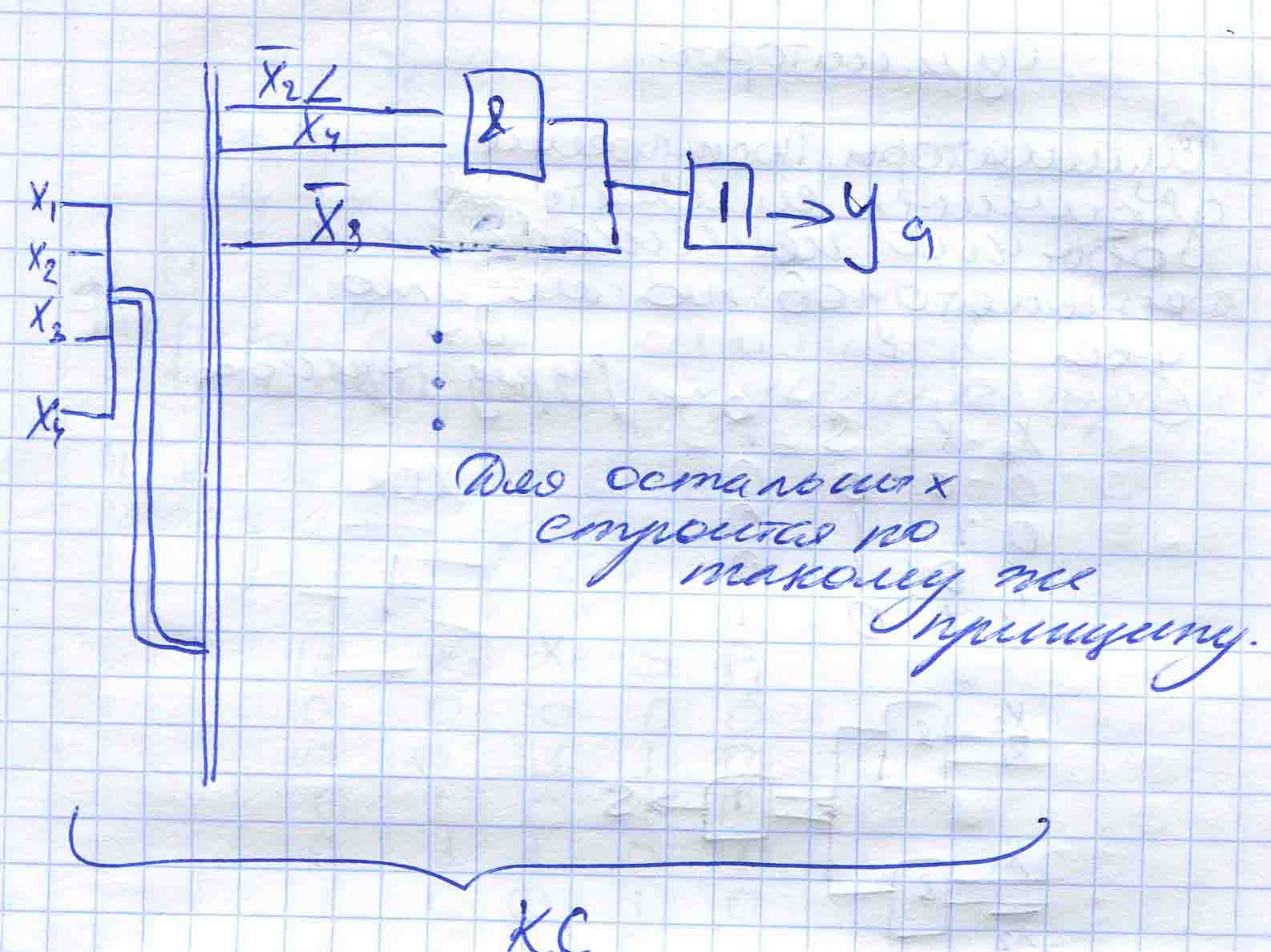

Остальные делаются по аналогии (используя правила законов логики)

КС – комбинационная схема

Далее пример

Все области содержат 2^n клеток;

2. Так как Карта Карно на четыре переменные, оси располагаются на границах Карты и их не видно (подробнее смотри пример Карты на 5 переменных);

3. Так как Карта Карно на четыре переменные, все области симметрично осей — смежные между собой (подробнее смотри пример Карты на 5 переменных);

4. Области S3, S4, S5, S6 максимально большие;

5. Все области пересекаются (необязательное условие);

6. В данном случае рациональный вариант только один.

![]()

![]()

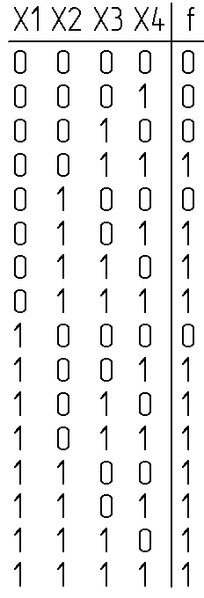

Карта Карно́ —графическийспособминимизациипереключательных (булевых) функций, обеспечивающийотносительнуюпростотуработысбольшимивыражениямииустранениепотенциальныхгонок. Представляетсобойоперации попарного неполного склеивания и элементарного поглощения. Карты Карно рассматриваются как перестроенная соответствующим образом таблица истинности функции. Карты Карно можно рассматривать как определенную плоскую развертку n-мерного булева куба.

Карта Карно может быть составлена для любого количества переменных, однако удобно работать при количестве переменных не более пяти. По сути Карта Карно — это таблица истинности составленная в 2-х мерном виде. Благодаря использованию кода Грея в ней верхняя строка является соседней с нижней, а правый столбец соседний с левым, т.о. вся Карта Карно сворачивается в фигуру тор (бублик). На пересечении строки и столбца проставляется соответствующее значение из таблицы истинности. После того как Карта заполнена, можно приступать к минимизации.

Если необходимо получить минимальную ДНФ, то в Карте рассматриваем только те клетки которые содержат единицы, если нужна КНФ, то рассматриваем те клетки, которые содержат нули. Сама минимизация производится по следующим правилам (на примере ДНФ):

Объединяем смежные клетки, содержащие единицы, в область так, чтобы одна область содержала 2n (n целое число = 0…) клеток (помним про то, что крайние строки и столбцы являются соседними между собой), в области не должно находиться клеток, содержащих нули;

Область должна располагаться симметрично оси(ей) (оси располагаются через каждые четыре клетки);

Несмежные области, расположенные симметрично оси(ей), могут объединяться в одну;

Область должна быть как можно больше, а количество областей как можно меньше;

Области могут пересекаться;

Возможно несколько вариантов покрытия.

Далее берём первую область и смотрим, какие переменные не меняются в пределах этой области, выписываем конъюнкцию этих переменных; если неменяющаяся переменная нулевая, проставляем над ней инверсию. Берём следующую область, выполняем то же самое, что и для первой, и т. д. для всех областей. Конъюнкции областей объединяем дизъюнкцией.

СФ-блоки

IP cores (IP-ядра) (от англ. IntellectualProperty — интеллектуальный продукт.Также IP-блоки; также англ. virtualcomponents, VC — виртуальные компоненты) — готовые блоки для проектирования микросхем (например, построения систем-на-кристалле).

Различают 3 основных класса блоков:

программные IP-блоки (англ. softblocks) — блоки, специфицированные на языке описания аппаратуры.

схемотехнические блоки (англ. firmblocks) — блоки, специфицированные на схемотехническом уровне, без привязки к конкретной топологической реализации.

физические (топологические) блоки (англ. hardsblocks) — блоки, специфицированные на физическом уровне реализации СБИС, например, GDSII для ASIC.

Hard IP-Core — сложно-функциональный блок, передаваемый потребителю в виде законченной схемотехнической конструкции, разработанной на основе базы данных для проектирования изготовителя микросхем и оптимизированной по размерам, потребляемой мощности и электрическим характеристикам.

Hard IP-Core — специализированные области кристалла, выделенные для определенных функций. В этих областях создаются блоки неизменной структуры, спроектированные по методологии ASIC (как области типа БМК или схем со стандартными ячейками), оптимизированные для заданной функции и не имеющие средств ее программирования[1].

В случае использования данного вида ядер размер площади используемой на кристалле — сокращается, улучшаются характеристики быстродействия, но в данном случае происходит потеря универсальности.

Построение комбинационных схем Любая логическая схема полностью описывается таблицей истинности. При этом не обязательно, чтобы все комбинации входных данных были полезными или нужными. Возможна ситуация, когда только часть входных комбинаций является полезной. Обычно при этом стараются выбирать выходные сигналы таким образом, чтобы схема получилась простейшая. Для реализации логической схемы с произвольной таблицей истинности используется сочетание простейших логических элементов «И», «ИЛИ», «НЕ». Существует много способов синтеза схем, реализующих произвольную таблицу истинности. Например: СКНФ, СДНФ. Алгоритм построения комбинационной схемы:

Формирование таблицы истинности

Минимизация функции (например с помощью Карт Карно)

После минимизации – непосредственно разработка принципиальной комбинационной схемы.

Системный уровень проектирования интегральных схем: Общий маршрут проектирования систем на кристалле состоит из следующих основных этапов:

концептуальное проектирование системы; основной задачей данного этапа является исследование проектируемой системы и получение исполняемых спецификаций на языке высокого уровня (стандартно на С/С++);

проектирование, то есть трансформация исполняемой спецификации проекта на уровень регистровых передач (получение спецификаций на языках Verilog/VHDL) и далее на вентильный уровень;

верификация проекта, то есть проверка проекта и проектных решений на соответствие исходной спецификации и другим требованиям в процессе проектирования и детализации;

физическое проектирование, начиная от выбора технологического и библиотечного базиса и заканчивая получением финального описания проекта в формате GDSII.

Системный уровень описания (system-leveldescription) проекта состоит из поведенческого описания в терминах функций, выражений, алгоритмов. На уровне регистровых передач (registertransferlevel) проект представляется совокупностью арифметических и логических узлов, элементов памяти и т.п

Основные задачи системного и архитектурного уровней проектирования следующие:

определение принципов организации системы;

выбор архитектуры, уточнение функций системы и их разделение на функции, реализуемые аппаратным и программным путем;

разработка структурной схемы, т.е. определение состава устройств и способов их взаимодействия;

определение требований к выходным параметрам устройств и формирование технических заданий (ТЗ) на разработку отдельных элементов системы