- •Системы автоматического управления (сау)

- •Сумматоры

- •Системы обработки информации

- •Обобщённая структурная схема вычислительной системы

- •Сравнительная оценка цифровых и аналоговых устройствмикроэлектронной техники

- •Достоинства технических средств цифровой техники

- •Мультиплексоры Демультиплексоры

- •Классификация микроэлектронных устройств.

- •XI равна 1только еслиAi и Bi равны.

- •Синхронные rs-триггеры.

- •Классификация интегральных схем (плис)

- •Комбинационные плис

- •Системы на кристале

- •Синхронные и асинхронные счётчики

- •Карты карно

- •Risc-процессоры

- •Системы счисления

- •Гарвардская архитектура

Сумматоры

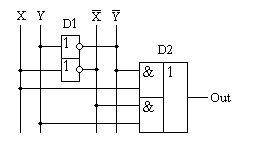

Построение двоичных сумматоров обычно начинается с сумматора по модулю 2

О бычный

сумматор по модулю 2

бычный

сумматор по модулю 2

В нимание!!!

У НЕГО В ЛЕКЦЯХ НЕ А В а X2

X1

(именно 2 и 1, не 1 и 2)

нимание!!!

У НЕГО В ЛЕКЦЯХ НЕ А В а X2

X1

(именно 2 и 1, не 1 и 2)

Вместо PO – просто P

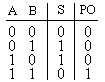

<- Таблица истинности полусумматора

< -

Так обозначают xor

-

Так обозначают xor

В полном двоичном сумматоре требуется учитывать перенос, поэтому требуются схемы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такой схемы, называемой полусумматором, приведена на рисунке выше.

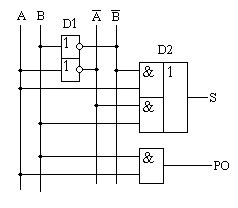

Сам сумматор:

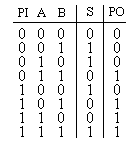

Схема полусумматора формирует перенос в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому она и называется полусумматором. Таблицу истинности полного двоичного одноразрядного сумматора можно получить из правил суммирования двоичных чисел. Она приведена на рисунке 7. В обозначении входов использовано следующее правило: в качестве входов использованы одноразрядные числа A и B; перенос обозначен буквой P; для обозначения входа переноса используется буква I (сокращение от английского слова input – вход); для обозначения выхода переноса используется буква O (сокращение от английского слова output – выход).

рисунок

7

рисунок

7

Системы обработки информации

(вычислительные системы)

П еречисленные

выше типовые задачи могут быть решены

и формализованы математическими и

логическими методами. В свою очередь

названные методы оперируют простейшими

операциями (арифметическими или

логическими), Обобщённая структурная

схема некоторой вычислительной системы

приведена на рис.В3.

еречисленные

выше типовые задачи могут быть решены

и формализованы математическими и

логическими методами. В свою очередь

названные методы оперируют простейшими

операциями (арифметическими или

логическими), Обобщённая структурная

схема некоторой вычислительной системы

приведена на рис.В3.

Обобщённая структурная схема вычислительной системы

Обрабатываемые данные предварительно через устройство вводаУвв поступают на запоминающее устройствоЗУ, где сохраняются на всё время обработки. В этом же ЗУ хранится и программа обработки поступающей информации.

Программа работы системы так же, как и «данные», хранятся в запоминающем устройстве в виде многоразрядных двоичных чисел, записанных в ячейки ЗУ по определённым адресам (адресам ячеек памяти). Двоичные числа, совокупность которых отображает программу обработки данных, структурированы на определённое число частей, каждая из которых имеет определённое назначение. В простейшем случае имеются следующие части: 1) код операции, которую надо выполнить с двумя двоичными числами, отображающими значения «данных» и называемыми «операндами»; 2) адрес первого операнда; 3) адрес второго операнда. Совокупность этих частей образует «команду».

Работа ЭВМ заключается в последовательном выполнении команд, заданных программой. Координирует работу всех блоков во времени и управляет ими управляющее устройствоУУ. А непосредственно логические и арифметические операции (действия) над операндами выполняет арифметико-логическое устройствоАЛУ, которое по сигналу от УУ «код операции» каждый раз настраивается на выполнение конкретной операции.

Устройство управления расшифровывает поступившую от ЗУ команду (рис. В3 «очередная команда»), код операции направляет на АЛУ и оно готовится к выполнению соответствующей операции. Затем формирует сигналы выборки из ЗУ операндов (см. сигнал «Адреса данных») и определяет адрес очередной команды, которую следует выполнить на следующем такте работы ЭВМ («Адрес очередной команды»). По сигналам от УУ из ЗУ считываются операнды, и АЛУ выполняет необходимые действия. При этом образуется промежуточный результат («Результат операции»), который также сохраняет ЗУ. В зависимости от результата выполнения операции может появиться необходимость изменения последовательности выполнения команд, либо прекратить обработку данных, либо вывести оператору сообщения об ошибках. Для этой цели с АЛУ на УУ поступает сигнал «Признак результата». Процесс обработки введённых данных (информации) продолжается до тех пор, пока не будет извлечена команда «Конец вычислений», либо оператор по своему усмотрению не остановит процесс обработки данных.

Полученный результат обработки также хранится в ЗУ и может быть выведен через устройство выводаУвывпо окончании процесса обработки либо в ходе процесса, если это предусмотрено программой.

Все перечисленные функциональные узлы выполняются в виде интегральных цифровых устройств.

Основными проблемами вычислительных систем являются, во-первых, повышение их производительности (быстродействия). И, во-вторых, обеспечение работы систем в реальном «масштабе» времени.

ШИФРАТОРЫ И КОДЕРЫ

Декодеры (дешифраторы) позволяют преобразовывать одни виды бинарных кодов в другие.

Десятичный дешифратор

Рассмотрим пример построения декодера из двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Сигнал с этих выводов можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру.Таблица истинности такого декодера:

Входы |

Выходы |

||||||||||||

8 |

4 |

2 |

1 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

Схема двоично-десятичного дешифратора