- •Системы автоматического управления (сау)

- •Сумматоры

- •Системы обработки информации

- •Обобщённая структурная схема вычислительной системы

- •Сравнительная оценка цифровых и аналоговых устройствмикроэлектронной техники

- •Достоинства технических средств цифровой техники

- •Мультиплексоры Демультиплексоры

- •Классификация микроэлектронных устройств.

- •XI равна 1только еслиAi и Bi равны.

- •Синхронные rs-триггеры.

- •Классификация интегральных схем (плис)

- •Комбинационные плис

- •Системы на кристале

- •Синхронные и асинхронные счётчики

- •Карты карно

- •Risc-процессоры

- •Системы счисления

- •Гарвардская архитектура

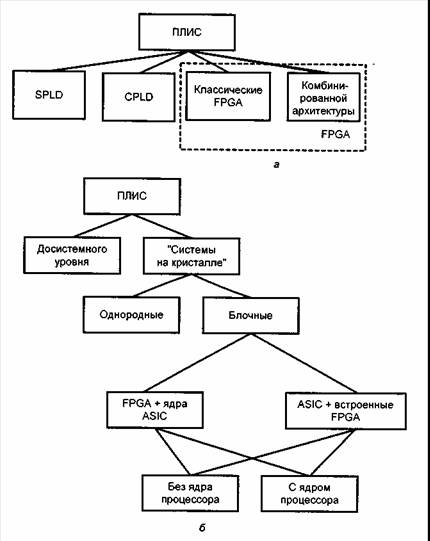

Классификация интегральных схем (плис)

Микросхемы, программируемые пользователями, открыли новую страницу в истории современной микроэлектроники и вычислительной техники. Они сделали БИС/СБИС, предназначенные для решения специализированных задач, стандартной продукцией электронной промышленности со всеми вытекающими из этого положительными следствиями: массовое производство, снижение стоимости микросхем, сроков разработки и выхода на рынок продукции на их основе. ПЛИС можно классифицировать по многим признакам, в первую очередь: - по уровню интеграции и связанной с ним логической сложности; - по архитектуре (типу функциональных блоков, характеру системы межсоединений); - по числу допустимых циклов программирования; - по типу памяти конфигурации («теневой»памяти ); - по степени зависимости задержек сигналов от путей их распространения; - по системным свойствам; - по схемотехнологии (КМОП, ТТЛШ и др.); - по однородности или гибридности (по признаку наличия или отсутствия в микросхеме областей с различными по методам проектирования схемами, такими как ПЛИС, БМК, схемы на стандартных ячейках). Все перечисленные признаки имеют значение и отображают ту или иную сторону возможных классификаций. Выделяя основные признаки и укрупняя их, рассмотрим классификацию по трем, в том числе двум комплексным, признакам: - по архитектуре; - по уровню интеграции и однородности/гибридности; - по числу допустимых циклов программирования и связанному с этим типу памяти конфигурации.

Рис.: Классификация ПЛИС (а – поархитектуре, б – по уровню интеграции)

Первый из классов — SPLD, SimpleProgrammableLogicDevices, т. е. простые программируемые логические устройства. По архитектуре эти ПЛИС делятся на подклассы программируемых логических матриц ПЛМ (PLA, ProgrammableLogicArrays) и программируемой матричной логики ПМЛ (PAL, ProgrammableArraysLogic, или GAL, GenericArrayLogic). Оба эти подкласса микросхем реализуют дизъюнктивные нормальные формы (ДНФ) переключательных функций, а их основными блоками являются две матрицы: матрица элементов Ии матрица элементов ИЛИ, включенные последовательно. Такова структурная модель ПЛМ и ПМЛ. Технически они могут быть выполнены и как последовательность двух матриц элементов ИЛИ-НЕ, но варианты с последовательностью матриц И-ИЛИ и с последовательностью матриц ИЛИ-НЕ — ИЛИ-НЕ функционально эквивалентны, т. к. второй вариант согласно правилу де Моргана тоже реализует ДНФ, но для инверсных значений переменных.

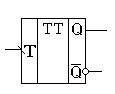

T-триггеры.

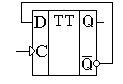

Т-триггер – это счетный триггер. У Т-триггера имеется только один вход. После поступления на этот вход импульса, состояние Т-триггера меняется на прямо противоположное. Счётным он называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние. Т-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D-триггеру. Использование двух триггеров позволяет избежать самовозбуждения схемы, так как счетные триггеры строятся при помощи схем с обратной связью Т-триггер можно синтезировать из любого двухступенчатого триггера. Рассмотрим пример синтеза Т-триггера из динамического D-триггера. Для того чтобы превратить D-триггер в счётный, необходимо ввести цепь обратной связи с инверсного выхода этого триггера на вход, как показано на рисунке 1.

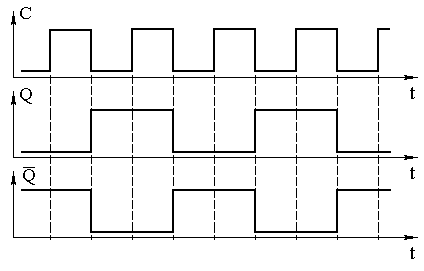

Временная диаграмма T-триггера приведена на рисунке 2.

При построении этой временной диаграммы был использован триггер, работающий по заднему фронту синхронизирующего сигнала.

Т-триггеры

используются при построении схем

различных счётчиков, поэтому в составе

БИС различного назначения обычно есть

готовые модули этих триггеров.

Условно-графическое обозначение

T-триггера приведено на рисунке 3.

Т-триггеры

используются при построении схем

различных счётчиков, поэтому в составе

БИС различного назначения обычно есть

готовые модули этих триггеров.

Условно-графическое обозначение

T-триггера приведено на рисунке 3.