- •2. Последовательный регистр

- •3. Сдвигающие регистры с параллельным вводом-выводом данных

- •4 Реверсивные сдвигающие регистры

- •5. Кольцевой сдвигающий регистр

- •6. Регистры хранения

- •Счетчики Основные теоретические положения

- •Двоичные счетчики

- •1. Суммирующий асинхронный двоичный счетчик

- •2. Вычитающий асинхронный счетчик

- •3. Счетчики по модулю n

- •4. Двоично-десятичные счетчики

- •5. Реверсивные двоичные счетчики

- •6. Синхронные счетчики

2. Вычитающий асинхронный счетчик

Двоичный вычитающий счетчик ведет отсчет от максимального значения до нуля, затем цикл повторяется.

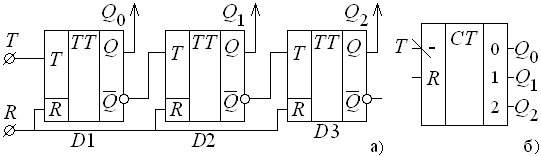

Функциональная схема данного счетчика представлена на рисунке 5.

Она содержит T-триггеры (выполнены по технологии MS). Схема отличается от суммирующего счетчика, изображенного на рис. 1, подключением T входов к инверсным выходам Q.

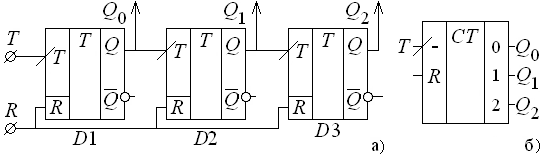

В вычитающем счетчике (рис. 6), в отличие от схемы на рисунке 3, T входы соединены с выходами Q.

Рис. 5 Трехразрядный асинхронный

вычитающий двоичный счетчик:

а – функциональная схема на MS-триггерах; б - обозначение

Рис. 6 Трехразрядный асинхронный вычитающий

двоичный счетчик:

а – функциональная схема на триггерах с динамическими входами; б - обозначение

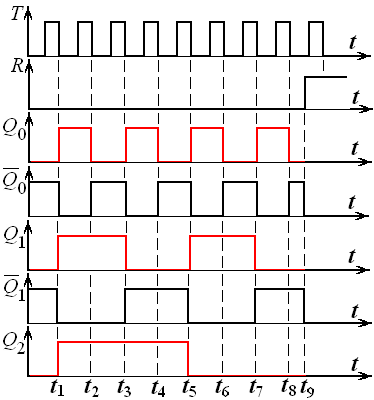

Временные диаграммы работы вычитающего счетчика (рис. 5) представлены на рис. 7.

Из них следует, что это устройство можно построить на основе суммирующего счетчика (рис. 1), выбрав в качестве выходов инверсные значения Q0, Q1, Q2.

Аналогичные преобразования можно сделать с суммирующим счетчиком, изображенным на рис. 3.

Рис. 7 Временные диаграммы работы асинхронного

трехразрядного вычитающего двоичного счетчика

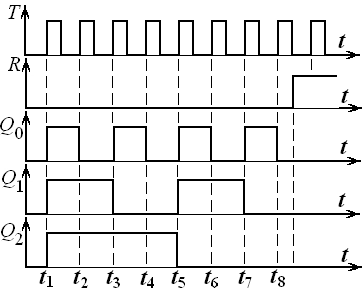

Временные диаграммы работы вычитающего счетчика (рис. 6) представлены на рис. 8.

В нем переключение происходит в динамическом режиме по переднему фронту входного сигнала.

Рис. 8 Временные диаграммы работы асинхронного трехразрядного вычитающего двоичного счетчика

с динамическим входом

Выходные сигналы трехразрядного вычитающего счетчика приведены в таблице 2.

Таблица состояний трехразрядного счетчика Таблица 2

№ набора |

Число импульсов T |

Сброс |

Выходы счетчика |

||

(десятичное число) |

R |

Q2 |

Q1 |

Q0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

2 |

1 |

0 |

1 |

1 |

1 |

3 |

2 |

0 |

1 |

1 |

0 |

4 |

3 |

0 |

1 |

0 |

1 |

5 |

4 |

0 |

1 |

0 |

0 |

6 |

5 |

0 |

0 |

1 |

1 |

7 |

6 |

0 |

0 |

1 |

0 |

8 |

7 |

0 |

0 |

0 |

1 |

9 |

8 |

0 |

0 |

0 |

0 |

10 |

Х |

1 |

0 |

0 |

0 |

3. Счетчики по модулю n

Данные устройства считают до числа n-1 и на следующем импульсе сбрасываются в ноль. Для уменьшения коэффициента KСЧ в качестве выхода счетчика используются выходы триггеров промежуточных каскадов. Например, для трехразрядного счетчика KСЧ=8, если взять выход второго триггера, то KСЧ= 4. За счет отказа от использования части триггеров, этот коэффициент изменяется от 2 до 7.

На основе всех трех триггеров, с помощью дополнительных элементов, можно получить: 22 < KСЧ <23.

В качестве примера приводится разработка суммирующего асинхронного счетчика с KСЧ= 5.

В этом устройстве, после формирования последнего числа из ряда целых чисел 0, 1,…, 4, осуществляется переход к 0 (а не к 5).

Следовательно, двоичные коды чисел 5, 6, 7 являются запрещенными и их появление должно привести к сбросу данных во всех разрядах счетчика (табл. 2).

Состояния выходов счетчика Таблица 2

Десятичное число |

Двоичное число |

||

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

2 |

0 |

1 |

0 |

3 |

0 |

1 |

1 |

4 |

1 |

0 |

0 |

5 |

1 |

0 |

1 |

6 |

1 |

1 |

0 |

7 |

1 |

1 |

1 |

Согласно табл. 2, запрещенные состояния выходов счетчика:

![]()

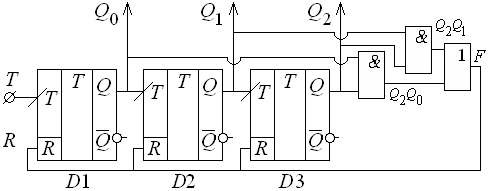

Схема счетчика представлена на рис. 9.

Рис. 9 Функциональная схема трехразрядного счетчика

с коэффициентом пересчета, равным пяти

В упрощенном варианте можно сбрасывать данные в разрядах триггеров только для набора, соответствующего числу 5.

Недостатком схемы является кратковременное появление запрещенного состояния перед сбросом. Поэтому данная схема применяется для управления индикаторами, где указанный недостаток не имеет принципиального значения.

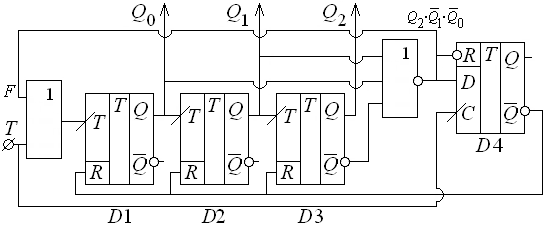

Схема счетчика, представленная на рис. 10, не имеет этого недостатка. В ней выявляется факт попадания в состояние, которое предшествует запрещенному состоянию (код 100). С приходом очередного входного сигнала происходит сброс данных.

Выявляемый набор:

![]()

В случае если F=1, снимается асинхронная приоритетная установка триггера D4 в ноль. Сам триггер подготавливается к записи единицы по входу D, что и произойдет по переднему фронту очередного импульса T. Сигнал F=1 на входе элемента 2ИЛИ препятствует поступлению импульсов на T вход счетчика.

При появлении единичного сигнала T, на инверсном выходе триггера D4 появляется логический ноль, который сбрасывает триггеры D1, D2, D3.

После этого F=0, триггер D4 по асинхронному входу R устанавливается в ноль.

Счетчик готов к продолжению работы.

Рис. 10 Функциональная схема трехразрядного счетчика

с коэффициентом пересчета, равным пяти

При выборе другого коэффициента пересчета, в схеме счетчика (рис. 10) изменится только логический элемент, реализующий функцию F.