- •2. Последовательный регистр

- •3. Сдвигающие регистры с параллельным вводом-выводом данных

- •4 Реверсивные сдвигающие регистры

- •5. Кольцевой сдвигающий регистр

- •6. Регистры хранения

- •Счетчики Основные теоретические положения

- •Двоичные счетчики

- •1. Суммирующий асинхронный двоичный счетчик

- •2. Вычитающий асинхронный счетчик

- •3. Счетчики по модулю n

- •4. Двоично-десятичные счетчики

- •5. Реверсивные двоичные счетчики

- •6. Синхронные счетчики

Двоичные счетчики

Двоичные счетчики выполняют счет входных импульсов в двоичной системе счисления. Число разрядов n двоичного счетчика, при заданном значении KСЧ, определяется из выражения:

![]()

Количество импульсов, подсчитанных счетчиком, определяется в любой момент времени из следующего уравнения:

где: 2i – вес i-го разряда; Q i – логическое значение на выходе триггера i-го разряда.

Данное выражение справедливо, если счет проводился от нулевого начального значения.

1. Суммирующий асинхронный двоичный счетчик

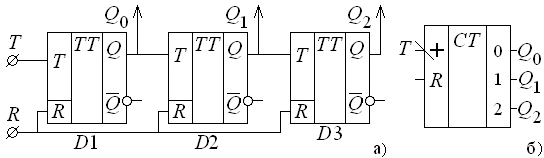

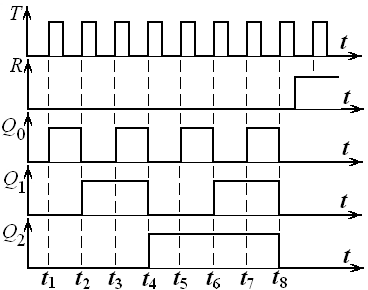

На рисунке 1 представлен асинхронный суммирующий счетчик, временные диаграммы его работы на рис. 2.

Подсчитываемые сигналы подаются на вход T.

По их заднему фронту происходит переключение T-триггеров, т.к. они относятся к MS-триггерам.

Для установки нулевых значений во всех разрядах служит вход R.

Рис. 1 Трехразрядный асинхронный суммирующий

двоичный счетчик:

а – функциональная схема на MS-триггерах;

б - обозначение

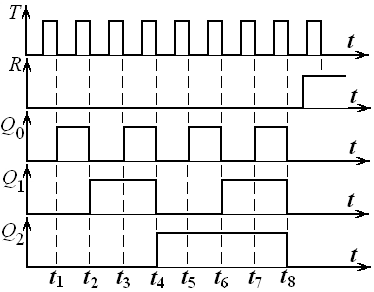

Рис. 2 Временные диаграммы работы асинхронного

трехразрядного суммирующего двоичного счетчика

В асинхронном счетчике триггеры переключаются общим тактовым сигналом T не одновременно.

Задержка переключения триггера объясняется конечным значением его быстродействия.

Оно составляет в среднем для различных типов микросхем 30…50 нс.

Для низкочастотных входных сигналов T задержкой можно пренебречь.

Если период входного сигнала составляет сотни наносекунд, то быстродействие следует учитывать, т.к. задержка переключения каждого триггера относительно входного сигнала счетчика включает сумму задержек всех предыдущих триггеров и уменьшает максимально возможную частоту работы устройства в целом.

Смещение моментов переключения триггеров является недостатком асинхронного метода переключения.

Счетчик может считать от нуля до семи (табл. 1, рис. 2). После поступления восьмого импульса T, он возвращается в исходное состояние.

Таблица состояний трехразрядного счетчика Таблица 1

№ набора |

Число импульсов T |

Сброс |

Выходы счетчика |

||

(десятичное число) |

R |

Q2 |

Q1 |

Q0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

2 |

1 |

0 |

0 |

0 |

1 |

3 |

2 |

0 |

0 |

1 |

0 |

4 |

3 |

0 |

0 |

1 |

1 |

5 |

4 |

0 |

1 |

0 |

0 |

6 |

5 |

0 |

1 |

0 |

1 |

7 |

6 |

0 |

1 |

1 |

0 |

8 |

7 |

0 |

1 |

1 |

1 |

9 |

8 |

0 |

0 |

0 |

0 |

10 |

Х |

1 |

0 |

0 |

0 |

Знаком «Х» в таблице обозначается, что любая величина переменной не оказывает влияния на результат.

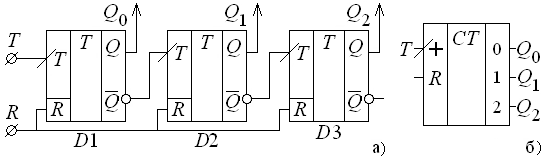

Если суммирующий счетчик состоит из триггеров с переключением по переднему фронту входного импульса (рис. 3), то для управления триггерами используются инверсные выходы Q, временные диаграммы его работы на рис. 4.

Рис. 3 Трехразрядный асинхронный суммирующий двоичный счетчик:

а – функциональная схема на триггерах с динамическими входами; б - обозначение

Достоинством асинхронных счетчиков является простота схемы.

Увеличение разрядности производится подключением необходимого числа триггеров.

К недостаткам можно отнести сравнительно низкое быстродействие, а также ее зависимость от числа разрядов. Из-за несовпадения моментов переключения триггеров, которые срабатывают по очереди, возникают кратковременные комбинации выходных сигналов, не соответствующие количеству подсчитанных импульсов.

Последний недостаток можно исключить, используя, например, счет в коде Грея.

При этом переключение происходит только в одном из разрядов.

Рис. 4 Временные диаграммы работы асинхронного

трехразрядного суммирующего двоичного счетчика

Для получения минимального времени переключения счетчика используется сигнал синхронизации, который обеспечивает одновременность срабатывания триггеров.