- •Лекция 12. Комбинационные цифровые устройства

- •12.1. Дешифраторы и шифраторы

- •12.1.1. Шифраторы

- •Каскадирование шифраторов применяется для увеличения разрядности входного кода (рис. 3).

- •12.1.2. Дешифраторы

- •Увеличение разрядности дешифратора

- •Семи сегментный дешифратор

- •Матричный индикатор

- •Индикаторы для диспетчерских щитов

- •12.2. Преобразователи кодов

- •12.3. Мультиплексоры и демультиплексоры

- •12.3.1. Мультиплексоры

- •Реализация логических функций на мультиплексорах

- •Увеличение разрядности мультиплексора

- •12.3.2. Демультиплексоры

- •Примеры использования демультиплексоров:

- •12.4. Сумматоры

- •Полусумматор

- •Полный сумматор

- •Вычитатель

- •Методы вычитания

Лекция 12. Комбинационные цифровые устройства

12.1. Дешифраторы и шифраторы.

12.2. Преобразователи кодов.

12.3. Мультиплексоры и демультиплексоры.

12.4. Сумматоры.

Логические устройства разделяют на два класса: комбинационные и последовательностные.

Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени.

Иначе устройство называют последовательностным или конечным автоматом (цифровым автоматом, автоматом с памятью). В последовательностных устройствах обязательно имеются элементы памяти.

Выходные сигналы последовательностных устройств определяются не только сигналами, имеющимися на входах в данный момент времени, но и состоянием элементов памяти.

Таким образом, реакция последовательностного устройства на определенные входные сигналы зависит от предыстории его работы.

12.1. Дешифраторы и шифраторы

Шифрирование это способ сжатия данных, дешифрирование – обратное преобразование. Условные обозначения дешифраторов и шифраторов DC и CD (decoder и coder соответственно).

12.1.1. Шифраторы

Шифратор – это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду.

Шифраторы (CD, coder) выполняют функцию, обратную функции дешифратора. При поступлении сигнала на один из входов шифратора на его выходах формируется код, соответствующий номеру этого входа.

Основное назначение шифратора – преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Шифраторы применяются для ввода десятичных данных с клавиатуры, преобразования чисел с фиксированной запятой в цифры с плавающей запятой, приоритетного обслуживания запросов на прерывание работы микропроцессора внешними устройствами, передачи информации по ограниченному числу линий связи (сжатие информации), в параллельных преобразователях аналогового сигнала в цифровой код.

Шифрирование это способ сжатия данных за счет преобразования m-разрядного унитарного (десятичного) кода в n-разрядный двоичный или двоично-десятичный код (m > n).

Полный шифратор (m – n) имеет m = 2n входов и n выходов, если m < 2n, то шифратор не полный. Также он может быть неприоритетным, если разрешена подача только одного активного сигнала или приоритетным, если допускается подача одновременно нескольких активных сигналов на входы.

Шифраторы, которые при одновременном нажатии нескольких клавиш вырабатывают код только старшей цифры, называют приоритетными-т.е. нажатие других клавиш должно игнорироваться.

Принцип работы полного неприоритетного шифратора (4 – 2) поясняется таблицей истинности (таблица 1).

Таблица истинности неприоритетного шифратора (4 – 2) Таблица 1

№ набора |

Информационные входы |

Выходы |

||||

X3 |

X2 |

X1 |

X0 |

F1 |

F0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

2 |

0 |

1 |

0 |

0 |

1 |

0 |

3 |

1 |

0 |

0 |

0 |

1 |

1 |

Карты Карно для минимизации схемы шифраторов обычно не используются вследствие сложности составления при большом количестве переменных.

Из таблицы (1) следует, что младший разряд F0 кода на выходе шифратора равен единице, когда на нечетных входах присутствует единица:

![]()

Старший разряд F1 кода на выходе шифратора равен единице, когда на входах X3, X2 присутствует единица:

![]()

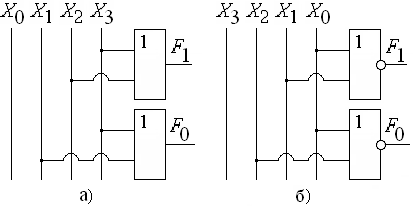

Следовательно, схема шифратора (4 – 2) может быть реализована с помощью двух элементов 2ИЛИ (рис. 1, а).

Рис. 1 Схемы неприоритетного шифратора (4 – 2)

на элементах 2ИЛИ (а), 2ИЛИ-НЕ (б)

Для инверсной записи (рис. 1, б):

![]()

![]()

Один из входных сигналов шифратора обязательно имеет единичное значение (таблица 1).

Если на входах X1, X2, X3 нулевые значения, это означает, что на входе X0 логическая единица, соответствующая набору 0, и этот вход к схеме может быть не подключен (рис. 1, а).

Аналогично для X3 в схеме шифратора на рис. 1, б. Схемы шифраторов на рисунке отличаются зеркальной перестановкой входов (в обоих случаях младший разряд X0, старший X3) и инвертированием выходных сигналов (рис.1, б).

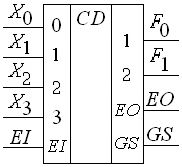

У шифраторов обычно имеются служебные входы и выходы:

- Разрешающий (стробирующий) вход EI (EN) для выбора времени срабатывания шифратора при условии EI =1, также для наращивания разрядности входного кода.

- Разрешающий выход EO (EN), определяет отсутствие сигналов на всех информационных выходах (EO = 1). Используется для увеличения разрядности путем подключения дополнительных шифраторов, условие подключения EO =1.

- Разрешающий выход GS (CS), указывает на наличие информационного сигнала хотя бы на одном входе, принимая значение GS = 1. Обеспечивает согласование работы шифратора и внешних устройств (микропроцессор). Может применяться в схеме наращивания разрядности шифратора для исключения ошибок преобразования кодов.

Одно из основных назначений шифратора – ввод данных в цифровые устройства с помощью клавиатуры. Шифраторы, которые при одновременном нажатии нескольких клавиш вырабатывают код только старшей цифры, называют приоритетными. Если эти шифраторы выявляют старшую (левую) единицу и формируют двоичный код соответствующего единице десятичного номера, то называются указателями старшей единицы (обозначение элемента HPR1/BIN).

В таблице истинности указателя старшей единицы (таблица 2) символом «Х» обозначены значения входных переменных, которые не важны для устройства и могут быть равны 0 или 1. Интерес представляют единицы в старшем разряде соответствующего набора.

Символом « – » обозначены значения переменных, которые не поступают в шифратор, т.к. на разрешающем входе EI сигнал логического нуля, на выходе F1F0 = 00.

Пример: если нажата клавиша старшего разряда Х3 (набор 5), что соответствует кодам 310 = 112, нажатие других клавиш должно игнорироваться.

Таблица истинности указателя старшей единицы (4 – 2) Таблица 2 |

|||||||||

№ набора |

Служебные |

Информационные |

|||||||

вход |

выходы |

Входы |

Выходы |

||||||

EI |

GS |

EO |

X3 |

X2 |

X1 |

X0 |

F1 |

F0 |

|

0 |

0 |

0 |

0 |

– |

– |

– |

– |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

2 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

3 |

1 |

1 |

0 |

0 |

0 |

1 |

Х |

0 |

1 |

4 |

1 |

1 |

0 |

0 |

1 |

Х |

Х |

1 |

0 |

5 |

1 |

1 |

0 |

1 |

Х |

Х |

Х |

1 |

1 |

Условное графическое обозначение полного приоритетного шифратора на рис. 2.

Рис. 2 Обозначение полного приоритетного

шифратора (4 – 2)