- •Топологическое проектирование систем на печатных платах средствами Expedition pcb («Mentor Graphics») Учебное пособие

- •Часть 3

- •1. Введение

- •2. Library Manager. Работа с центральной библиотекой проектов

- •1.Назначение программы. Основные термины и понятия

- •2.Общие рекомендации по созданию посадочных мест элементов

- •3.Создание центральной библиотеки проекта (Central Library)

- •4.Формирование структуры библиотеки (Partition Editor)

- •5.Создание контактных площадок (Padstack Editor)

- •6.Создание посадочных мест элементов (Cell Editor)

- •7.Создание элементов (Part Editor). Назначение свопирования выводов/вентилей

- •8.Взаимообмен с другими центральными библиотеками (Library Services)

- •3. Expedition pcb. Проектирование печатных плат

- •9.Назначение и интерфейс программы. Основные режимы работы

- •10.Управление экраном

- •11.Создание собственных видовых схем

- •12.Создание нового проекта печатной платы. Основные настройки

- •13.Задание геометрии печатной платы, работа с контурами

- •14.Размещение элементов и свопирование

- •15.Трассировка межсоединений

- •16.Работа с экранными областями

- •17.Проверка соответствия топологии технологическим ограничениям

- •18.Генерация слоев шелкографии

- •19.Генерация данных для изготовления печатной платы

- •20.Генерация данных для конструкторской документации

- •21.Получение информации о проекте в трехмерном изображении

- •4. Обзор основных возможностей редактора Expedition pcb по трассировке критических (в т.Ч. Высокочастотных) цепей

- •5. FabLink xe. Панелизация печатных плат

- •22.Назначение программы

- •23.Типы многоплатных панелей

- •24.Трафареты для нанесения паяльной пасты

- •25.Работа с программой FabLink xe

- •6. Контрольные тестовые вопросы с указанием правильных ответов

- •7. Контрольные тестовые вопросы без указания ответов

- •8. Список литературы

- •9. Приложение

12.Создание нового проекта печатной платы. Основные настройки

В редакторе DxDesigner на этапе создания схемы электрической принципиальной закладываются предпосылки для перехода к проектированию печатной платы:

задаются основные параметры будущего проекта печатной платы – привязка к центральной библиотеке (Central Library), маршрут проектирования (Expedition PCB), шаблон или прототип (Template) для 2-х, 4-х, или 6-ти…слойной платы, возможность прямой и обратной аннотаций (Forward / Back Annotation) и др.;

проводится упаковка (Package CDB) электрической схемы;

устраняются возможные ошибки (Errors) и анализируются возможные предупреждения (Warnings).

Проект собственно печатной платы обычно формируется в подкаталоге \PCB основного проекта под именем pcb.pcb.

Для перехода в топологический редактор Expedition PCB используются команды схемотехнического редактора DxDesigner Tools >> Launch Expedition или Tools >> Forward to Expedition. Система создает новый проект печатной платы и автоматически открывает окно редактора Expedition PCB с назначенным шаблоном (прототипом).

Перед началом работы, при необходимости, подстраивают выставленные в шаблоне параметры и настройки под новый проект.

В редакторе Expedition PCB основные команды установки находятся в основном меню Setup.

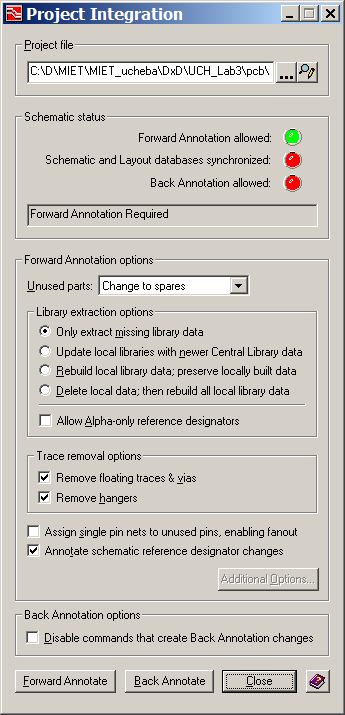

Перенос данных электрической схемы в проект печатной платы (Forward Annotation).

П![]() еренос

данных электрической схемы в проект

печатной платы называется процедурой

прямой аннотации – Forward

Annotation.

Для ее проведения необходимо выполнить

команду основного меню Setup

>> Project

Integration…

(иконка

) >>

кнопка Forward

Annotate

(см. рис. 3.5).

еренос

данных электрической схемы в проект

печатной платы называется процедурой

прямой аннотации – Forward

Annotation.

Для ее проведения необходимо выполнить

команду основного меню Setup

>> Project

Integration…

(иконка

) >>

кнопка Forward

Annotate

(см. рис. 3.5).

Обратная процедура – Back Annotation, т.е. передача в назад схему результатов свопирования и переименовывания позиционных обозначений элементов, выполняется автоматически каждый раз при сохранении проекта печатной платы, но может проводиться принудительно той же командой, но с кнопкой Back Annotate.

К оманды Forward и Back Annotation вызываются также из основного меню ECO или иконками , соответственно.

Рис. 3.5. Интеграция проектов электрической схемы и печатной платы.

При успешном прохождении процедуры прямой аннотации все три кружка в поле Schematic status окрашиваются в зеленый цвет.

О![]() тчет

о произведенных действиях, а также

предупреждениях редактора (Warnings)

и найденных ошибках (Errors)

формируется в виде файла ForwardAnnotation.txt,

находящегося

в папке

…\pcb\LogFiles\.

Его рекомендуется просмотреть встроенным

просмотровщиком с помощью команды

основного меню File

>> File

Viewer…

(или соответствующей иконки ).

тчет

о произведенных действиях, а также

предупреждениях редактора (Warnings)

и найденных ошибках (Errors)

формируется в виде файла ForwardAnnotation.txt,

находящегося

в папке

…\pcb\LogFiles\.

Его рекомендуется просмотреть встроенным

просмотровщиком с помощью команды

основного меню File

>> File

Viewer…

(или соответствующей иконки ).

П ри

прямой аннотации в проекте печатной

платы формируется локальная

библиотека элементов,

состоящая из Part

Numbers,

Cells

и Padstacks.

Дальнейшие изменения этих составных

частей в центральной библиотеке проекта

(Central

Library)

должны переноситься в проект платы

командой Project

Integration

с выставлением соответствующих опций

или командой Setup

>> Library

Services…

.

ри

прямой аннотации в проекте печатной

платы формируется локальная

библиотека элементов,

состоящая из Part

Numbers,

Cells

и Padstacks.

Дальнейшие изменения этих составных

частей в центральной библиотеке проекта

(Central

Library)

должны переноситься в проект платы

командой Project

Integration

с выставлением соответствующих опций

или командой Setup

>> Library

Services…

.

Соответствие этих двух библиотек можно проверять командой основного меню Analysis >> Verify Local to Central Library… .

Назначение топологических параметров.

Назначение топологических параметров, таких как система единиц, ширины и зазоры проводников, переходные отверстия и пр., производится в редакторе электрических ограничений CES (Constraint Editor System), доступном как из схемотехнического (DxDesigner), так и из топологического (Expedition PCB) редакторов. Рекомендуется задавать топологические параметры автору электрической схемы совместно с конструктором-топологом.

Редактор электрических ограничений CES (см. рис. 3.6) открывается командами:

– из схемотехнического редактора DxDesigner: Tools >> Setup Constraints ;

– из топологического редактора Expedition PCB: Setup >> Constraints… .

Рис. 3.6. Редактор электрических ограничений (CES). Закладка Trace & Via Properties.

Выбор системы единиц проекта печатной платы.

Для задания системы единиц печатной платы необходимо командой редактора CES Setup >> Options... >> Units >> Display units выбрать в строке Units, столбце Leaner метрические (мм) или дюймовые (in, th, …) единицы, а также установить отображаемое количество знаков после запятой (столбец Precision). Для метрической системы рекомендуется выставлять точность не менее 3-х знаков, чтобы, например, различать значения 0,25 мм и 0,254 мм.

Назначение ширин проводников (Traces) и переходных отверстий (Via).

Назначение ширины трассируемых проводников и переходных отверстий производится в редакторе CES на закладке Trace & Via Properties в столбцах Trace Width и Via Assignments соответственно. В каждом печатном слое для ширины трасс необходимо задать три значения – минимальная ширина (Minimum), нормальная (Tipical) и максимальная (Expansion). При автоматической трассировке программа использует значение Tipical, а в узких и свободных местах – Minimum и Expansion соответственно. Изменение величин производится простым редактированием содержимого клеток основной таблицы. Параметры, назначенные в схеме Scheme (Master) относятся ко всей поверхности печатной платы.

Для упрощения процедуры ввода в таблицу одинаковых значений достаточно выделить одну из клеток, ввести требуемую ширину, а потом, растянуть выделенную рамку клетки от правого нижнего угла (курсор принимает форму перекрестия) на другие клетки по горизонтали или по вертикали. Во всех охваченных таким образом клетках значения станут равными введенной ширине. Данная процедура распространяется и на другие закладки редактора CES.

Требуемые переходные отверстия необходимо предварительно перенести из центральной библиотеки в проект печатной платы командой редактора Expedition PCB Setup >> Library Services... >> Закладка Padstacks.

Значение переходного отверстия по умолчанию (Default) можно переназначить командой редактора Expedition PCB Setup >> Setup Parameters… >> Закладка Via Definitions.

Назначение зазоров (Clearances).

Назначение зазоров производится в редакторе CES на закладке Clearances (см. рис. 3.7). Редактор регламентирует подробную детализацию зазоров между элементами печати – проводниками (Trace), контактными площадками (Pad и SMD Pad), переходными отверстиями (Via), областями сплошной металлизации (Plane) и пр. Изменение величин производится также простым редактированием содержимого клеток основной таблицы. Параметры, назначенные в схеме Scheme (Master) относятся ко всей поверхности печатной платы.

Зазоры для других составляющих печатной платы (корпусов элементов – Placement Outline или Package, монтажных отверстий – Mounting Hole, краев платы – Board Edge, внутренних пазов – Contour и др.) задаются в раскрывающихся окнах команд-иконок General Clearances и Assign Package Type Clearances.

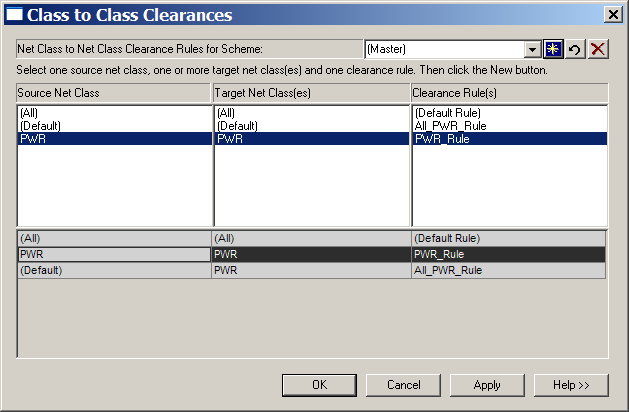

Команда-иконка Class to Class Clearance Rule служит для определения зазоров внутри и между различными классами цепей.

Рис. 3.7. Редактор электрических ограничений CES. Закладка Clearances.

Создание классов цепей (Net Classes).

Классы цепей (Net Classes) позволяют задавать разные топологические ограничения для конкретных цепей. Электрическая схема может включать цепи, к которым предъявляются особые требования по ширинам и зазорам. Например, цепи питания и земли обычно более сильноточные по сравнению с сигнальными цепями и, соответственно, печатные проводники для них должны быть шире. Отдельные цепи бывают чувствительны к помехам и требуют большего зазора до ближайших других цепей. Для задания такого рода отличий и введено понятие классов цепей. Любая цепь может относиться только к одному из классов.

Для создания нового класса и назначения в него цепей необходимо (рассмотрен один из вариантов):

в редакторе CES в окне обзора CES встать на класс, предлагаемый по умолчанию Net Classes – (Default);

вызвать с помощью правой клавиши мышки выпадающее меню и выбрать команду Copy;

присвоить новому классу цепей интуитивно понятное название, используя команду выпадающего меню Rename;

в созданной копии на закладке Trace & Via Properties изменить ширины проводников и назначения переходных отверстий на требуемые;

не уходя с закладки Trace & Via Properties, провести назначение цепей в новый класс, используя команду выпадающего меню Assign Nets…, или соответствующую иконку, или команду основного меню Edit >> Assign Nets to Classes… .

Окно обзора CES открывается командой Window >> Project Window.

Назначение зазоров внутри и между классами цепей (Net Classes Clearances).

В случае, когда внутри нового класса цепей требуются собственные зазоры, необходимо (рассмотрен один из вариантов):

создать новое правило (Rule):

перейти на закладку Clearances;

в окне обзора CES на схеме (Master) встать на правило, предлагаемое по умолчанию Clearances – (Default Rule) ;

вызвать с помощью правой клавиши мышки выпадающее меню и выбрать команду New;

присвоить новому правилу интуитивно понятное название, используя команду выпадающего меню Rename;

в созданном правиле изменить зазоры на требуемые;

применить новое правило к выбранному классу цепей (см. рис. 3.8):

командой-иконкой Class to Class Clearance Rule открыть окно назначения;

на полях Sourse Net Class, Target Net Class(es) и Clearance Rule(s) выбрать требуемый класс и правило зазоров для него;

з апомнить новое правило командой-иконкой Create new rule ( ), при этом новое правило появляется в нижней части окна;

сохранить назначение кнопкой OK или Apply.

![]() Для

удаления созданного правила зазоров

необходимо встать на него в нижней части

окна и нажать команду-иконку Delete

( ).

Для

удаления созданного правила зазоров

необходимо встать на него в нижней части

окна и нажать команду-иконку Delete

( ).

Рис. 3.8. Назначение зазоров (Clearance Rule) внутри и между классами цепей.

Назначение правила зазоров между классами цепей производится аналогично вышеописанному. При этом, а в полях Sourse Net Class, Target Net Class(es) и Clearance Rule(s) выбираются требуемые классы цепей и правило зазоров. Предварительно, при необходимости, такое правило создается.

Задание особых технологических ограничений в локальных зонах печатной платы (Schemes).

Помимо классов цепей редактор CES позволяет создавать схемы (Schemes), которые предназначены для назначения иных (т.е. отличающихся от основных) технологических ограничений (ширин проводников, зазоров, типов переходных отверстий), распространяющихся на ограниченные зоны печатной платы.

Необходимость таких зон часто диктуется применяемой в электрической схеме элементной базой. Например, более жестких ограничений, как правило, требует трассировка многовыводных микросхем в корпусах типа BGA (выводы реализованы в виде массива шариков на нижней стороне подложки). А распространение этих ограничений на всю площадь платы может быть неоправданным, т.к. приводит к ухудшению электрических характеристик (например, повышается омическое сопротивление цепи) и снижению технологичности изготовления печатной платы.

Для создания новой схемы необходимо (рассмотрен один из вариантов):

в редакторе CES в окне обзора CES встать на схему (Master);

вызвать с помощью правой клавиши мышки выпадающее меню и выбрать команду Copy;

присвоить новой схеме интуитивно понятное название, используя команду выпадающего меню Rename;

в созданной схеме на закладках Trace & Via Properties и Clearances изменить ширины проводников, переходные отверстия и зазоры на требуемые.

В процессе проектирования печатной платы зоны со специфическими ограничениями рисуются в виде контуров Rule Area (см. раздел 3.5), в свойствах (Properties) которых указывается имя созданной схемы (Name). При пересечении проводниками границы контура технологические ограничения трассировки автоматически изменяются.

Задание структуры печатной платы (Layer Stackup).

Структура печатной платы по слоям (Layer Stackup) задается, как правило, в проектах с высокоскоростными цепями с заданным волновым сопротивлением. Параметры структуры платы используются для расчета ширин и зазоров таких цепей (с помощью встроенного калькулятора), а также в программах моделирования.

Структура печатной платы может быть описана или в редакторе CES (командой меню Edit >> Stackup… ), или в редакторе Expedition PCB (командой основного меню Setup >> Setup Parameters… >> закладка Layer Stackup ).

Задание экранных слоев (Plane).

Назначение слоев печатной платы в качестве экранных рассматривается ниже, в разделе 3.8 (Работа с экранными областями).

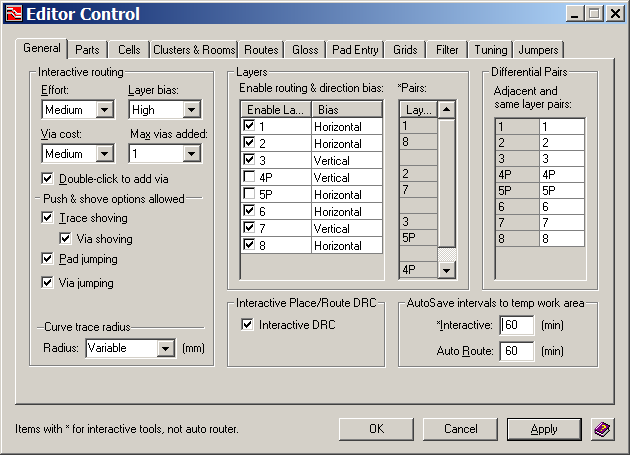

Настройки редактора Editor Control.

Н екоторые основные настройки устанавливаются в окне редактора Editor Control (см. рис. 3.9), открываемом в редакторе Expedition PCB командой основного меню Setup >> Editor Control … или соответствующей иконкой ( ).

На закладке General выставляются:

опции интерактивной трассировки, в частности, режима раздвигания ранее проложенных трасс и переходных отверстий при прокладке следующей трассы;

назначение слоев, участвующих в трассировке, и предпочтительные направления прокладки трасс на них при автотрассировке;

парность слоев при добавлении в трассу переходного отверстия;

выбор варианта прокладки дифференциальных пар (в одном слое рядом или в смежных слоях один проводник под другим).

На закладке Parts выставляются опции режима размещения элементов, в т.ч. запрет (или разрешение) нарушения допустимых зазоров между элементами, параметры привязки к сетке размещения, параметры выравнивания и пр.

На закладке Cells можно, при необходимости, регламентировать ориентацию на плате одинаковых корпусов (посадочных мест), что впоследствии повышает производительность монтажа элементов.

На закладке Routes выставляются опции прокладки трасс, в частности, разрешение (запрет) трассирования под углом 45°, запрет (или разрешение) закольцовки трасс (Prevent loops) и пр.; параметры и опции размещения переходных отверстий, дифференциальных пар, проводников (в части применения минимальной и максимальной ширин) и др.

Рис. 3.9. Редактор Editor Control.

На закладке Pad Entry можно, при необходимости, регламентировать подход проводников к контактным площадкам.

На закладке Grids назначаются сетки привязки для режимов размещения элементов (Placement grid), трассировки (Route grid и Via grid) и рисования (Drawing grid).

На закладке Filter можно временно исключать отдельные цепи (Nets) из процесса трассировки, а также отключать их “резиновые” связи (Netlines). Это полезно, например, при размещении элементов, когда многоточечные цепи (цепи питания и земли) затеняют общую картину связей других цепей.