- •46. Що таке сегментування пам'яті? Як сегментування пам'яті організовано в процесорі Intel 80286? 58

- •47. Що таке сегментування пам'яті? Як сегментування пам'яті організовано в процесорі Intel 80386? 59

- •Опишіть мікропроцесорну систему як частинний випадок електронної системи.

- •В чому переваги та недоліки традиційної цифрової системи (системи на “жорсткій логіці”) порівняно з універсальною (програмованою) системою?

- •В чому переваги та недоліки універсальної (програмованої) цифрової системи порівняно з традиційною системою (системою на “жорсткій логіці”)?

- •4. Опишіть властивості процесора, як головного вузла універсальної (програмованої) цифрової системи.

- •5. Що таке класична структура зв'язків у лектроннихсистемах? в чому її переваги та недоліки порівняно із шинною структурою зв'язків?

- •6. Що таке шинна структура зв'язків у електронних системах? в чому її переваги та недоліки порівняно із класичною структурою зв'язків?

- •7. Що таке програмний обмін інформацією і де він використовується?

- •8. Що таке обмін інформацією з використанням переривань і де

- •9. Що таке режим прямого доступу до пам'яті і де він використовується?

- •10. Які архітектури мікропроцесорних систем ви знаєте? в чому переваги та недоліки прінстонської архітектури порівняно із гарвардською?

- •11. Які архітектури мікропроцесорних систем ви знаєте? в чому переваги та недоліки гарвардської архітектури порівняно із прінстонською?

- •16. Як здійснюється обмін інформацією в мікропроцесорних системах? Що таке цикли обміну інформацією?

- •17. Що таке цикли обміну інформацією? Які цикли обміну інформацією ви знаєте? Охарактеризуйте їх.

- •18. Що таке системна магістраль і з чого вона складається?

- •19. Які шини входять до складу системної магістралі? Охарактеризуйте шину даних.

- •20. Які шини входять до складу системної магістралі? Охарактеризуйте шину адреси.

- •21. Які шини входять до складу системної магістралі? Охарактеризуйте шину керування. Що таке строби обміну?

- •22. Синхронний та асинхронний обмін інформацією. Їхні переваги та недоліки.

- •23. Детально охарактеризуйте цикл читання програмного обміну на магістралі q-bus.

- •24. Детально охарактеризуйте цикл запису програмного обміну на магістралі q-bus.

- •25. Детально охарактеризуйте цикл “читання-модифікація-запис” програмного обміну на магістралі q-bus.

- •26. Детально охарактеризуйте цикл читання програмного обміну на магістралі isa.

- •27. Детально охарактеризуйте цикл запису програмного обміну на магістралі isa.

- •28. Детально охарактеризуйте цикли обміну за перериваннями на магістралі q-bus.

- •29. Детально охарактеризуйте цикли обміну за перериваннями на магістралі isa.

- •30. Детально охарактеризуйте цикли обміну в режимі прямого доступу до пам'яті на магістралі q-bus.

- •31. Детально охарактеризуйте цикли обміну в режимі прямого доступу до пам’яті на магістралі isa

- •32. Які чинники впливають на проходження сигналу по магістралі?

- •33. Процесор, як пристрій системної магістралі. Які функції він виконує?

- •34. Яку роль в процесорі відіграють схема керування вибіркою команд та арифметико-логічний пристрій?

- •35. Детально охарактеризуйте регістри мікропроцесора. Які функції вони виконують?

- •36. Пам'ять, як пристрій системної магістралі. Які функції вона виконує? Охарактеризуйте функції стеку.

- •37. Пам'ять, як пристрій системної магістралі. Які функції вона виконує? Охарактеризуйте функції таблиці векторів переривань.

- •38. Пам'ять, як пристрій системної магістралі. Які функції вона виконує? Охарактеризуйте функції пам'яті програми початкового запуску та пам'яті пристроїв, під'єднаних до системної шини.

- •39. Пристрої вводу-виводу, як пристрої системної магістралі. Які функції вони виконують?

- •Пристрої вводу-виводу, як пристрої системної магістралі. Охарактеризуйте функції пристроїв інтерфейсу користувача та пристроїв тривалого зберігання інформації.

- •Пристрої вводу-виводу, як пристрої системної магістралі. Охарактеризуйте функції таймерних пристроїв.

- •Які методи адресації операндів ви знаєте? Детально опишіть безпосередню та пряму адресацію.

- •Які методи адресації операндів ви знаєте? Детально опишіть регістрову та непряму адресацію.

- •Які методи адресації операндів ви знаєте? Детально опишіть автоінкрементну та автодекрементну адресацію. Де вони використовуються?

- •Що таке сегментування пам'яті? Як сегментування пам'яті організовано в процесорі Intel 8086?

- •Що таке сегментування пам'яті? Як сегментування пам'яті організовано в процесорі Intel 80286?

- •Що таке сегментування пам'яті? Як сегментування пам'яті організовано в процесорі Intel 80386?

- •Дайте детальну характеристику регістрам процесора.

- •50. Що таке система команд процесора? Із чого вона складається? Детально охарактеризуйте арифметичні команди.

- •51. Що таке система команд процесора? Із чого вона складається? Детально охарактеризуйте логічні команди.

- •52. Що таке система команд процесора? Із чого вона складається? Детально охарактеризуйте команди переходів.

- •53. Які класи мікроконтролерів ви знаєте? Які ознаки притаманні сучасним 8-розрядним мікроконтролерам?

- •54.Які класи мікроконтролерів ви знаєте? Детально опишіть структуру процесорного ядра мікроконтролера.

- •55.Які класи мікроконтролерів ви знаєте? Детально опишіть пам'ять програм та пам'ять даних мікроконтролера.

- •56.Які класи мікроконтролерів ви знаєте? Детально охарактеризуйте регістри, стек та зовнішню пам'ять мікроконтролера.

- •57. Як організовано взаємодію мікроконтролера із зовнішнім середовищем? Детально опишіть функції портів вводу/виводу.

- •58.Як організовано взаємодію мікроконтролера із зовнішнім середовищем?Детально опишіть функції таймерів.

- •59.Як організовано взаємодію мікроконтролера із зовнішнім середовищем?Детально опишіть ф-ію процесорів подій.

- •60. Як досягаєтьсямінімізаціяенергоспоживанняу системах на базімікроконтролерів?

- •61. Детально охарактеризуйте тактовігенераторимікроконтролера.

- •62. Якіапаратнізасобизабезпеченнянадійності систем на базімікроконтролеріввизнаєте? Детально опишітьфункціїсхемиформування сигналу скидання.

- •63. Якіапаратнізасобизабезпеченнянадійності систем на базімікроконтролеріввизнаєте? Детально опишітьфункції блоку детектуваннязниженнянапругиживлення та сторожового таймера.

- •64. Які додаткові модулі мікроконтролера ви знаєте? Детально охарактеризуйте модулі послідовного вводу/виводу.

- •65. Які додаткові модулі мікроконтролера ви знаєте? Детально охарактеризуйте модулі аналогового вводу/виводу.

Що таке сегментування пам'яті? Як сегментування пам'яті організовано в процесорі Intel 8086?

Сегментная адресация памяти — схема логической адресации памяти компьютера в архитектуре x86. Линейный адрес конкретной ячейки памяти, который в некоторых режимах работы процессора будет совпадать с физическим адресом, делится на две части: сегмент и смещение. Сегментом называется условно выделенная область адресного пространства определённого размера, а смещением — адрес ячейки памяти относительно начала сегмента. Базой сегмента называется линейный адрес (адрес относительно всего объёма памяти), который указывает на начало сегмента в адресном пространстве. В результате получается сегментный (логический) адрес, который соответствует линейному адресу база сегмента+смещение и который выставляется процессором на шину адреса.

Селектором называется число (в x86 — 16-битное), однозначно определяющее сегмент. Селектор загружается в сегментные регистры.

Центральный процессор 8086 имеет четыре 16-битных регистра общего назначения AX, BX, CX, DX, четыре регистра-указателя SI, DI, BP и SP, четыре регистра сегментов CS, DS, ES, SS, один 16-битовый регистр флагов FLAGS и указатель программ IP

16-битная x86-архитектура, благодаря наличию четырех сегментных регистров, позволяет одновременно иметь доступ к четырем сегментам памяти. Назначение сегментных регистров:

DS (data segment) — сегмент данных;

CS (code segment) — сегмент кода;

SS (stack segment) — сегмент стека;

ES (extra segment) — дополнительный сегмент.

Логический адрес на такой платформе принято записывать в виде сегмент:смещение, где сегмент и смещение задаются в шестнадцатеричной системе счисления. В реальном режиме для вычисления физического адреса байта памяти происходит сдвиг влево на 4 разряда значения соответствующего сегментного регистра, а затем добавляется смещение.

Например, логический адрес 7522:F139 дает 20-битный физический адрес:

75220 + F139 = 84359

Максимальный объем физ. Памяти для 8086 – 1Мб

Що таке сегментування пам'яті? Як сегментування пам'яті організовано в процесорі Intel 80286?

Программная модель процессора 80286 включает 14 регистров ЦП 8086, пять новых регистров:

GDTR - 40-разрядный регистр определяет размер и положение глобальной дескрипторной таблицы;

LDTR - 16-разрядный регистр определяет базовый адрес локальной дескрипторной таблицы;

IDTR - 40-разрядный регистр определяет начало и размер таблицы векторов прерываний;

MSW - слово состояния программы (, если флаг PE = 1 в MSW, то процессор переключается в защищенный режим).;

TR - 16-разрядный регистр содержит селектор сегмента состояния задачи, используется для многозадачности,

и шесть программно недоступных регистров, связанных с CS, DS, ES, SS, GDTR, IDTR.

С появлением Intel-286 впервые стали говорить о различных режимах работы. Было реализовано два режима функционирования: режим реального адреса (режим эмуляции 8086) и защищенный режим, в котором используются все возможности МП. В последующих поколениях МП этого семейства защищенный режим становится основным режимом работы.

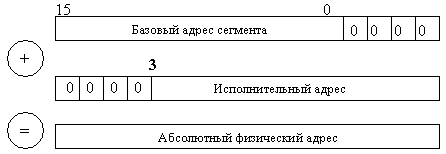

Формирование линейного адреса без участия селекторов

В режиме реального адреса используется упрощенная схема формирования линейного адреса.

В этом случае базовый адрес сегмента берется из сегментного регистра. Значение в сегментном регистре представляет собой биты 4-19 базового адреса сегмента. Действительный физический адрес получается умножением на 16 базового адреса сегмента (рис. 2.2). Предел для всех сегментов одинаков. В режиме реального адреса предел сегмента - 64 Кбайт.

Формирование линейного адреса в защищенном режиме

Значения, помещаемые в сегментные регистры, называются селекторами. Селектор содержит индекс дескриптора, определяющий номер записи в дескрипторной таблице, бит TI, указывающий, к какой дескрипторной таблице производится обращение LDT (TI = 1) или GDT (TI = 0), а также запрашиваемые права доступа к сегменту – RPL

По указанному в селекторе номеру записи в соответствующей (бит TI селектора) дескрипторной таблице определяется дескриптор сегмента.

Дескриптор - это 8-байтная единица описательной информации, распознаваемая устройством управления памятью в защищенном режиме, хранящаяся в дескрипторной таблице.

Дескриптор сегмента содержит базовый адрес описываемого сегмента, предел (размер) сегмента и права доступа к сегменту. В защищенном режиме сегменты могут начинаться с любого линейного адреса.

Для определения физического адреса базовый адрес сегмента суммируется со смещением.

Существуют две обязательных дескрипторных таблицы - глобальная (GDT) и дескрипторная таблица прерывания (IDT), - а также множество (до 8192) локальных дескрипторных таблиц (LDT), из которых в одинединый момент времени процессору доступна только одна. Расположение дескрипторных таблиц определяется регистрами процессора GDTR, IDTR, LDTR.

Максимальный объем физ. Памяти для 8086 – 16Мб