- •Общая организация микропроцессорных систем.

- •Адресация операндов при выполнении программ.

- •Структурная схема микроЭвм

- •Структурная схема процессора.

- •Регистр стека

- •Команды процессора.

- •3.Команды обращения к подпрограммам.

- •5.Команды ввода/вывода. Эта группа команд весьма разнообразна и очень существенно зависит от архитектуры конкретной эвм. В учебных целях рассматривается команда вывода output и команда ввода input.

- •Способы адресации

- •Структура команд.

- •Виды адресаций pdp-11

- •Архитектура микропроцессоров intel.

- •Общие сведения о микропроцессоре Intel (16-разрядный)

- •Сегменты и смещения.

- •Регистры сегментов

- •Регистры указателей индексов

- •Указатель команд

- •Режим адресации

- •Регистровая и непосредственная адресация

- •Режимы адресации памяти

- •Прямая адресация

- •Косвенная регистровая адресация

- •Адресация по базе

- •Прямая адресация с индексированием

- •Смещение dispH/dispL

- •Шинная организация эвм

- •Эволюция шинной организации микропроцессорных систем.

- •3) Применение конвертеров системной шины

- •Применение кэш-памяти.

- •Передача информации по шинам микро эвм

- •Стробирование сигналов на шинах данных.

- •Передача данных по шине по методу «запрос-ответ»

- •Способ передачи данных с внешней синхронизацией.

- •Организация ввода/вывода микропроцессорных систем.

- •Адресация внешнего устройства.

- •Классификация методов ввода/вывода.

- •Системный интерфейс микропроцессора Intel

- •Локальный интерфейс Intel 80-386

- •Модель функционирования локального интерфейса микропроцессора Intel 80386

- •Подсистема прерываний

- •Использование контроллеров прерывания для повышения быстродействия микропроцессорной системы.

- •Программирование контроллеров прерывания.

- •Организация памяти микропроцессора.

- •Канал прямого доступа к памяти

- •Виды запоминающих устройств.

- •Распределение адресного пространства.

- •Диспетчер памяти

- •Озу статического типа (sram)

- •Озу динамического типа (dram).

- •Регенерация по таймеру.

- •«Прозрачная» регенерация.

- •1 Мультиплексор позволяет пропускать на выход либо разряды адреса, либо состояние счетчика регенерации.

- •Организация кэш-памяти.

- •Системы адресации кэш-памяти.

Распределение адресного пространства.

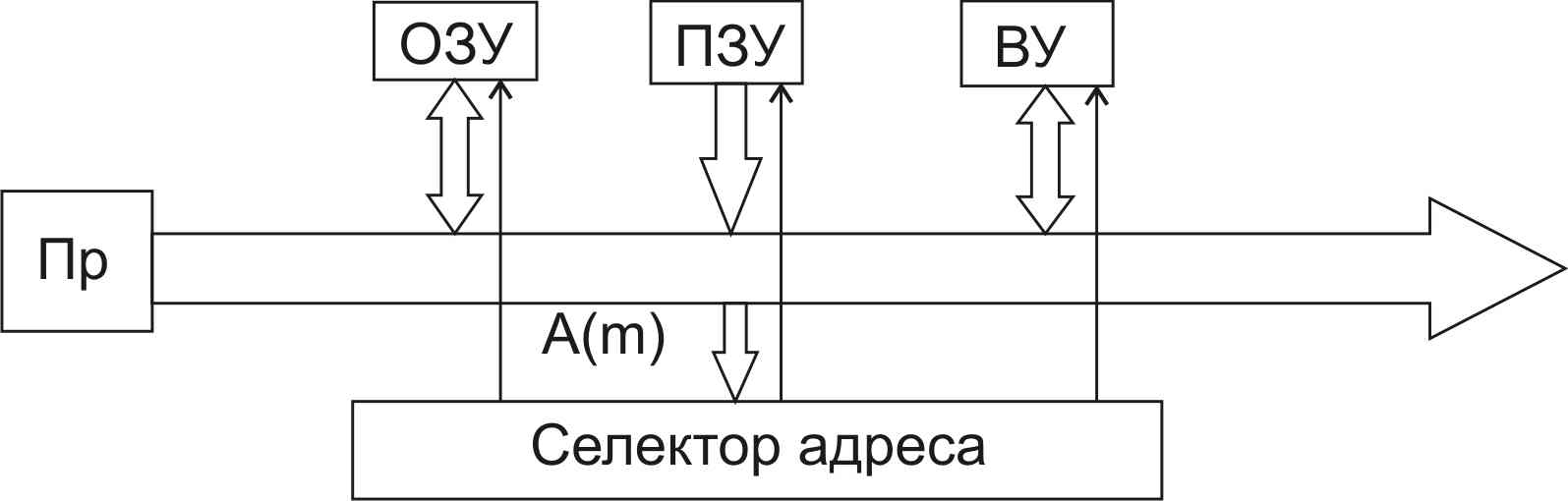

Объем адресного пространства определяется двумя параметрами: разрядностью шины адреса и набором управляющих сигналов. Если размер шины n разрядов, то адресуемое адресное пространство получается 2^n. Управляющие сигналы интерфейсной шины определяют тип объекта запоминания, к которому происходит обращение с помощью этих управляющих сигналов, происходит разделение обращения к ОЗУ, к стеку, к ПЗУ и другим устройствам. Схема организации подключения памяти к процессору выглядит следующим образом:

На шину процессора подключаются все типы запоминающих устройств. Это могут быть ОЗУ, ПЗУ, ВУ. Также на шину подключается операционное устройство, которое называется селектор адреса. Этот селектор анализирует код адреса A(m) и вырабатывает управляющие сигналы активации того или иного внешнего устройства. Такой прием позволяет размещать все устройства запоминания в едином адресном пространстве, а выбирать для работы с помощью селектора то устройство, которое в данный момент адресовано.

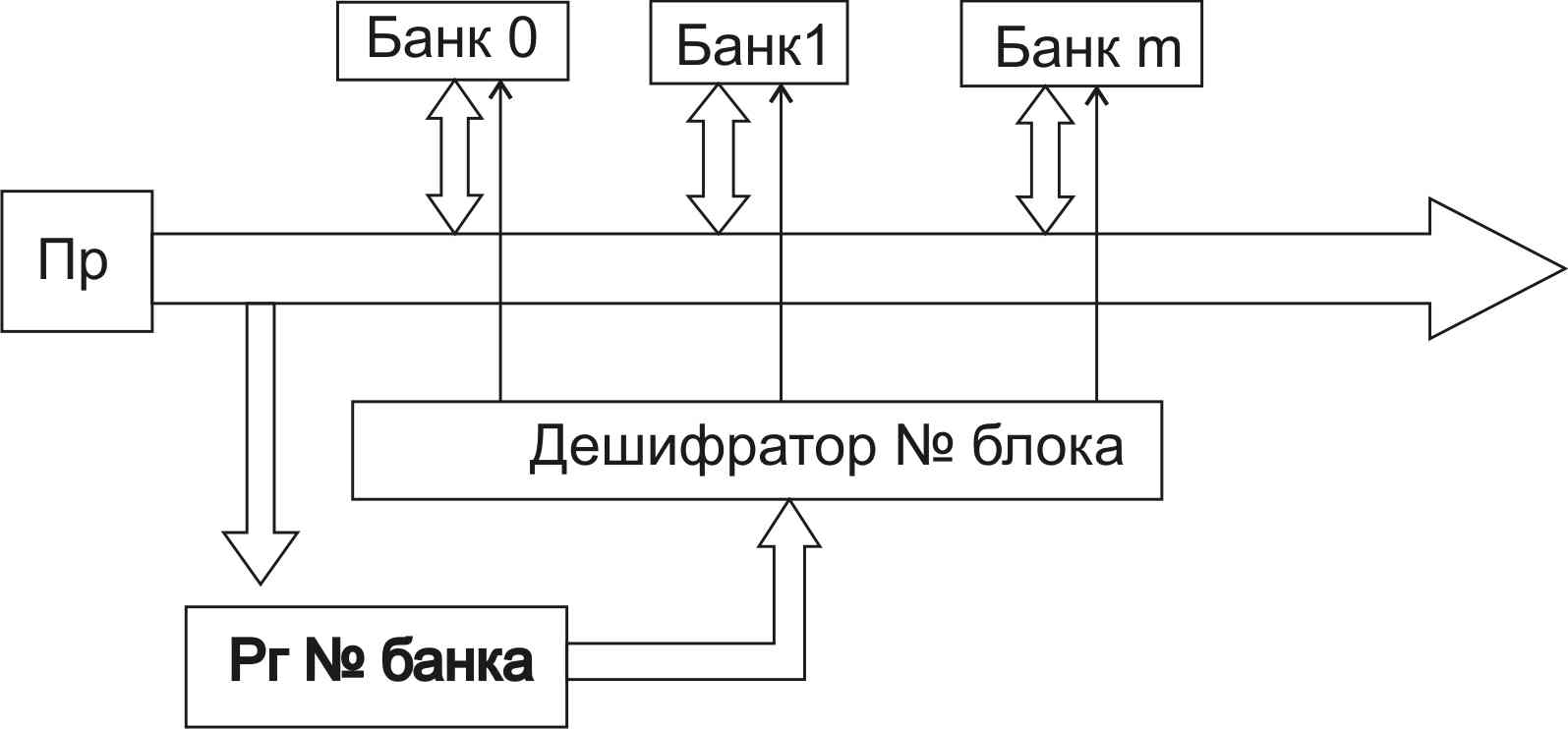

Диспетчер памяти

Данное устройство позволяет расширить адресное пространство за пределом возможной адресации с помощью имеющихся n разрядов. Для этого все запоминающее устройство подразделяется на так называемые банки памяти. В пределах каждого банка памяти адресация ячеек производится с помощью имеющихся n адресных разрядов, а диспетчер памяти позволяет выбрать для работы только 1 из имеющихся банков. Все банки памяти нумеруются в возрастающем порядке, номер банка задается с помощью специального регистра номера блока. Заданный в этом регистре код номера банка дешифруется, и полученный управляющий сигнал поступает на разрешающий вход банка памяти. Если сигнал разрешения есть, то блок выбран и может работать. Схема выглядит следующим образом:

В этом случае, объем адресуемого пространства памяти резко увеличивается. Следует заметить, что регистр номера банка доступен процессору на программном уровне, поэтому из программы можно управлять выбором необходимого для работы банка памяти.

Озу статического типа (sram)

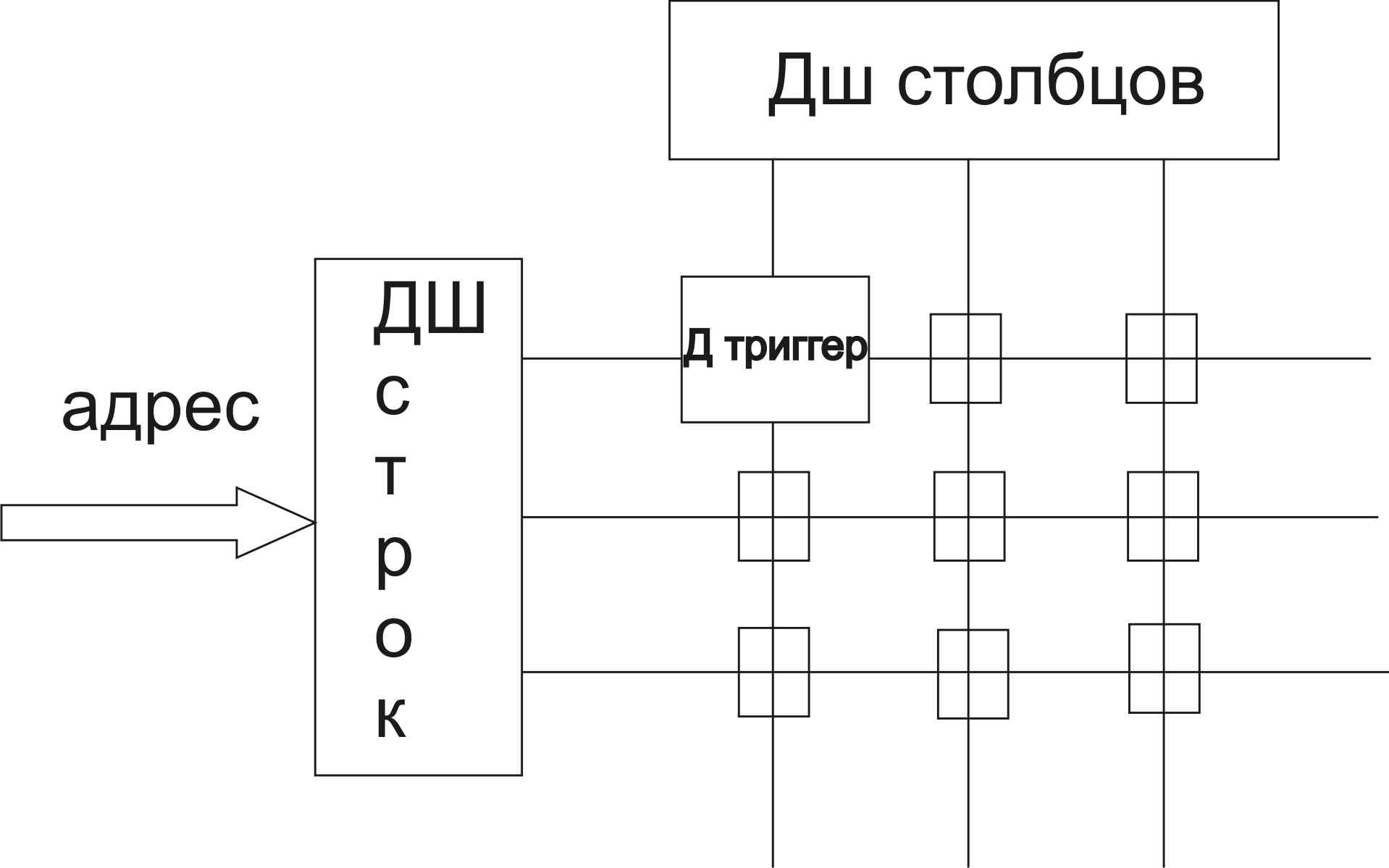

В качестве запоминающих элементов в пространстве, память в этом случае использует обычный Д-триггер. Это запоминающие элементы, т.е. Д-триггеры располагаются в узлах запоминающей матрицы. Схема такого устройства выглядит следующим образом:

Выбор элементов запоминания по строкам осуществляет дешифратор строк, который преобразует часть адресного кода в управляющий сигнал по одной из строк. Выбор элемента запоминания по второй координате, по столбцу, осуществляется с помощью дешифратора столбцов, который преобразует вторую часть адресного кода в управляющий сигнал на одном из столбцов. Активным может быть только тот элемент запоминания, который окажется на пересечении выбранного столбца и выбранной строки. Использование такой статической памяти позволяет довольно просто управлять ее работой. Одним из недостатков этого типа памяти является сравнительно небольшая емкость устройства при заданных геометрических размерах. Поэтому такую быстродействующую память используют в современных микропроцессорных системах для создания буферных запоминающих устройств относительно небольшого объема. Например, для кэш-памяти, которая позволяет согласовывать скорость работы процессора и скорость работы основной памяти. По своему способу работы, статическая память может быть асинхронной, или синхронной. Если используются синхронные запоминающие устройства, то после их адресации выдается еще сигнал синхронизации, по которому бит информации записывается в триггер или снимается из него.