- •Общая организация микропроцессорных систем.

- •Адресация операндов при выполнении программ.

- •Структурная схема микроЭвм

- •Структурная схема процессора.

- •Регистр стека

- •Команды процессора.

- •3.Команды обращения к подпрограммам.

- •5.Команды ввода/вывода. Эта группа команд весьма разнообразна и очень существенно зависит от архитектуры конкретной эвм. В учебных целях рассматривается команда вывода output и команда ввода input.

- •Способы адресации

- •Структура команд.

- •Виды адресаций pdp-11

- •Архитектура микропроцессоров intel.

- •Общие сведения о микропроцессоре Intel (16-разрядный)

- •Сегменты и смещения.

- •Регистры сегментов

- •Регистры указателей индексов

- •Указатель команд

- •Режим адресации

- •Регистровая и непосредственная адресация

- •Режимы адресации памяти

- •Прямая адресация

- •Косвенная регистровая адресация

- •Адресация по базе

- •Прямая адресация с индексированием

- •Смещение dispH/dispL

- •Шинная организация эвм

- •Эволюция шинной организации микропроцессорных систем.

- •3) Применение конвертеров системной шины

- •Применение кэш-памяти.

- •Передача информации по шинам микро эвм

- •Стробирование сигналов на шинах данных.

- •Передача данных по шине по методу «запрос-ответ»

- •Способ передачи данных с внешней синхронизацией.

- •Организация ввода/вывода микропроцессорных систем.

- •Адресация внешнего устройства.

- •Классификация методов ввода/вывода.

- •Системный интерфейс микропроцессора Intel

- •Локальный интерфейс Intel 80-386

- •Модель функционирования локального интерфейса микропроцессора Intel 80386

- •Подсистема прерываний

- •Использование контроллеров прерывания для повышения быстродействия микропроцессорной системы.

- •Программирование контроллеров прерывания.

- •Организация памяти микропроцессора.

- •Канал прямого доступа к памяти

- •Виды запоминающих устройств.

- •Распределение адресного пространства.

- •Диспетчер памяти

- •Озу статического типа (sram)

- •Озу динамического типа (dram).

- •Регенерация по таймеру.

- •«Прозрачная» регенерация.

- •1 Мультиплексор позволяет пропускать на выход либо разряды адреса, либо состояние счетчика регенерации.

- •Организация кэш-памяти.

- •Системы адресации кэш-памяти.

Смещение dispH/dispL

Как видно из таблицы использование смещения задается кодом md, т.е чтобы правильно задать смещение нужно правильно задать md. В мниманической формуле команды видно есть ли там смещение и каковым оно должно быть, если смещение отсутствует , то md=0, если смещение не велико, то для данной величины смещения хватит 1 байта, md=01, если смещение большое, то необходимо привлекать 16-ти разрядную dispHdispL→md=10.

Если в команде используется ячейка памяти помеченная символьным именем (меткой), то md нужно выбирать 10,т.е 16-ти разрядное смещение.

Если используется прямая адресация,то тогда md=0, но прямой адрес задаётся 16-ти разрядным смещением.

DateH и DateL

Эти поля служат для задания данных, т.е операндов внутри команды, т.е операнд может быть размером со слово или размером с байт. Данные в команде нах-ся во время непосредственной адресации, если операция байтовая , т.е W=0, то непосредственное байтовое значение операнда располагается в байте dispL, если команда работает со словом, т.е W=1, то используются обе DateH и DateL.

В формуле команды данные и смещение записываются в десятичном виде, а внутрь команды мы их должны поставить в двоичном виде, следовательно нужно уметь переводить из десятичного в двоичный, отрицательные числа записываются в особом виде.

Для задания размерности операндов в ассемблере Intel существует специальный оператор указания типа операнда PTR, если такой оператор используется то сразу становиться ясно какой размерности будет операнд.

<ТИП>PRT<выражение>, тип может быть Bate или Word

В лаб. работе существует некоторые команды которые работают с ячейками помеченными метками, если такую метку встречаем, то обращаемся к таблице значений, в этой таблице показано, что скрывается за этой меткой

Например: ma Byte Date 0002

Запись означает, что этой командой должна выбираться операция размерности байт, W=0, то выбирается сегмент данных DS и что внутри этой ячейки находятся смещения +216, это означает . что при нахождении смещения все перечисленные dispы должны быть алгебраически учтены, при вычислении системы.

Шинная организация эвм

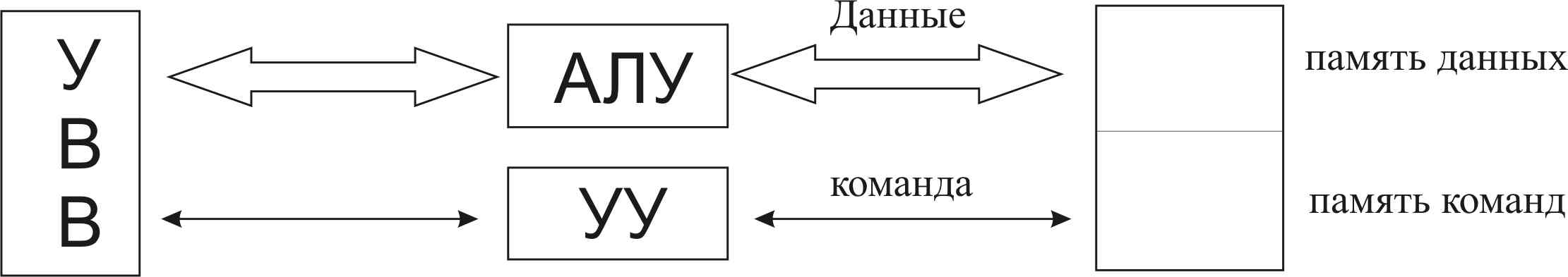

Исторически существуют 2 классических варианта организации вычислительных машин , это структура фонНеймона и Гарвардская.

В структуре фонНеймона главной отличительной чертой яв-ся то, что команды и данные находятся в едином поле памяти.

Команды и данные работают с единым полем памяти, если в АЗУ выйдет отдельно память команды и память данных, то получим Гарвардскую структуру.

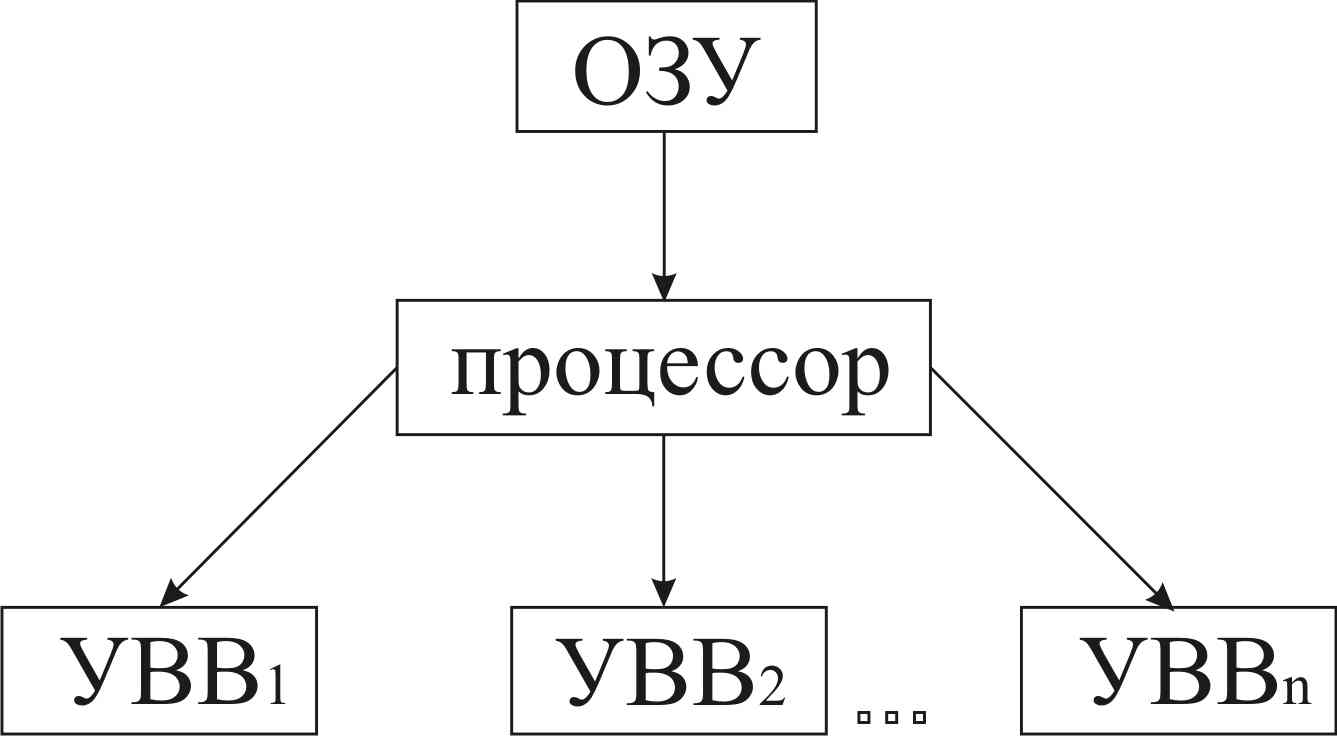

В течении всего развития ЭВМ главным остаётся вопрос, как объединить в единую систему память, процессор и внешние устройства. Первоначально ЭВМ строились по радиальному принципу.

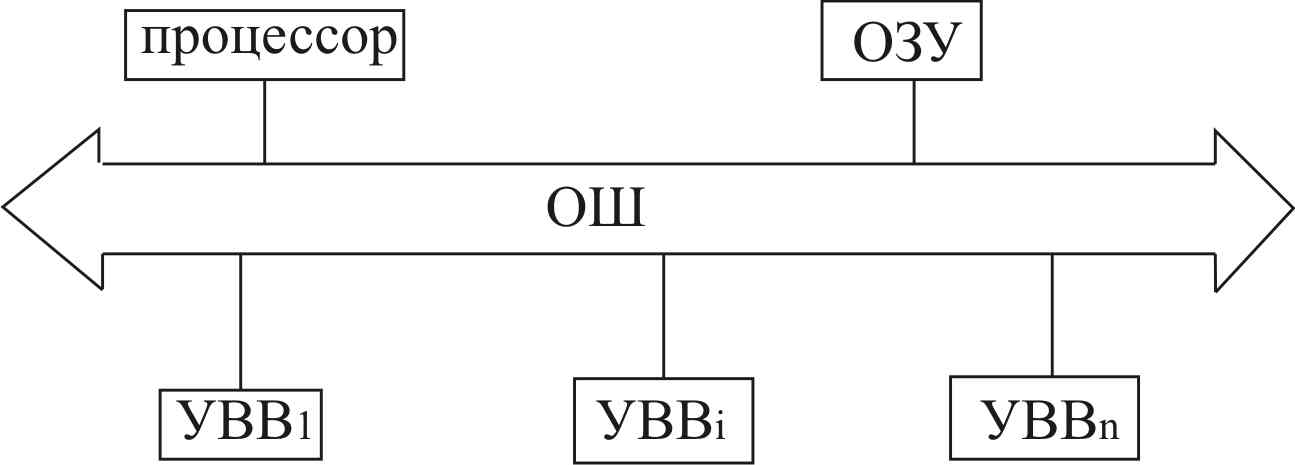

Эта радиальная структура на ранних этапах развитий чётко соответствовала пониманием того, что процессор с одной стороны работает с памятью, а с другой стороны имеет все необходимые элементы подключения различных по типу внешних устройств. Рассмотреть такую систему было затруднительно, т.к. процессор имел ограниченное число интерфейсов, переворот в понимании организации взаимосвязи между элементами микро ЭВМ произошел с появлением так называемой обшей шины. В этом случае все элементы ЭВМ подключаются единообразно к некоторому набору проводников, который представляет собой общую шину. Впервые такая архитектура появилась в машине фирмы DEC PDP-11 (наши аналоги СМ-3,СМ-4).В этой архитектуре все ячейки памяти и все регистры внеш. устройств адресуются единообразно. Программисту надо лишь знать под каким адресом находится регистр команд и регистр памяти тех или иных внешних устройств. Расширяется система вставлением блока на свободное место.

У разработчиков микро ЭВМ существует стремление сделать микропроцессорную систему с одной стороны открытую для расширения, а с другой – наиболее быстродействующую. ЭтJи два требования требуют определенного компромисса с точки зрения структуры системы. Принцип открытости, который позволяет разработчику легко подключать к микро ЭВМ дополнительные блоки, а в особенности переферийные устройства были впервые применяли в компьютерах IBM PC. Эта структурная организация на сегодняшний день стала практически стандартом для всех производителей персональных компьютеров. Основную шину микро ЭВМ образует организованная группа линий передачи сигналов. IBM PC шину можно разделить на 3 составляющий: 1-адресная шина, 2-шина данных, 3-шина управления.

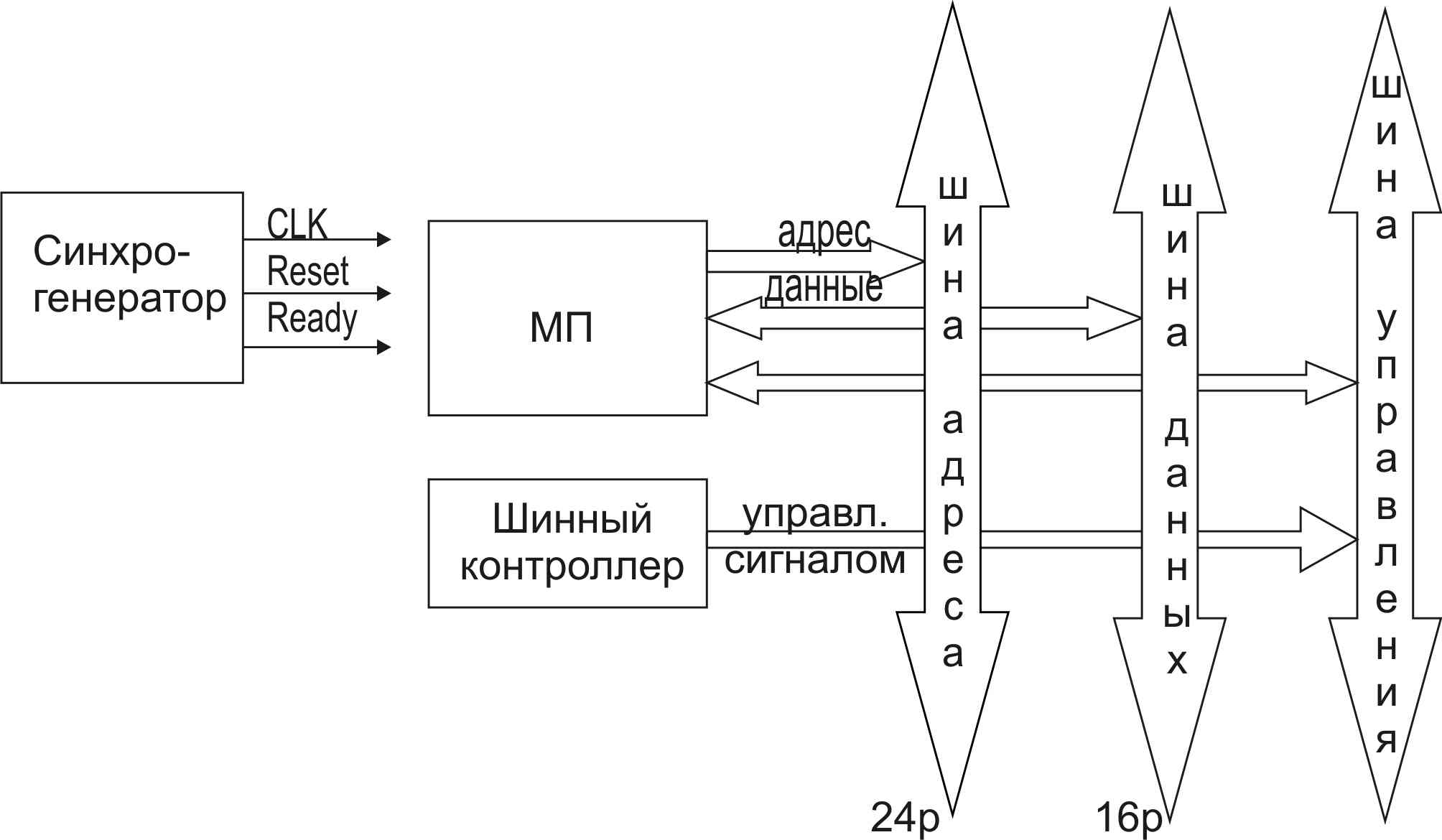

Структурная схема микро ЭВМ шинной организации выглядит следующим образом.

Синхрогенератор – это такой блок, который вырабатывает набор синхро последовательностей и несколько одиночных сигналов. Сигнал Reset – это сигнал начального сброса, который приводит в исходное состояние все элементы микро ЭВМ. Сигнал готовности Ready является специфичным сигналом и используется при работе с медленными периферийными устройствами. Сигнал ССК является основным тактовым сигналом микропроцессора. Он синхронизирует работу как самого микропроцессора, так и всех остальных микросхем микро ЭВМ. Микропроцессор обменивается сигналами с тремя шинами. Первая из них – шина адреса. Она имеет шину 24 разряда и используется для адресации ячеек памяти и периферийных устройств. Шина данных имеет 16 разрядов. Для осуществления гибкости программирования по этой шине может производиться обмен как словом, так и байтом, т.е. используется 8 разрядов этой шины, при чем могут используется как младшие разряды шины, так и старшие 8 разрядов этой шины. Шина управления организует работу всей микропроцессорной системы с помощью шинного контроллера. Микропроцессор осуществляет двухсторонний обмен управляющими сигналами с этой шиной.