- •1. Структура многоуровневой системы управления. Решаемые задачи и требования к системе.

- •Структура многоуровневой су:

- •2. Структура и устройства управляющей микропроцессорной системы. Способы аналоговой обработки данных.

- •4. Схемы сопряжения устройств озу, пзу и портов ввода/вывода с шинами системной магистрали.

- •Управление доступом к устройствам мп-системы:

- •5. Применение дешифраторов, ппзу и плм в схемах выборки устройств мп-системы.

- •6. Структура и интерфейс 8-разрядного микропроцессора.

- •7. Цикл выполнения команды 8-разрядного микропроцессора.

- •8. Диаграмма машинного цикла 8-разрядного микропроцессора. Типы машинных циклов, используемых при выполнении команд. Диаграмма цикла микроконтроллера mcs-51.

- •9. Системный контроллер мп – системы и системные сигналы управления.

- •10. Программистские модели 8-разрядных микропроцессоров (ресурсы, способы представления данных и виды адресации, слово состояния программы). Работа со стеком.

- •11. Структура и интерфейс микроконтроллеров с архитектурой cisc (на примере mcs-51).

- •12. Логическая организация памяти микроконтроллера mcs-51.

- •13. Характеристика системы команд микроконтроллера мcs-51. Слово состояния программы, типы данных, способы адресации. Организация ветвлений в программах.

- •14. Состав и назначение регистров специальных функций в микроконтроллерах.

- •15. Базовые арифметические операции целочисленной 8-разрядной двоичной арифметики. Признаки результата.

- •16. Операции умножения/деления двоичных чисел.

- •17. Арифметическая обработка многобайтных операндов в микропроцессорах и микроконтроллерах с 8 – разрядной архитектурой.

- •18. Сложение-вычитание многобайтных 2-10 чисел в 8-разрядных микропроцессорах и микроконтроллерах.

- •19. Логическая обработка данных в микроконтроллерах. Битовые операции. Вычисление логической функции, аргументы которой поступают по входным линиям порта (задача).

- •20. Порты параллельного синхронного ввода-вывода мп систем. Программирование ввода-вывода.

- •21. Схемы портов параллельного асинхронного ввода-вывода мп – систем.

- •22. Структурная схема параллельного программируемого интерфейса. Основные режимы работы.

- •23. Организация ввода-вывода данных по запросам прерываний от схемы программируемого параллельного интерфейса.

- •24. Схемы и принципы работы двунаправленного (p0) и квазидвунаправленных портов (p1, p2, p3) микроконтроллеров mcs-51.

- •25. Режимы работы портов ввода-вывода микроконтроллеров avr.

- •26. Параллельный обмен данными с внешними устройствами в микроконтроллерных системах. Обмен с квитированием.

- •27. Схема, основные режимы работы и программирование таймера микроконтроллера mcs51.

- •28. Применение таймеров mcs51 для отсчета времени, измерения длительности сигнала, подсчета событий, формирования периодических сигналов.

- •1. Подсчет числа импульсов, поступающих на вход мк51 за 10мс.

- •2. Измерение длительности сигнала, поступающего на вход .

- •3. Организовать временную задержку длительность 500мс

- •29. Таймеры микроконтроллеров avr. Использование таймеров для сравнения, захвата событий, формирования шим-сигналов, в сторожевом режиме.

- •30. Основные функции системы прерываний.

- •31. Способы программной и аппаратной идентификация запроса прерываний в одноуровневых и многоуровневых системах прерываний.

- •32. Механизм обработки векторных прерываний в мп-системах с помощью команд rst n и call addr.

- •Радиально - векторная система прерываний (на примере микропроцессора i8085).

- •33. Контроллер прерываний. Структура, интерфейс, способы обработки прерываний.

- •34. Построение системы прерываний с несколькими контроллерами. Идентификация запроса прерываний.

- •35. Программирование контроллера прерываний. Назначение управляющих слов при инициализации контроллера и во время работы.

- •36. Система прерываний микроконтроллера mcs51. Работа со стеком.

- •37. Структура и основные режимы работы канала последовательного ввода-вывода uart микроконтроллера mcs-51.

- •38. Программирование приёма/передачи данных по каналу uart между двумя микроконтроллерами.

- •39. Организация обмена данными между микроконтроллерами при работе в сети.

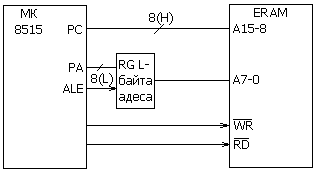

- •40. Схема интерфейса микроконтроллера mcs-51 с внешней памятью программ, внешней памятью данных и дополнительными портами ввода-вывода.

- •41. Основные средства и способы организации взаимодействия микроконтроллера с клавиатурой и дисплеем.

- •42. Контроллер клавиатуры и дисплея - структура и программируемые операции.

- •2. С электронной коммутацией датчиков.

- •3. С кодированным сканированием (электрическая коммутация)

- •43. Применение ацп и цап в мп-системах.

- •44. Устройства энергонезависимой памяти с последовательным интерфейсом (на примере at25, at45).

- •45. Память DataFlash -структура, операции, применение.

- •47. Организация адресного пространства микроконтроллеров avr, способы адресации памяти программ и памяти данных.

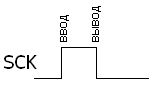

- •48. Интерфейсы последовательной связи uart, spi, i2c.

- •49. Системы на кристалле: типы cSoC, структура, основные характеристики и функции, среда проектирования.

- •Основные характеристики

44. Устройства энергонезависимой памяти с последовательным интерфейсом (на примере at25, at45).

Речь идёт о памяти EEPROM.

Цикл обращения к EEPROM при записи данных:

1. Проверка доступности (ожидание обновления флага в регистре управления EEWE)

2. При EEWE = 0 происходит запись адреса (пересылка) в регистр адреса, запись данных в регистр данных, в регистре управления устанавливается регистр разрешения записи EEMWE и через 4 такта EEWE устанавливается в 1.

3. Начинается режим записи, который длится > 2 мс, после чего происходит аппаратный сброс флага и повторение цикла.

Имеются 2 бита защиты, которыми можно запретить доступ к памяти на считывание и запись.

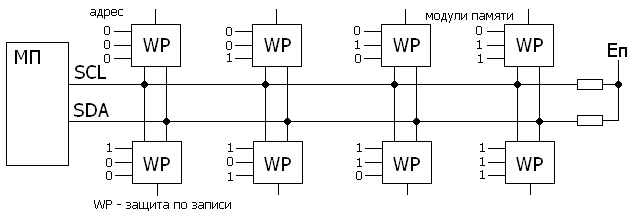

Память последовательного типа EEPROM.

Объём: 128б – 128 Кбайт. Напряжение питания – 1.8 – 5.5 В.

Для записи данных на страницу предварительно заносим данные в буфер и после сигнала STOP на интерфейсе происходит стирание страницы и перенос данных из буфера на страницу. При записи границы между страницами сохраняются, т.е. при достижении границы страницы запись дальше пойдёт с начала страницы. При чтении контроль границ страниц не осуществляется. Возможные размеры страниц: 8, 16, 32, 64, 128, 256 б/Мб.

Некоторые модели внутри разбиваются на банки. Может быть 2,4,8 банков. Это делается для уменьшения количества интерфейсных входов на 1, 2, 3 соответственно (интегрируем 2, 4, 8 схем в одну).

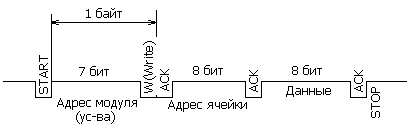

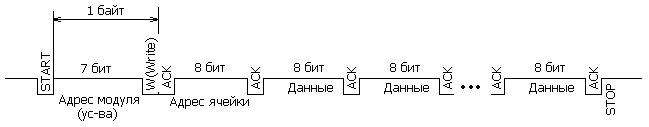

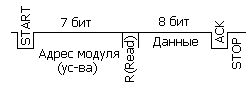

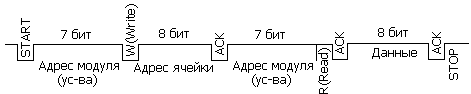

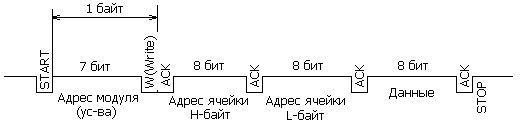

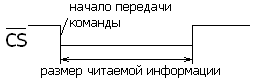

Временные диаграммы работы EEPROM:

1. Запись одиночного бита:

2. Запись страничная (последовательности байт):

3. Чтение по текущему адресу:

4. Чтение по заданному адресу:

Временные диаграммы операций чтения/записи были приведены для единого адресного пространства в схеме. Если же устройство поделено на банки, то в протоколе адрес устройства вида 1010A2A1A0 модифицируется на:

1010А2А1Р0 – для 2х банков (Р0 – номер банка).

1010А2Р1Р0 – для 4х банков.

1010Р2Р1Р0 – для 8ми банков.

В случае расширения имеем: 1А2А1А0Р2Р1Р0 (2К∙8 = 16 Кбайт).

В случае использования протокола I2C (линейка АТ24) временная диаграмма записи одиночного байта выглядит следующим образом:

45. Память DataFlash -структура, операции, применение.

Объём 1-64 Мбит.

Данная память применяется для хранения больших объёмов данных, используется для оцифровки звука, хранения фотографий и т.д. Сферы применения: хранения данных при работе приложений, хранение программ, хранение таблиц констант

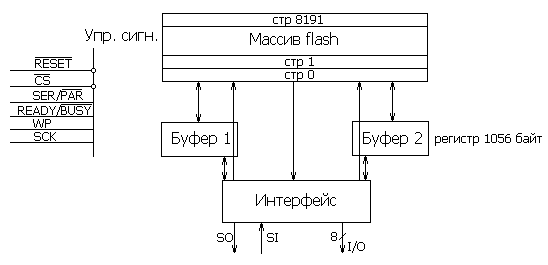

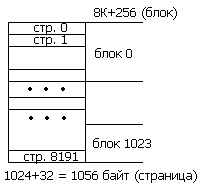

Структура памяти DataFlash.

SO – Serial Output

SI – Serial Input

WP – защита по записи

![]() - последовательная или параллельная

передача.

- последовательная или параллельная

передача.

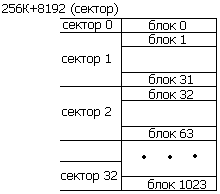

Логическая организация памяти.

Есть 3 уровня памяти – сектора, блоки и структуры.

Операции

1 .

Чтение/запись на уровне страниц.

.

Чтение/запись на уровне страниц.

2. Стирание на уровне страниц и блоков.

3. Операции чтения:

3.1 Непрерывное чтение

КОП (1 байт), 3 байта адреса (Nстр (13 р.) + N на стр. (11 р.))

3.2 Постраничное чтение

3.3. Чтение буфера

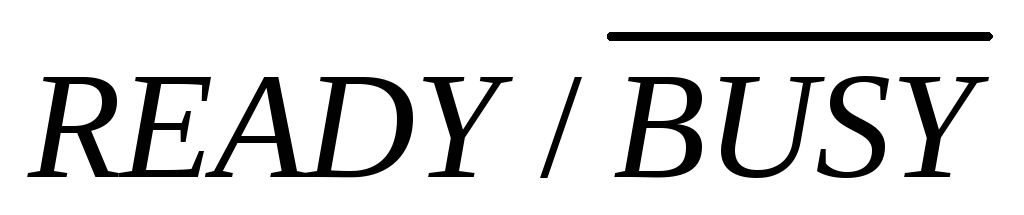

3.4 Чтение слова состояния

-

COMP

Условный код размера DataFlash

4. Операции записи/стирания

4.1 Запись в буферы

4.2 Копирование из буфера

4.2.1 Со встроенным стиранием

4.2.2 Без встроенного стирания

4.3 Запись через буферы

4.4 Стирание страниц и блоков

5. Дополнительные операции

5.1 Копирование страниц из flash в буфер 1 или 2

5.2 Сравнение страниц flash и буфера 1 или 2

5.3 Автоматическая перезапись страниц с использованием буфера 1 или 2

Алгоритмы записи:

1. Запись через буферы.

2. Запись в буфер и копирование.

Эти алгоритмы применяются при последовательной записи страницы за страницей.

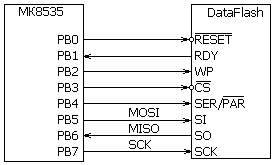

Схема взаимодействия МК с DataFlash:

-

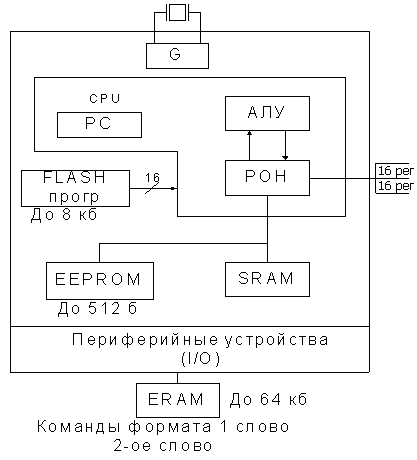

46. AVR - микроконтроллеры. Архитектура и назначение устройств.

Обобщенная архитектура:

G – генератор. Настройка RC – генератора происходит в самом МП. АЛУ и РОН имеют по 8 разрядов. Память выполнена по Гарвардской архитектуре.

Память программ предназначена для хранения команд, управляющих функционированием МК. В памяти программ также хранятся различные константы, не меняющиеся во время работы программы. Память программ представляет собой электрически стираемое ППЗУ (FLASH-ПЗУ). Для адресации используется счетчик команд.

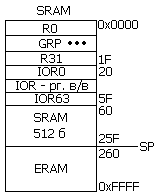

П амять

данных разделена на три части: регистровая

память, оперативная память (статическое

ОЗУ) и энергонезависимое EEPROM.

Регистровая память включает в себя 32

РОНа (32 байта) и служебные регистры ВВ

(64 байта). В области регистров ВВ

расположены различные служебные

регистры (регистр указатель стека,

регистр состояния и др.), а также регистры

управления ПУ, входящими в состав МК.

Для хранения переменных программ вместе

с регистрами также может использоваться

статическое ОЗУ. Есть возможность

подключения внешнего статического ОЗУ

объемом до 64 Кбайт. Для хранения данных,

которые могут изменяться в процессе

настройки и функционирования готовой

системы (калибровочные константы,

серийные номера, ключи и т. п.), может

быть использована EEPROM.

Эта память расположена в отдельном

адресном пространстве, а доступ к ней

осуществляется с помощью определенных

РВВ.

амять

данных разделена на три части: регистровая

память, оперативная память (статическое

ОЗУ) и энергонезависимое EEPROM.

Регистровая память включает в себя 32

РОНа (32 байта) и служебные регистры ВВ

(64 байта). В области регистров ВВ

расположены различные служебные

регистры (регистр указатель стека,

регистр состояния и др.), а также регистры

управления ПУ, входящими в состав МК.

Для хранения переменных программ вместе

с регистрами также может использоваться

статическое ОЗУ. Есть возможность

подключения внешнего статического ОЗУ

объемом до 64 Кбайт. Для хранения данных,

которые могут изменяться в процессе

настройки и функционирования готовой

системы (калибровочные константы,

серийные номера, ключи и т. п.), может

быть использована EEPROM.

Эта память расположена в отдельном

адресном пространстве, а доступ к ней

осуществляется с помощью определенных

РВВ.

Память SRAM имеет объём 512 байт, EEPROM – также 512 байт. ERAM – внешняя память данных. Запись информации в ячейку EEPROM длиться 2.5-4 мс. В AVR хорошо представлены UART, SPI и TWI (I2C) (в ATMega). Таймеры T0, T1, T2 и WDT. Работа с ERAM происходит медленнее, чем с SRAM (1 МТ). В МК AVR есть режимы энергосбережения Idle и Power Down Mode. Выход из режимов длиться 16 мс.