- •Ответы по мпс (по Вовану – 2008-2009 уч.Г.)

- •1. Классификация микропроцессоров. Архитектуры микропроцессоров. Микропроцессорные комплекты, системы на кристалле.

- •2. Ацп. Основные характеристики, структурные схемы.

- •3. Цап. Основные характеристики, структурные схемы.

- •4. Микроконтроллеры семейства mcs51. Структура, параметры.

- •5. Микроконтроллеры семейства mcs51. Организация памяти.

- •6. Микроконтроллеры семейства mcs51. Система команд.

- •7. Микроконтроллеры avr. Структуры, параметры.

- •8. Микроконтроллеры avr. Организация памяти, внешняя память.

- •9. Микроконтроллеры avr. Система тактирования.

- •10. Микроконтроллеры avr. Организация портов ввода/вывода.

- •11. Микроконтроллеры avr. Сторожевой таймер, логика сброса.

- •12. Микроконтроллеры avr. Подсистема прерываний.

- •13. Микроконтроллеры avr. Таймеры.

- •14. Микроконтроллеры avr. Модуль захвата и сравнения, режимы шим.

- •15. Микроконтроллеры avr. Интерфейс spi.

- •16. Микроконтроллеры avr. Интерфейс usart.

- •17. Микроконтроллеры avr. Интерфейс twi.

- •18. Микроконтроллеры avr. Модуль ацп.

- •19. Микроконтроллеры avr. Система команд.

- •20. Микроконтроллеры avr. Методы адресации.

- •21. Микроконтроллеры avr. Организация интерфейса с семисегментным индикатором и матричной клавиатурой.

- •22. Ассемблер микроконтроллеров avr. Приемы программирования.

- •23. Программные и аппаратные средства разработки и отладки микропроцессорных систем.

- •24. Цифровые сигнальные процессоры, структуры, характеристики, области применения.

- •25. Цсп семейства tms320c2000. Структура, основные характеристики.

- •39. Организация интерфейса usb.

- •40. Шина isa. Организация, протокол обмена.

- •41. Шина pci. Организация, протокол обмена.

- •42. Проектирование микропроцессорных систем. Цикл проектирования.

- •43. Организация питания микропроцессорных систем. Импульсные источники питания.

Ответы по мпс (по Вовану – 2008-2009 уч.Г.)

1. Классификация микропроцессоров. Архитектуры микропроцессоров. Микропроцессорные комплекты, системы на кристалле.

Архитектура МП - это его логическая организация, рассматриваемая с точки зрения пользователя; она определяет возможности микропроцессора по аппаратной и программной реализации функций, необходимых для построения микропроцессорной системы. Понятие архитектуры микропроцессора отражает:

- его структуру, т.е. совокупность компонентов, составляющих микропроцессор, и связей между ними; для пользователя достаточно ограничиться регистровой моделью микропроцессора;

- способы представления и форматы данных;

- способы обращения ко всем программно-доступным для пользователя элементам структуры (адресация к регистрам, ячейкам постоянной и оперативной памяти, внешним устройствам);

- набор операций, выполняемых микропроцессором;

- характеристики управляющих слов и сигналов, вырабатываемых микропроцессором и поступающих в него извне;

- реакцию на внешние сигналы (система обработки прерываний и т.п.).

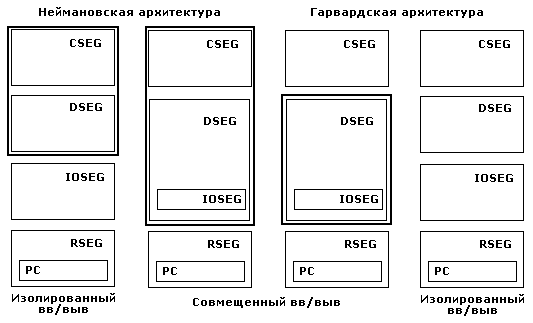

По способу организации пространства памяти микропроцессорной системы различают два основных типа архитектур:

1. Фон Неймановская (принстонская) - для хранения программ и данных используется одно пространство памяти. Программы и данные хранятся в едином пространстве, и нет никаких признаков, указывающих на тип информации в ячейке памяти.

«+»: более простая внутренняя структура микропроцессора и меньшее количество управляющих сигналов.

2. Гарвардская - память программ CSEG (Code Segment) и память данных DSEG (Data Segment) разделены и имеют свои собственные адресные пространства и способы доступа к ним.

«+»: позволяет осуществлять более гибкие манипуляции информации, реализовывать компактно кодируемый набор машинных команд и, в ряде случаев, ускорять работу микропроцессора.

«-»: является более сложной и требует дополнительных управляющих сигналов.

Представители - микроконтроллеры семейства MCS-51 фирмы Intel.

RSEG – регистровый сегмент.

МП-системы с трехшинной и двухшинной системной магистралью.

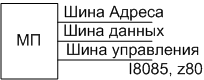

На физическом уровне микропроцессор взаимодействует с памятью и системой ввода-вывода через единый набор системных шин - внутрисистемную магистраль. Она, в общем случае состоит из:

- шины данных DB (Data Bus), по которой производится обмен данными между МП, памятью и системой ВВ;

- шины адреса AB (Address Bus), используемой для передачи адресов ячеек памяти и портов ВВ, к которым осуществляется обращение;

- шины управления CB (Control Bus), по которой передаются управляющие сигналы, реализующие циклы обмена информацией и управляющие работой системы.

1. Трехшинная или демультиплексная магистраль

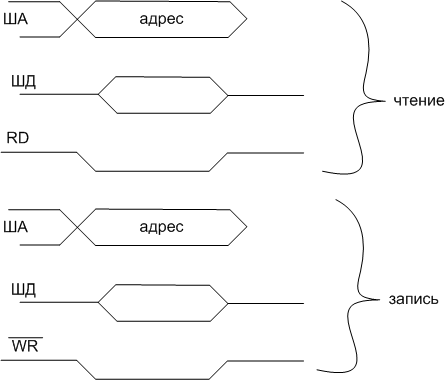

Основные операции на шинах – чтение и

запись. Чтение: из порта или ячейки

памяти в МП (![]() ).

Запись: в порт или ячейку памяти из МП

(

).

Запись: в порт или ячейку памяти из МП

(![]() ).

).

Временная диаграмма работы системных шин:

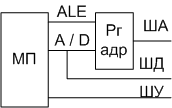

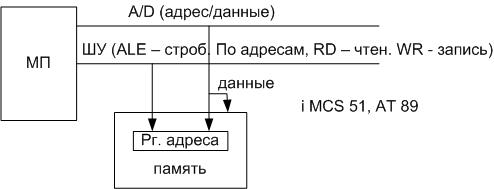

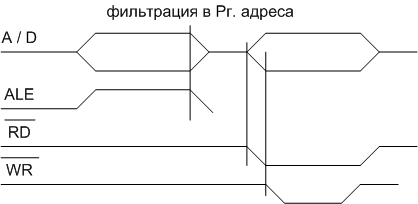

2. Двухшинная или мультиплексная магистраль

Для сокращения ширины физической магистрали вводят совмещенную шину адреса-данных AD (Address/Data Bus), по которой передаются как адреса так и данные. Этап передачи адресной информации отделен по времени от этапа передачи данных и стробируется специальным сигналом ALE (Address Latch Enable), который включен в состав ШУ.

Временная диаграмма работы:

Недостаток: необходимо иметь защелку для адреса.

Преобразование двухшинной магистрали в трехшинную магистраль: