- •Ответы по мпс (по Вовану – 2008-2009 уч.Г.)

- •1. Классификация микропроцессоров. Архитектуры микропроцессоров. Микропроцессорные комплекты, системы на кристалле.

- •2. Ацп. Основные характеристики, структурные схемы.

- •3. Цап. Основные характеристики, структурные схемы.

- •4. Микроконтроллеры семейства mcs51. Структура, параметры.

- •5. Микроконтроллеры семейства mcs51. Организация памяти.

- •6. Микроконтроллеры семейства mcs51. Система команд.

- •7. Микроконтроллеры avr. Структуры, параметры.

- •8. Микроконтроллеры avr. Организация памяти, внешняя память.

- •9. Микроконтроллеры avr. Система тактирования.

- •10. Микроконтроллеры avr. Организация портов ввода/вывода.

- •11. Микроконтроллеры avr. Сторожевой таймер, логика сброса.

- •12. Микроконтроллеры avr. Подсистема прерываний.

- •13. Микроконтроллеры avr. Таймеры.

- •14. Микроконтроллеры avr. Модуль захвата и сравнения, режимы шим.

- •15. Микроконтроллеры avr. Интерфейс spi.

- •16. Микроконтроллеры avr. Интерфейс usart.

- •17. Микроконтроллеры avr. Интерфейс twi.

- •18. Микроконтроллеры avr. Модуль ацп.

- •19. Микроконтроллеры avr. Система команд.

- •20. Микроконтроллеры avr. Методы адресации.

- •21. Микроконтроллеры avr. Организация интерфейса с семисегментным индикатором и матричной клавиатурой.

- •22. Ассемблер микроконтроллеров avr. Приемы программирования.

- •23. Программные и аппаратные средства разработки и отладки микропроцессорных систем.

- •24. Цифровые сигнальные процессоры, структуры, характеристики, области применения.

- •25. Цсп семейства tms320c2000. Структура, основные характеристики.

- •39. Организация интерфейса usb.

- •40. Шина isa. Организация, протокол обмена.

- •41. Шина pci. Организация, протокол обмена.

- •42. Проектирование микропроцессорных систем. Цикл проектирования.

- •43. Организация питания микропроцессорных систем. Импульсные источники питания.

17. Микроконтроллеры avr. Интерфейс twi.

Интерфейс последовательной связи I2C (I2C, TWSI)

МК AVR m163.

Характеристики:

1) двухпроводной

2) работа с адресуемыми устройствами (до 128)

3) 8-ми битовый обмен в любом направлении

4) имеет средства контроля передачи адреса и данных в виде подтверждения сигнала

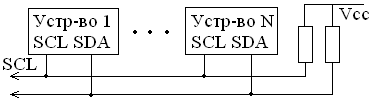

Схемотехника I2C:

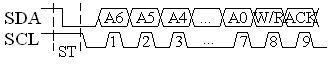

Протокол обмена по I2C:

- от ведущего выводится стартовая посылка ST (начало обмена)

- от ведущего выводится стартовый байт (7 бит.)

- от ведущего выводится бит направления обмена (1 бит) (запись от ведущего к ведомому и чтение от ведомого к ведущему)

- от ведомого поступает бит подтверждения

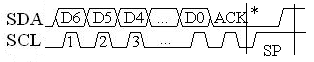

- от ведущего поступает байт (байты) данных

- от ведомого поступает бит подтверждения после каждого байта

- ведущий формирует стоповую посылку (завершение обмена)

Временные диаграммы работы I2C:

АСК – сигнал подтверждения

* - варианты возможного продолжения работы:

1) Передача данных в том же направлении

2) Выбор другого ведомого или изменение направления передачи данных, либо делается и то и другое. Для этого формируется ST (стартовая посылка) еще раз.

3) Окончание обмена (SP стоповая посылка), освобождающая шину.

Технические средства I2C в составе МК (на примере AVR):

TWDR – регистр данных, TWAR – регистр адреса, TWBR – регистр скорости, TWCR – регистр управления, TWSR – регистр статуса

Средняя

скорость (бит/с)

![]() .

Для AVR m163

.

Для AVR m163

![]() = 8МГц,

= 8МГц,

![]() = (200-600) нс.

= (200-600) нс.

Состояния TWSR:

- ведущий с передачей данных - ведущий с приемом данных - ведомый с приемом данных - ведомый с передачей данных + условие перехода к следующим словам данных в виде битов TWSR.

18. Микроконтроллеры avr. Модуль ацп.

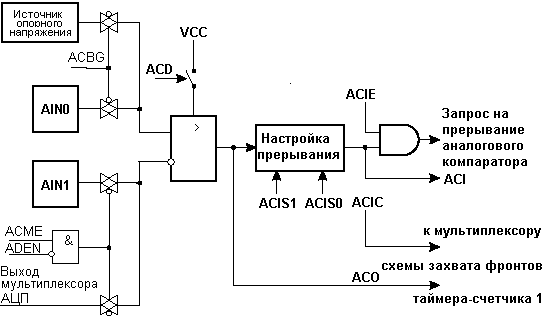

Аналоговый компаратор (на примере ATmega128)

Аналоговый компаратор сравнивает уровни напряжений на неинвертирующем входе AIN0 и инвертирующем входе AIN1. Если напряжение на неинвертирующем входе AIN0 превышает напряжение на инвертирующем входе AIN1, то выход аналогового компаратора ACO принимает единичное состояние. Выход компаратора может быть настроен для использования в качестве источника входного сигнала для схемы захвата фронтов таймера-счетчика 1. Кроме того, компаратор может генерировать собственный запрос на обработку прерывания. Пользователь может выбрать несколько событий, по которым возникает прерывание: нарастающий, падающий фронт на выходе компаратора или любое его изменение.

Включение АК осуществляется установкой бита ADEN регистра ADCSRA. Кроме того, если бит ACME регистра SFIOR установлен (и ADEN=0), то к инвертирующему входу аналогового компаратора подключается выход аналогового мультиплексора АЦП. Сброс данного бита приведет к подключению инвертирующего входа аналогового компаратора к выводу микроконтроллера AIN1. Для управления АК используется регистр ACSR (регистр состояния и управления аналогового компаратора). Его разряды: 7 – ACD: Отключение АК; 6 – ACBG: Подключение источника опорного напряжения к аналоговому компаратору; 5 – ACO: Выход аналогового компаратора; 4 – ACI: Флаг прерывания аналогового компаратора; 3 – ACIE: Разрешение прерывания аналогового компаратора; 2 – ACIC: Подключение аналогового компаратора к схеме захвата фронтов; 1, 0 – ACIS1, ACIS0: Выбор события прерывания аналогового компаратора.

Имеется возможность использовать выводы ADC7..0 в качестве неинвертирующих входов аналогового компаратора. Для организации такого ввода используется мультиплексор АЦП и, следовательно, в этом случае АЦП должен быть отключен. Если установлен бит разрешения подключения мультиплексора к аналоговому компаратору (бит ACME в SFIOR) и выключен АЦП (ADEN=0 в регистре ADCSRA), то состояние разрядов MUX2..0 регистра ADMUX определяют какой вывод микроконтроллера подключен к неинвертирующему входу аналогового компаратора. Если ACME сброшен или установлен ADEN, то в качестве неинвертирующего входа аналогового компаратора используется вывод микроконтроллера AIN1.

Аналого-цифровой преобразователь (на примере ATmega128)

ATmega128 содержит 10-разр. АЦП последовательного приближения. АЦП связан с 8-канальным аналоговым мультиплексором, 8 однополярных входов которого связаны с линиями порта F. Общий входных сигналов должен иметь потенциал 0В (т.е. связан с GND). АЦП также поддерживает ввод 16 дифференциальных напряжений. Два дифференциальных входа (ADC1, ADC0 и ADC3, ADC2) содержат каскад со ступенчатым программируемым усилением: 0 дБ (1x), 20 дБ (10x), или 46 дБ (200x). Семь дифференциальных аналоговых каналов используют общий инвертирующий вход (ADC1), а все остальные входы АЦП выполняют функцию неинвертирующих входов. Если выбрано усиление 1x или 10x, то можно ожидать 8-разр. разрешение, а если 200x, то 7-разрядное. АЦП содержит УВХ (устройство выборки-хранения), которое поддерживает на постоянном уровне напряжение на входе АЦП во время преобразования. АЦП имеет отдельный вывод питания AVCC (аналоговое питание). AVCC не должен отличаться более чем на ± 0.3В от VCC.

В качестве внутреннего опорного напряжения может выступать напряжение от внутреннего ИОНа на 2.56В или напряжение AVCC. Если требуется использование внешнего ИОН, то он должен быть подключен к выводу AREF с подключением к этому выводу блокировочного конденсатора для улучшения шумовых характеристик.

АЦП преобразовывает входное аналоговое напряжение в 10-разр. код методом последовательных приближений. Минимальное значение соответствует уровню GND, а максимальное уровню AREF минус 1 мл. разр.

Канал аналогового ввода и каскад дифференциального усиления выбираются путем записи бит MUX в регистр ADMUX. В качестве однополярного аналогового входа АЦП может быть выбран один из входов ADC0…ADC7, а также GND и выход фиксированного источника опорного напряжения 1,22 В. В режиме дифференциального ввода предусмотрена возможность выбора инвертирующих и неинвертирующих входов к дифференциальному усилителю.

Если выбран дифференциальный режим аналогового ввода, то дифференциальный усилитель будет усиливать разность напряжений между выбранной парой входов на заданный коэффициент усиления. Усиленное таким образом значение поступает на аналоговый вход АЦП. Если выбирается однополярный режим аналогового ввода, то каскад усиления пропускается

Работа АЦП разрешается путем установки бита ADEN в ADCSRA. Выбор опорного источника и канала преобразования не возможно выполнить до установки ADEN. Если ADEN = 0, то АЦП не потребляет ток, поэтому, при переводе в экономичные режимы сна рекомендуется предварительно отключить АЦП.

АЦП генерирует 10-разрядный результат, который помещается в пару регистров данных АЦП ADCH и ADCL.

АЦП генерирует собственный запрос на прерывание по завершении преобразования. Если между чтением регистров ADCH и ADCL запрещен доступ к данным для АЦП, то прерывание возникнет, даже если результат преобразования будет потерян.

Одиночное преобразование запускается путем записи лог. 1 в бит запуска преобразования АЦП ADSC. Данный бит остается в высоком состоянии в процессе преобразования и сбрасывается по завершении преобразования. Если в процессе преобразования переключается канал аналогового ввода, то АЦП автоматически завершит текущее преобразование прежде, чем переключит канал.

В режиме автоматического перезапуска АЦП непрерывно оцифровывает аналоговый сигнал и обновляет регистр данных АЦП. Данный режим задается путем записи лог. 1 в бит ADFR регистра ADCSRA. Первое преобразование инициируется путем записи лог. 1 в бит ADSC регистра ADCSRA. В данном режиме АЦП выполняет последовательные преобразования, независимо от того сбрасывается флаг прерывания АЦП ADIF или нет.

В первую очередь после объявления переменных и установки начальных адресов следует инициализировать стек и настроить АЦП. Для это заполняем соответствующие регистры:

Регистр SFIOR

ADTS2 |

ADTS1 |

ADTS0 |

- |

X |

X |

X |

X |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ADTS2:ADTS0=000 — режим непрерывного преобразования

Регистр ADMUX

REFS1 |

REFS0 |

ADLAR |

MUX4 |

MUX3 |

MUX2 |

MUX1 |

MUX0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

REFS1:REFS0=01 — источник опорного напряжения — напряжение питания AVсс

ADLAR=1 — выравнивание по левой границе 16-битного слова

MUX4:MUX0=00100 — входной канал — несимметричный вход ADC4

Регистр ADCSRA

ADEN |

ADSC |

ADATE |

ADIF |

ADIE |

ADPS2 |

ADPS1 |

ADPS0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

ADEN=1 — разрешение АЦП

ADSC=1 — запуск преобразования

ADATE=1 — режим непрерывного преобразования

ADIF=0 — флаг прерывания от компаратора

ADIE=1 – прерывание от компаратора разрешено

ADPS2:ADPS0=110 — коэффициент деления предделителя 64 (частота выборок 131072 Гц)

При завершении каждого цикла преобразования АЦП инициируется прерывание, обработчик которого читает значения регистров результата ADCH и ADCL и записывает их в соответствующие регистры общего назначения (radch и radcl). Поскольку сдвиг 10-битного результата осуществляется влево, и в рамках данной лабораторной работы достаточно 8-битной точности, то вывод на дисплей осуществляется только из регистра radch. Причём старшие 4 бита этого регистра выводятся в основном цикле работы программы на первый слева индикатор (в PORTB передаём 00000001), а младшие 4 бита — на второй слева (в PORTB — 00000010).

Помимо прочего в программе организуется задержка (цикл TIME), необходимая для возможности корректного восприятия данных с индикатора.