- •Ответы по мпс (по Вовану – 2008-2009 уч.Г.)

- •1. Классификация микропроцессоров. Архитектуры микропроцессоров. Микропроцессорные комплекты, системы на кристалле.

- •2. Ацп. Основные характеристики, структурные схемы.

- •3. Цап. Основные характеристики, структурные схемы.

- •4. Микроконтроллеры семейства mcs51. Структура, параметры.

- •5. Микроконтроллеры семейства mcs51. Организация памяти.

- •6. Микроконтроллеры семейства mcs51. Система команд.

- •7. Микроконтроллеры avr. Структуры, параметры.

- •8. Микроконтроллеры avr. Организация памяти, внешняя память.

- •9. Микроконтроллеры avr. Система тактирования.

- •10. Микроконтроллеры avr. Организация портов ввода/вывода.

- •11. Микроконтроллеры avr. Сторожевой таймер, логика сброса.

- •12. Микроконтроллеры avr. Подсистема прерываний.

- •13. Микроконтроллеры avr. Таймеры.

- •14. Микроконтроллеры avr. Модуль захвата и сравнения, режимы шим.

- •15. Микроконтроллеры avr. Интерфейс spi.

- •16. Микроконтроллеры avr. Интерфейс usart.

- •17. Микроконтроллеры avr. Интерфейс twi.

- •18. Микроконтроллеры avr. Модуль ацп.

- •19. Микроконтроллеры avr. Система команд.

- •20. Микроконтроллеры avr. Методы адресации.

- •21. Микроконтроллеры avr. Организация интерфейса с семисегментным индикатором и матричной клавиатурой.

- •22. Ассемблер микроконтроллеров avr. Приемы программирования.

- •23. Программные и аппаратные средства разработки и отладки микропроцессорных систем.

- •24. Цифровые сигнальные процессоры, структуры, характеристики, области применения.

- •25. Цсп семейства tms320c2000. Структура, основные характеристики.

- •39. Организация интерфейса usb.

- •40. Шина isa. Организация, протокол обмена.

- •41. Шина pci. Организация, протокол обмена.

- •42. Проектирование микропроцессорных систем. Цикл проектирования.

- •43. Организация питания микропроцессорных систем. Импульсные источники питания.

5. Микроконтроллеры семейства mcs51. Организация памяти.

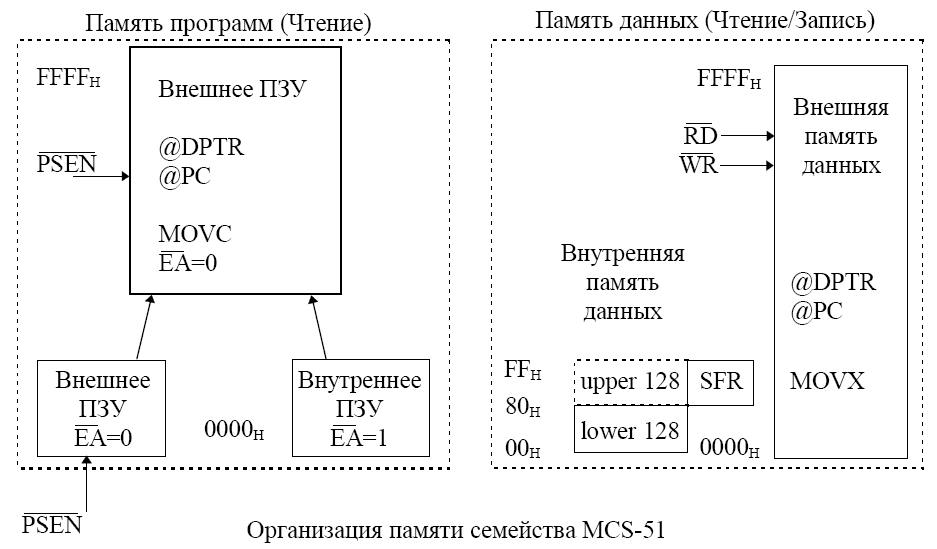

Вся серия MCS-51 имеет гарвардскую архитектуру, то есть раздельные адресные пространства памяти программ и данных. Объем внутренней (резидентной) памяти программ (ROM, EPROM или OTP ROM), располагаемой на кристалле, в зависимости от типа микросхемы может составлять 0 (ROMless), 4К (базовый кристалл), 8К, 16К или 32К. При необходимости пользователь может расширять память программ установкой внешнего ПЗУ. Доступ к внутреннему или внешнему ПЗУ определяется значением сигнала на выводе ЕА (External Access):

EA=Vcc (напряжение питания) - доступ к внутреннему ПЗУ;

EA=Vss (потенциал земли) - доступ к внешнему ПЗУ.

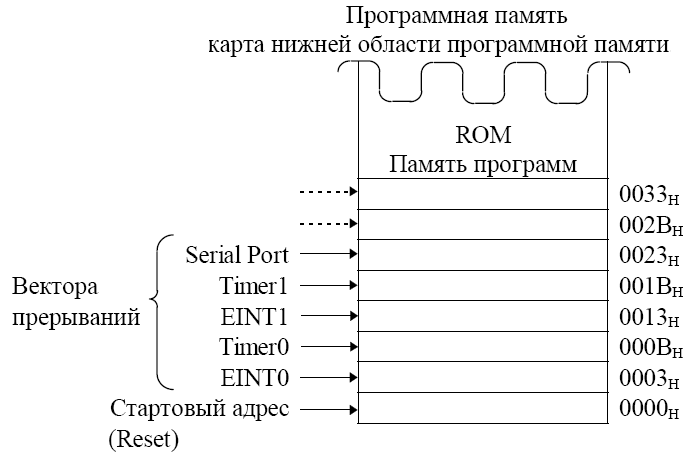

Для кристаллов без ПЗУ (ROMless) вывод ЕА должен быть постоянно подключен к Vss. Строб чтения внешнего ПЗУ - PSEN (Program Store Enable) генерируется при обращении к внешней памяти программ и является неактивным во время обращения к ПЗУ, расположенному на кристалле. Область нижних адресов памяти программ используется системой прерываний, архитектура микросхемы 8051обеспечивает поддержку пяти источников прерываний:

• двух внешних прерываний;

• двух прерываний от таймеров;

• прерывания от последовательного порта.

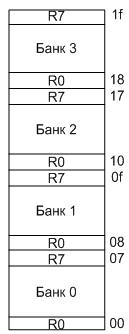

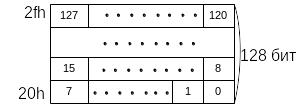

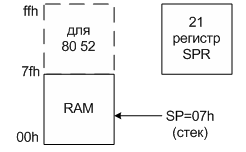

Память данных отделена от памяти программ. В этой области возможна адресация 64К внешнего ОЗУ. При обращении к внешней памяти данных ЦП микроконтроллера генерирует соответствующие сигналы чтения (RD ) или записи (WR ), взаимодействие с внутренней памятью данных осуществляется на командном уровне, при этом сигналы RD и WR не вырабатываются. Внешняя память программ и внешняя память данных могут комбинироваться путем совмещения сигналов RD и PSEN по схеме "логического И" для получения строба внешней памяти (программ/данных). Нижние 128 байт внутренней памяти данных (lower 128) присутствуют на всех кристаллах MCS-51. Первые 32 байта представляют собой 4 банка (Register Bank) по 8 регистров (R7...R0). Регистры R0 и R1 в любом из банков могут использоваться в качестве регистров косвенного адреса. Следующие за регистровыми банками 16 байт образуют блок побитно-адресуемого пространства. Набор инструкций MCS-51 содержит широкий выбор операций над битами, а 128 бит в этом блоке адресуются прямо и адреса имею значения от 00Н до 7FH. Все байты в нижней 128-байтной половине памяти могут адресоваться как прямо, так и

косвенно. Верхняя 128 байтная половина памяти ОЗУ (upper 128) в микросхеме I-8051 отсутствует, но имеется в версиях кристаллов с 256 байтами ОЗУ. В этом случае область "Upper 128" доступна только при косвенной адресации. Область SFR (Special Function Register) доступна

только при прямой адресации.

BSEG - битовый сегмент 256 бит

- для хранения логических (чего-то :)

Адресация байтами.

128 бит - биты регистров специальных функций (SFR)

CSEG - сегмент кода

DSEG - сегмент данных (внутренний)

Для стека отводится память, начиная с указателя стека, равного 07h.

Запись в стек осуществляется по байтам. Стек растет вверх. Область стека контролируется только программистом.

XSEG - внешний сегмент данных (64 Кбайт)

Независима от памяти программ.

Для работы используется команда MOVX.

RSEG - регистровый сегмент

Состоит из 32-х регистров, которые образуют 4 банка по 8 регистров.

Выбор банка производится через PSW:

![]()

C - флаг переноса. AC - флаг вспомогательного переноса. F0 - флаг 0. Может быть установлен, сброшен или проверен программой как флаг, специфицируемый пользователем.

RS1 RS0 - выбор банка регистров. OV - флаг переполнения. P - флаг паритета. Устанавливается и сбрасывается аппаратно в каждом цикле команды и фиксирует нечетное/четное число единичных бит в аккумуляторе, т.е. выполняет контроль по четности.

RS1 RS0 Банк Границы адресов

0 0 0 00h-07h

0 1 1 08h-0fh

1 0 2 10h-17h

1 1 3 18h-1fh