Бикмухаметов_-_Учебное_пособие_по_МАиМУ

.pdf

81

в разряде целых. В рассмотренном примере таковой будет мантиссa 1,101…1100000, которая получается при уменьшении порядка числа на 5.

Так как при таком подходе мантиссы всех чисел содержат в разряде целых единицу, то ее можно учитывать неявно, т.е. в памяти не хранить, а вво-

дить лишь при выполнении операций над числами с плавающей запятой.

В результате появляется дополнительный бит в представлении дробной части мантиссы.

Использование смещенных порядков (характеристик).

Чтобы упростить операции сравнения порядков, их смещают вправо по числовой оси таким образом, чтобы в дальнейшем сравнивать как целые числа без знака. Смещенные порядки или характеристики Х получают по следующим формулам. Если порядки представляются в дополнительном коде, то X = (Pдоп + 2m)·(mod2m+1) (5.2),

где: m–количество разрядов под модуль порядка, a −2m ≤ Pдоп≤ (2m−1)

Если порядки представляются в прямом коде, то |

|

X = Pпр + (2m – 1) |

(5.3), |

где – (2m – 1) ≤ Pпр ≤ (2m – 1) .

Из формул (5.2) и (5.3) следует, что: а) X ≥ 0;

б) под Х отводится (m+1) разрядов, т.е. столько же, сколько под знак и модуль порядка;

в) если PC ≥ PD, то XC ≥ XD

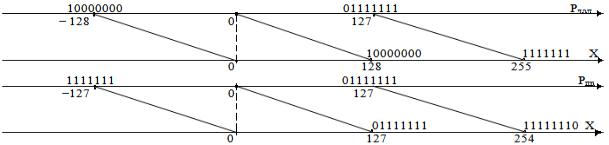

Смещение порядков можно проиллюстрировать следующими числовыми диаграммами. Пусть m = 7. Тогда (− 128) ≤ Pдоп ≤ (127), −127 ≤ Рпр ≤ 127 (рис. 5.6)

Рис. 5.6.

82

Из пунктов а), б), в) и числовых диаграмм следует, что операции над по-

рядками можно свести к операциям над характеристиками, которые рас-

сматриваются при этом как целые числа без знака. В результате упроща-

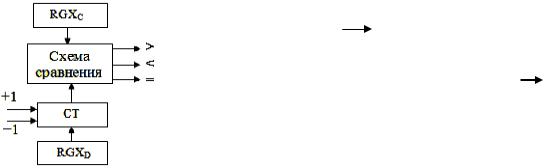

ется сравнение порядков. Например, при выравнивании порядков можно вместо KSMP использовать схему сравнения и реверсивный счетчик СТ по следующей схеме (рис. 5.7)

Пусть CT : = RGXD. Тогда при выравнивании поряд s

ков: если XC > XD, то |MD|, и CT: = CT + 1 до выполне-

ния условия: RGXC= CT; если XC < XD, то |MC|s и СТ :

= CT − 1 до выполнения того же условия.

Рис.5.7.

Стандарт IEEE 754

В процессорах основных мировых разработчиков придерживаются стан-

дарта IEEE 754 на представление формата с плавающей запятой (или точ-

кой). Согласно этому стандарту двоичные коды чисел в формате с пла-

вающей точкой могут занимать поля длиной 4.8 и 10 байтов, называемые соответственно коротким вещественным (КВ), длинным вещественным

(ДВ) и временным вещественным (ВВ) форматами.

В форматах КВ, ДВ и ВВ левый разряд поля – это знак мантиссы (он же знак числа), далее в N разрядах записывается характеристика Х (N = 8,11

и 15 соответственно), остальные L разрядов (L = 23,53 и 64 соответствен-

но) выделены под модуль мантиссы. В форматах КВ и ДВ старший бит мантиссы, равный 1, учитывается неявно. Порядки во всех фoрматах представляются в прямом коде и смещаются на величину, равную (2N−1 −

1).

Например, формат КВ имеет вид:

31 |

23 |

0 |

|

|||

|

|

|

|

|

|

|

зн |

Х |

Дробная часть |

|

M |

|

, |

|

|

|||||

|

|

|

|

|

|

|

83

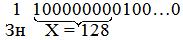

и в разрядах этого формата число Q = −2,5 = −10,1 будет представлено

кодом

Контрольные вопросы.

1.Как иначе называется ПРС в разрядах мантиссы результата?

2.Почему при потере значимости нормализация влево невозможна?

3.Какая мантисса сдвигается влево при выравнивании порядков?

4.В каких случаях результату присваивается значение машинного но-

ля?

5.По какому признаку определяется необходимость в коррекции ре-

зультата?

6.В каком случае результату присваивается значение одного из опе-

рандов с обратным знаком?

7.Каким образом возникает переполнение порядка при сложении-

вычитании?

8.Возможно ли исчезновение порядка при сложении-вычитании?

9.Почему при умножении анализ на исчезновение порядка выполня-

ется дважды?

10.Почему в |MG| может быть нарушение нормализации вправо не бо-

лее, чем на S разрядов?

11.Чем ОС блока мантисс при умножении отличается от ОС умноже-

ния дробей в прямом коде?

12.В каких случаях выполняется анализ на переполнение порядка при делении?

13.Почему при G0 ≥ 0 |MG| сдвигается вправо на S разрядов?

14.Чем ОС блока мантисс при делении отличается от ОС деления дро-

бей в прямом коде?

84

15.В каком случае результату деления присваивается значение машин-

ного ноля?

16.В каких случаях результату умножения присваивается значение ма-

шинного ноля?

85

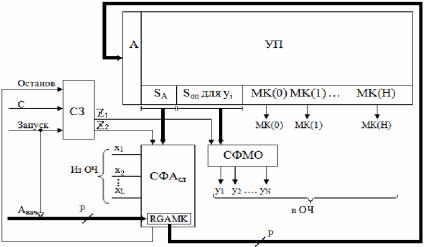

Глава 6. Проектирование УЧ АЛУ с программируемой логикой.

§6.1. Управляющая память.

Основу УЧ с программируемой логикой составляет управляющая па-

мять (УП), в качестве которой используется, например, перепрограммируе-

мое постоянное запоминающее устройство (ППЗУ).

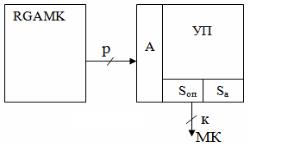

Пусть: Р –количество ячеек ППЗУ; р – количество разрядов в адресе ячейки ППЗУ, равное ]log2P[; к – количество разрядов в ячейке ППЗУ; τчт -

время чтения из УП содержимого одной ячейки, называемого микрокоман-

дой (МК).

Обозначение УП на структурных схемах представлено на рис. 6.1.

Рис. 6.1

В одной ячейке УП записывается одна МК. Адрес МК, т.е. номер ячей-

ки, в которой записана данная МК, подается на адресные входы А из регист-

ра адреса МК (RGAMK). При этом на выходах УП формируется с задержкой,

равной τчт , к-разрядный код МК, который включает в общем случае 2 поля:

операционное (Sоп) и адресное (Sa).

В Sоп кодируется информация об УС, формируемых в данном такте ра-

боты АЛУ. Различают два вида УС.

1) Импульсные УС микроопераций (МО) с длительностью τ, где τ -

длительность синхросигналов С. Обозначаются как y1, y2, …, yN и называют-

ся просто сигналами МО.

2) Потенциальные УС МО с длительностью, не меньшей такта Т, назы-

ваемые микроприказами. Обозначаются как МК(0), МК(1), …, МК(Н), где МК(j) означает j-ый разряд операционного поля МК, считываемой из УП.

86

Адресное поле Sa используется для передачи управления, или, иначе,

для формирования адреса следующей выполняемой МК (Асл). Используются различные способы адресации МК. Классическим способом является прину-

дительная адресация с двумя адресами в МК, когда Sa включает 3 поля:

Sа |

|

|

1 |

X |

m |

1 |

A1 |

p |

1 |

A2 |

p |

, |

|

||||||||||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

где А1 и А2 – адреса ячеек УП, Х-поле проверяемого ЛУ.

1.Безусловная передача управления (БПУ), когда Х=0, адрес А2 не использу-

ется, а Асл=А1, что соответствует записи в УП следующего участка в графе МП.

|

|

|

Sоп |

|

А2 |

|||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

у1, МК(0)/C |

с) |

у1, МК(0)/C |

Х = 0 |

А1 |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y2, у3/A1 |

А1) |

у2, у3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Здесь запись в поле первой операторной вершины означает, что УС y1 и

МК(0) записаны в Sоп ячейки с адресом С.

2.Условная передача управления (УПУ), когда Х = i, где i – номер ЛУ хi, про-

веряемого в данном такте. Тогда Асл равно либо А1, если хi = 0, либо A2, если xi = 1, что соответствует записи в УП следующего участка в графе МП.

y4/D

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

D) |

Sоп |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

y4 |

X= i |

A1 |

A2 |

|

|

|

|

xi |

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

/A1 /A2

Обозначим через Х= {x1, x2, …, xL} множество различных ЛУ, про-

веряемых в условных вершинах графа МП. Тогда количество разрядов в

поле Х |

l = ]log2(L+1)[. |

87

Перед началом выполнения МП в RGAMK записывается начальный адрес Анач (адрес первой выполняемой МК), и на выходах УП формируют-

ся разряды МК. Далее:

п.1. в течение такта выполняются МО, входящие в текущую МК;

п.2. в течение следующего такта формируется Асл и выполняется чтение из УП очередной МК.

В дальнейшем пункты 1) и 2) циклически повторяются вплоть до оконча-

ния МП.

§ 6.2. Схема УЧ с программируемой логикой.

Структурная схема УЧ с программируемой логикой включает схему запуска (СЗ), УП, схему формирования сигналов МО (СФМО) и схему формирования Асл(СФАсл) (рис. 6.2).

В схеме рис. 6.2. предполагается, что в Sоп выделяются отдельные поля для сигналов МО (Sоп для уi) и микроприказов [Sоп для МК(j)], при-

чем микроприказы кодируются горизонтально. Последнее означает, что для каждого микропри-

каза выделяется в соот-

ветствующем поле от-

дельный разряд, в кото-

ром записывается 1, ес-

ли данный микроприказ в данном такте должен быть сформирован.

Рис. 6.2.

Работа схемы на рис.6.2 начинается по сигналу «Запуск», по которому,

во-первых, в RGAMK записывается Анач, и на выходах УП формируются раз-

ряды первой МК; во-вторых, СЗ начинает циклически формировать два по-

следовательных сигнала z1 и z2, где z1: Формирование сигналов МО; z2: RGAMK: = Aсл. По окончании МП формируется сигнал «Останов» = (Асл =

88

Анач), то есть последняя выполняемая МК должна передавать управление по начальному адресу.

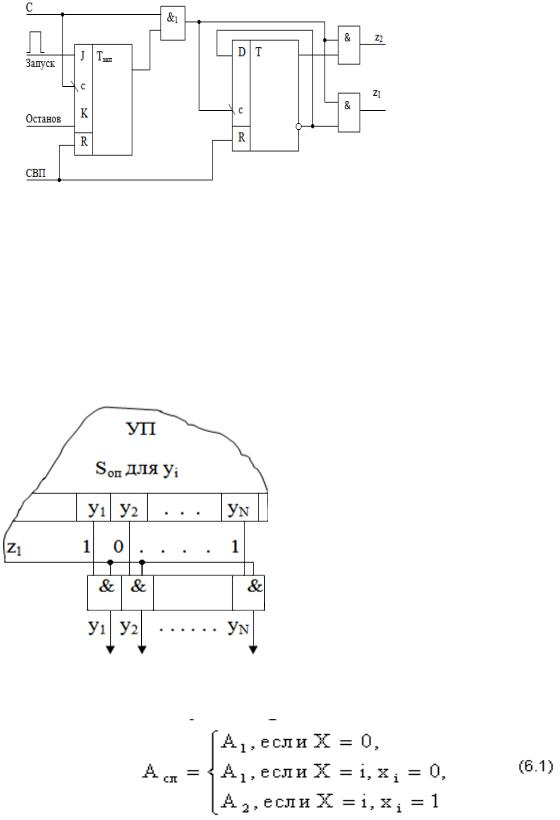

Схема запуска (рис. 6.3). |

До |

поступления |

сигнала |

|

«Запуск» триггер запуска |

||

|

Тзап |

и триггер Т |

должны |

|

находиться в состоянии О |

||

|

(CВП – сброс по включе- |

||

|

нию питания). По сигналу |

||

|

«Запуск» Тзап устанавлива- |

||

Рис. 6.3. |

ется в состояние 1, элемент И от- |

||

крывается, и синхросигналы начинают проходить в СЗ. Первый синхро-

сигнал появится на выходе z1, и по его окончании T: = 1; второй – на вы-

ходе z2, и по его окончании Т: = 0; третий – на выходе z1 и т.д. По оконча-

нии МП сигналом «Останов» Tзап сбрасывается, элемент И1 закрывается.

Сигнал z1 поступает в СФМО, которая при горизонтальном кодиро-

вании сигналов МО представляет собой набор из N элементов И (рис.6.4)

Пусть в Sоп для уi записаны сигналы МО y1 и yN. Тогда будут открыты лишь крайние элементы И, и сигнал z1 пройдет через них в качестве сигналов y1 и уN.

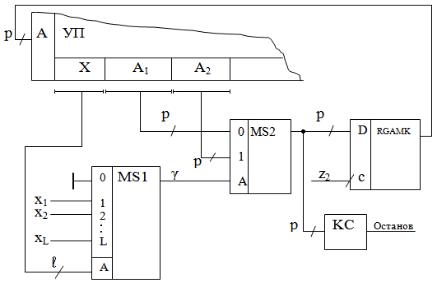

Сигнал z2 поступает в СФАсл. Пусть используется принудительная адресация с двумя адресами в МК, когда

Рис.6.4.

89

Схема такой адресации представлена на рис. 6.5. Здесь MS1 – одно-

разрядный мультиплексор из (L+1) направлений в одно, на адресные вхо-

ды которого подаются разряды поля Х. В результате

0, если Х 0 |

(6.2) |

|

|

|

|

|

, если Х i |

|

х i |

|

|

MS2 – p-разрядный мультиплексор из двух направлений в одно. На выходах MS2 формируются разряды A1, если γ = 0, и разряды А2, если γ =

1. Из сравнения (6.1) и (6.2) следует, что на выходах MS2 формируются разряды Асл, который и записывается в RGAMK по сигналу z2.

Рис. 6.5.

КС – комбинационная схема, формирующая сигнал «Останов» = (Aсл= Анач). Например, если Анач= 0, то КС – это р-входовый элемент ИЛИ

– НЕ.

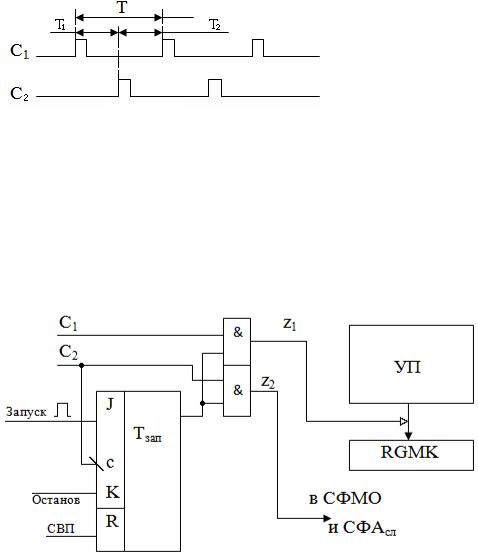

Совмещение в одном такте выполнения текущей МК с чтением из УП очередной МК.

Для этого, во-первых, в схему УЧ вводится буферный регистр МК

(RGAMK), в который по сигналу z1 записывается содержимое ячейки УП с адресом А, где А – адрес текущей МК [z1 :RGMK: = УП(А)]. Во-вторых,

90

в СЗ подаются 2 серии синхросигналов C1 и C2, сдвинутые по фазе (рис.

6.6).

Рис. 6.6.

Здесь такт Т делится на 2 микротакта T1 и Т2, где время Т1 выделяет-

ся на выполнение текущей МК в ОЧ, а Т2 – на чтение из УП очередной МК. При этом сигнал z2 подается одновременно в 2 схемы: в СФМО для формирования сигналов МО, входящих в текущую МК, и в СФАсл. В ре-

зультате схема запуска приобретает вид, показанный на рис. 6.7.

Рис. 6.7.

§6.3. Построение таблицы МК при различных способах адресации МК.

Таблица МК показывает содержимое ячеек УП при записи в них МП операции.

Построим таблицу МК для графа МП на рис. 6.8, считая, что:

-адресация - принудительная с 2 адресами в МК;

-кодирование УС - горизонтальное;

-останов по Анач = 0;

-количество ячеек УП Р = 16, т.е., р = ]log2P[ = 4.

В графе МП (рис. 6.8) (Н+1) = 2[МК(0), МК(1)]; N=6 (y1, y2,…, y6); L=4