- •Аннотация

- •1.1. Прототип модуля

- •1.2. Структура иерархического проекта

- •1.3. Иерархическое описание накапливающего сумматора.

- •Variable tr[8..1] : dff;

- •Variable tr[9..1] : dff;

- •Include "rg_a.Inc";

- •Include "add.Inc";

- •Include "rg_out.Inc";

- •Variable

- •2. Проектирование схем двоично-десятичной арифметики.

- •2.1. Двоично-десятичное представление схем.

- •2.2. Двоично-десятичный сумматор

- •Variable

- •2.2. Двоично-десятичный вычитатель

- •Variable

- •2.3. Двоично-десятичные счетчики

- •3.1. Способы задания абстрактных автоматов.

- •3.2. Описание работы автоматов на языке ahdl

- •Init, Working, Waiting, Resuming, Ending.

- •Variable

- •3.3. Проектирование счетчиков на базе абстрактных автоматов

- •Variable

- •4. Проектирование типовых схемотехнических узлов

- •Дешифратора

- •Считается, что одновременно может быть нажата только одна кнопка клавиатуры.

- •Variable

- •4.2. Схемы вычисления функций

- •4.3. Счетчики расхода, пробега

- •Variable

- •Variable

- •Include "t210.Inc";

- •Variable

- •4.4. Узлы обработки сигналов локаторов

- •Include "t210.Inc";

- •Variable

- •4.5. Часы, счетчики времени, календари

- •Variable

- •Variable

- •4.6. Частотомеры

- •Variable

- •4.7. Умножители

- •Input_b_is_constant)

- •5 Проектирование схем с магистральным вводом выводом данных

- •5.1 Правила работы с магистралью, арбитр.

- •Variable

- •5.2 Подготовка временных диаграмм.

- •5.3. Пример сумматора с магистральным вводом-выводом данных.

- •Variable

Variable tr[9..1] : dff;

BEGIN

TR[].(CLK,CLRn) = (CLK,!Reset);

TR[].D = D[];

OUT[] = TR[].Q;

END;

Модуль имеет входную шину данных D[9..1], тактовый вход CLK и вход сброса Reset. Выходные данные выводятся на шину OUT[9..1]. Запись информации в регистр осуществляется по положительному фронту сигнала CLK.

Регистр реализован на базе стандартных примитивов DFF.

По умолчанию на все входы подаются нулевые значения сигналов.

Головной файл накапливающего сумматора Accum.tdf, содержащий следующее текстовое описание:

Include "rg_a.Inc";

Include "add.Inc";

Include "rg_out.Inc";

SUBDESIGN ACCUM

( Din[8..1],CLK,Reset : INPUT;

Dout[9..1]: OUTPUT;

D[8..1] : OUTPUT;)

Variable

M_RG_A : RG_A;

M_ADD : ADD;

M_RG_OUT : RG_OUT;

BEGIN

M_RG_A.CLK = CLK;

M_RG_OUT.(CLK,Reset) = (CLK,Reset);

M_RG_A.D[] = Din[];

M_ADD.A[] = M_RG_A.OUT[];

M_ADD.B[] = M_RG_OUT.OUT[];

M_RG_OUT.D[] = M_ADD.OUT[];

Dout[] = M_RG_OUT.OUT[];

D[] = M_RG_A.OUT[];

END;

Головной модуль накапливающего сумматора имеет входную шину данных Din[8..1], на которую последовательно подаются слагаемые, входной тактовый сигнал CLK и сигнал сброса Reset. Накопленная сумма выдается на шину Dout[9..1]. Шина D[8..1], используется для контроля состояния входов сумматора.

Головной модуль накапливающего сумматора содержит три оператора INCLUDE со ссылками на прототипы модулей.

Прототипы модулей представлены следующим образом.

Прототип модуля Rg_a.tdf

FUNCTION rg_a (d[8..1], clk, reset)

RETURNS (out[8..1]);

Прототип модуля add.tdf

FUNCTION add (a[8..1], b[9..1])

RETURNS (out[9..1]);

Прототип модуля Rg_out.tdf

FUNCTION rg_out (d[9..1], clk, reset)

RETURNS (out[9..1]);

Отметим, что прототипы модулей формируются автоматически с помощью команды Create Default Include File (меню File) выполняемой в окне текстового редактора пакета MAX+PLUSII и содержащего описание модуля.

В представленном примере модулям присвоены символические имена M_RG_A, M_ADD и M_RG_OUT и обращение к ним идёт как к переменным.

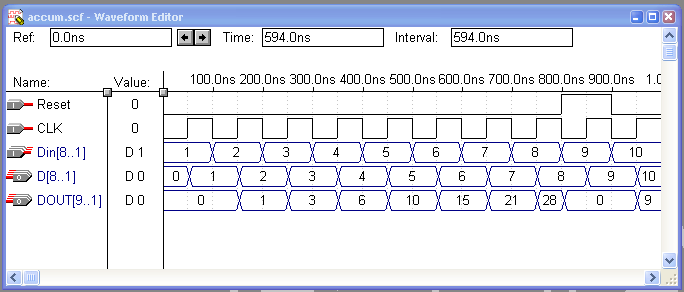

Временная диаграмма работы накапливающего сумматора имеет вид, представленный на рис 1.3.2

Рис 1.3.2. Временная диаграмма работы накапливающего сумматора.

1.4. Пользовательские библиотеки элементов MAX+PLUSII

В состав САПР MAX+PLUSII входят следующие пользовательские библиотеки

Библиотека примитивов (prim), включающая в свой состав простые, элементы такие как

элементарные логические элементы;

внешние выводы;

контакты земли питания;

D и Т триггеры;

JK триггеры;

Триггеры LACH;

RS триггеры.

Библиотека мегафункций (mf), включающая сложные функциональные узлы, представленные либо на уровне примитивов либо на уровне не параметризуемого поведенческого описания на языке AHDL. В состав мегафункций входят такие элементы как:

счетчики;

мультиплексоры;

компараторы;

элементы стандартной серии 7400, включающие богатый набор таких элементов как сумматоры, регистры, шифраторы, кодеры и т.д.

Отметим, что элементы из библиотеки мегафункций при необходимости можно скорректировать. Правда, для этого целесообразно сделать его копию, сохранив её под другим именем.

Библиотека логически параметризуемых функции (mega-lpm), включающая сложные функциональные узлы, представленные на уровне параметризуемых модулей, содержащих поведенческое описания на языке AHDL. В состав mega-lpm библиотеки входят следующие типовые модули.

счетчики;

сумматоры;

умножители;

делители;

компараторы;

регистры;

блоки памяти;

декодеры;

мультиплексоры.

При заказе параметризуемого модуля Вам предложат задать такие параметры модуля как разрядность, наличие сигнала сброса, тип счетчика и т.д.

Билиотека типовых схемных решений (.edif), включающая широкий набор различных стандартных, схемных решений, логических узлов. Эта библиотека разработана специалистами фирмы Altera, для облегчения перевода в базис MAX+PLUSII проектов, разработанных ранее в базисе стандартных серий микросхем.

Отметим что в формате EDIF может быть представлена самая разнообразная информация, включая графическое описание, описание тестовых векторов, список цепей (net list), параметры и т.д.