- •Аннотация

- •1.1. Прототип модуля

- •1.2. Структура иерархического проекта

- •1.3. Иерархическое описание накапливающего сумматора.

- •Variable tr[8..1] : dff;

- •Variable tr[9..1] : dff;

- •Include "rg_a.Inc";

- •Include "add.Inc";

- •Include "rg_out.Inc";

- •Variable

- •2. Проектирование схем двоично-десятичной арифметики.

- •2.1. Двоично-десятичное представление схем.

- •2.2. Двоично-десятичный сумматор

- •Variable

- •2.2. Двоично-десятичный вычитатель

- •Variable

- •2.3. Двоично-десятичные счетчики

- •3.1. Способы задания абстрактных автоматов.

- •3.2. Описание работы автоматов на языке ahdl

- •Init, Working, Waiting, Resuming, Ending.

- •Variable

- •3.3. Проектирование счетчиков на базе абстрактных автоматов

- •Variable

- •4. Проектирование типовых схемотехнических узлов

- •Дешифратора

- •Считается, что одновременно может быть нажата только одна кнопка клавиатуры.

- •Variable

- •4.2. Схемы вычисления функций

- •4.3. Счетчики расхода, пробега

- •Variable

- •Variable

- •Include "t210.Inc";

- •Variable

- •4.4. Узлы обработки сигналов локаторов

- •Include "t210.Inc";

- •Variable

- •4.5. Часы, счетчики времени, календари

- •Variable

- •Variable

- •4.6. Частотомеры

- •Variable

- •4.7. Умножители

- •Input_b_is_constant)

- •5 Проектирование схем с магистральным вводом выводом данных

- •5.1 Правила работы с магистралью, арбитр.

- •Variable

- •5.2 Подготовка временных диаграмм.

- •5.3. Пример сумматора с магистральным вводом-выводом данных.

- •Variable

Variable

RA[7..0] : DFF;

RB[7..0] : DFF;

TT[7..0] : TRI;

CN[1..0] : DFF;

BEGIN

CN[].CLK= !CLK;

RA[].D=M[];

RB[].D=M[];

CASE CN[].Q IS

WHEN 2 => CN[].D=0;

WHEN OTHERS => CN[].D=CN[].Q+1;

END CASE;

RA[].CLK=CN0.Q & CLK;

RB[].CLK=CN1.Q & CLK;

TT[].OE= !CN0.Q & !CN1.Q;

TT[].IN=RA[].Q+RB[].Q;

M[7..0]=TT[].OUT;

DONE=!CN0.Q & !CN1.Q;

END;

В данном описании сумматора введены следующие переменные

RA[7..0] – регистр хранения слагаемого A;

RB[7..0] – регистр хранения слагаемого B;

TT[7..0] – восемь двунаправленных элементов ввода-вывода типа TRI;

CN[1..0] – регистр управляющего счётчика CN.

Управляющий счётчик считает от «0» до «2». Организуется работа счётчика в соответствующем операторе CASE, обеспечивающем переход счёта из состояния «2» в состояние «0».

При состоянии счётчика равном «1», происходит запись данных из магистрали M[] в регистр RA, а при состоянии равном «2», соответственно в регистр RB.

Управление этими процессами задаётся операторами:

RA[].CLK=CN0.Q & CLK;

RB[].CLK=CN1.Q & CLK;

RA[].D=M[];

RB[].D=M[];

При состоянии управляющего счётчика CN равном «0», происходит вычисление суммы и выдача результата на магистраль M[], что, в свою очередь, определяется операторами:

TT[].IN=RA[].Q+RB[].Q;

TT[].OE= !CN0.Q & !CN1.Q;

M[7..0]=TT[].OUT;

При состоянии управляющего счётчика CN равном «0», происходит также формирование сигнала завершения работы DONE с помощью оператора

DONE=!CN0.Q & !CN1.Q;

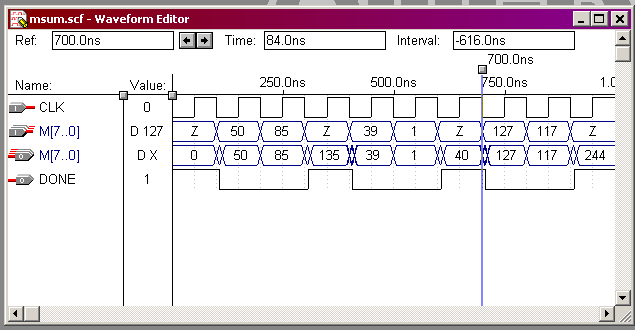

Рассмотрим пример временной диаграммы работы восьмиразрядного сумматора с магистральным вводом-выводом данных. Данная диаграмма представлена на рис 5.2.2.

Рис 5.2.2. Пример временной диаграммы работы восьмиразрядного сумматора с магистральным вводом-выводом данных. Магистраль M на диаграмме представлена и как вход и как выход.

На примере, представленном на рис 5.2.2. производятся три цикла работы сумматора, на которых выполняются следующие примеры:

50+85=135

39+1=40

127+117=244.

Как и положено, операция сложения выполняется три такта. На каждом третьем такте входная шина M переводится в состояние «Z». На этом же такте на выходную шину M выдает результат суммирования

При внимательном изучении временной диаграммы можно заметить переходные процессы при переключении входных сигналов магистрали в состояние Z и обратно. Это происходит из-за ненулевого времени переключения элемента TRI из активного состояния в состояние Z и обратного переключения. В течении короткого времени этих переключений на магистраль находится либо в состоянии «Z» (элемент TRI ещё не включился и на магистрале нет активного сигнала) , либо состоянии «Х» (элемент TRI ещё не успел выключился и на магистрале находятся два активных источника сигнала).

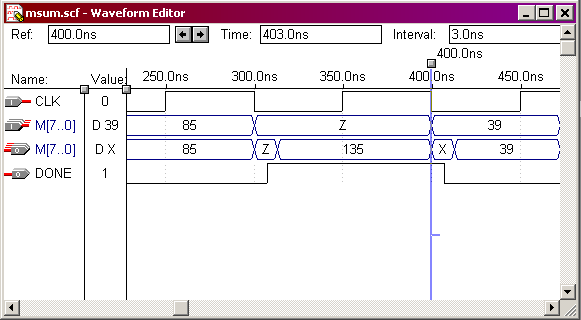

Более подробно эти переходные процессы показаны на рис 5.2.3.

Рис 5.2.3. Более подробно эти переходные процессы переключения состояний магистрали.

Такие переходные процессы являются кратковременными и не влияют на правильную работу аппаратура.

Литература

1. Комолов Д.А., Мяльк Р.А., Зобенко А.А., Филиппов А.С. Системы автоматизированного проектирования фирмы Altera MAX+PLUS II и QUARTUS II. –Москва: ИП РадиоСофт, 2002-352с.: ил.

2. Антонов А.П., ЯЗЫК ОПИСАНИЯ ЦИФРОВЫХ УСТРОЙСТВ AlteraHDL. Москва, РадиоСофт, 2002. – 224с.

3. Стешенко В.Б. ПЛИС фирмы ALTERA: проектирование устройств обработки сигналов. – Москва: ДОДЭКА, 2002 – 128с.