- •Аннотация

- •1.1. Прототип модуля

- •1.2. Структура иерархического проекта

- •1.3. Иерархическое описание накапливающего сумматора.

- •Variable tr[8..1] : dff;

- •Variable tr[9..1] : dff;

- •Include "rg_a.Inc";

- •Include "add.Inc";

- •Include "rg_out.Inc";

- •Variable

- •2. Проектирование схем двоично-десятичной арифметики.

- •2.1. Двоично-десятичное представление схем.

- •2.2. Двоично-десятичный сумматор

- •Variable

- •2.2. Двоично-десятичный вычитатель

- •Variable

- •2.3. Двоично-десятичные счетчики

- •3.1. Способы задания абстрактных автоматов.

- •3.2. Описание работы автоматов на языке ahdl

- •Init, Working, Waiting, Resuming, Ending.

- •Variable

- •3.3. Проектирование счетчиков на базе абстрактных автоматов

- •Variable

- •4. Проектирование типовых схемотехнических узлов

- •Дешифратора

- •Считается, что одновременно может быть нажата только одна кнопка клавиатуры.

- •Variable

- •4.2. Схемы вычисления функций

- •4.3. Счетчики расхода, пробега

- •Variable

- •Variable

- •Include "t210.Inc";

- •Variable

- •4.4. Узлы обработки сигналов локаторов

- •Include "t210.Inc";

- •Variable

- •4.5. Часы, счетчики времени, календари

- •Variable

- •Variable

- •4.6. Частотомеры

- •Variable

- •4.7. Умножители

- •Input_b_is_constant)

- •5 Проектирование схем с магистральным вводом выводом данных

- •5.1 Правила работы с магистралью, арбитр.

- •Variable

- •5.2 Подготовка временных диаграмм.

- •5.3. Пример сумматора с магистральным вводом-выводом данных.

- •Variable

Variable

MT[3..0] : DFF;

ST[3..0] : DFF;

HT[3..0]: DFF;

BEGIN

MT[].CLK=CLK;

ST[].CLK=!MT[3].Q;

HT[].CLK=!ST[3].Q;

MT[].CLRN=RN;

ST[].CLRN=RN;

HT[].CLRN=RN;

CASE MT[].Q IS

WHEN 9 => MT[].D=0;

WHEN OTHERS => MT[].D=MT[].Q+1;

END CASE;

CASE ST[].Q IS

WHEN 9 => ST[].D=0;

WHEN OTHERS => ST[].D=ST[].Q+1;

END CASE;

CASE HT[].Q IS

WHEN 9 => HT[].D=0;

WHEN OTHERS => HT[].D=HT[].Q+1;

END CASE;

M[] = MT[].Q;

S[] = ST[].Q;

H[] = HT[].Q;

END;

Схема счётчика имеет следующие входные и выходные сигналы.

СLK – входная частота;

RN – асинхронный сброс;

H[3..0] – выходы старшей тетрады частоты;

S[3..0] – выходы средней тетрады счётчика;

M[3..0] – выходы младшей тетрады счётчика.

В состав счетчика входит регистр младшей тетрады MT[3..0], средней тетрады MS[3..0], и старшей - MH[3..0].

Условия двоично-десятичного счёта отрабатываются с помощью группы операторов CASE, расписанных отдельно для каждой тетрады.

Нижеприведённые операторы обеспечивают отработку сигналов переноса между тетрадами:

MT[].CLK=CLK;

ST[].CLK=!MT[3].Q;

HT[].CLK=!ST[3].Q;

Младшая тетрада считает импульсы непосредственно входной частоты, средняя – импульсы переноса младшей, а старшая – импульсы переноса средгнй.

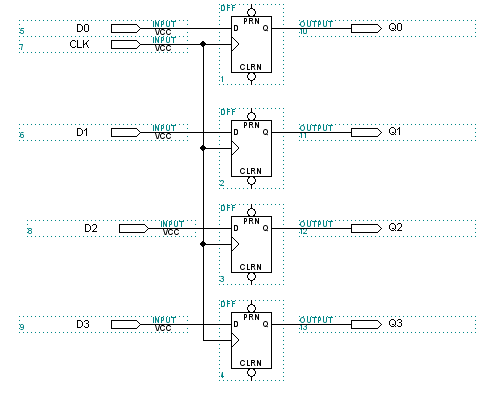

Регистр для хранения результатов подсчёта частоты реализован на базе триггеров DFF. Схема четырехразрядного регистра представлена на рис 4.6.2.

Рис 4.6.2. Схема четырехразрядного буферного регистра.

Схема регистра имеет следующие входные и выходные сигналы.

СLK – входной тактовый сигнал записи данных;

D0[3..0] – входные сигнала регистра;

Q0[3..0] – выходные сигналы регистра;

По положительному фронту входного тактового сигнала СLK регистр записывает входные данные, заданные на шине D0[3..0] и хранит их вплоть до прихода очередного импульса тактового сигнала.

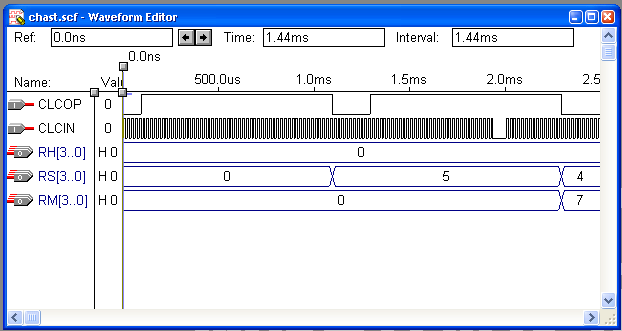

Временная диаграмма работы частотомера приведена на рис 4.6.3

Рис 4.6.3. Временная диаграмма работы частотомера.

На рисунке 4.5.3. представлен пример работы частотомера при измерении входной частоты 50 Мгц. Во втором цикле измерения из входного потока «вырезали» три рабочих такта, поэтому в результате получилась частота 47 МГц.

Частотомеры, работающие по методу определения периода.

В завершение обзора частотомеров рассмотрим структурную схему частотомеров, реализующих метод изменения периода. Как было отмечено выше, реализация данных частотомеров требует наличия операции деления.

Рассмотрим структурную схему частотомера, работающего по методу измерения периода, представленную на рис 4.6.4.

Делитель

F

N

F/n

F

Счётчик импульсов CLC

опорной

частоты

ENA

RN

C LC

LC

D

Выходной C

регистр. Q

Блок

управления

F I

I

Значение частоты

Рис 4.6.4. Структурная схема частотомера, работающего по методу измерения периода.

Схема, представленная на рис 4.6.4. работает следующим образом:

Блок управления по положительному фронту входной неизвестной частоты FI сбрасывает счётчик импульсов опорной частоты (подаёт короткий импульс на вход RN) и подаёт сигнал разрежения счёта на вход ENA. При приходе отрицательного фронта FI работа счётчика блокируется (на вход ENA подаётся запрещающий сигнал). Кроме того в этот же момент на вход записи информации С выходного регистра подаётся сигнал записи длительностью достаточной для выполнения процедуры деления.

На выход выходного регистра Q выдаётся последняя рассчитанная частота.