схемотехника_131017

.pdf

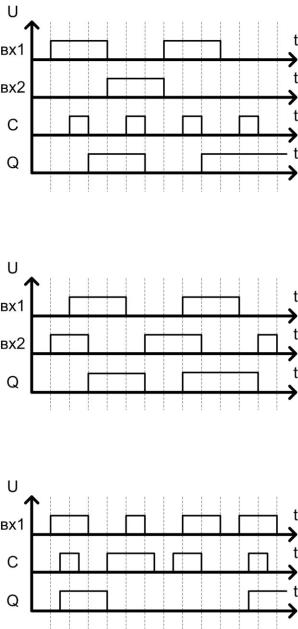

8. Определите тип триггера по приведённой временной диаграмме и нарисуйте его УГО. Укажите функциональное назначение пронумерованных входов.

9. Определите тип триггера по приведённой временной диаграмме и нарисуйте его УГО. Укажите функциональное назначение пронумерованных входов.

10. Определите тип триггера по приведённой временной диаграмме и нарисуйте его УГО. Укажите функциональное назначение пронумерованных входов.

11. Определите тип триггера по приведённой временной диаграмме и нарисуйте его УГО. Укажите функциональное назначение пронумерованных входов.

71

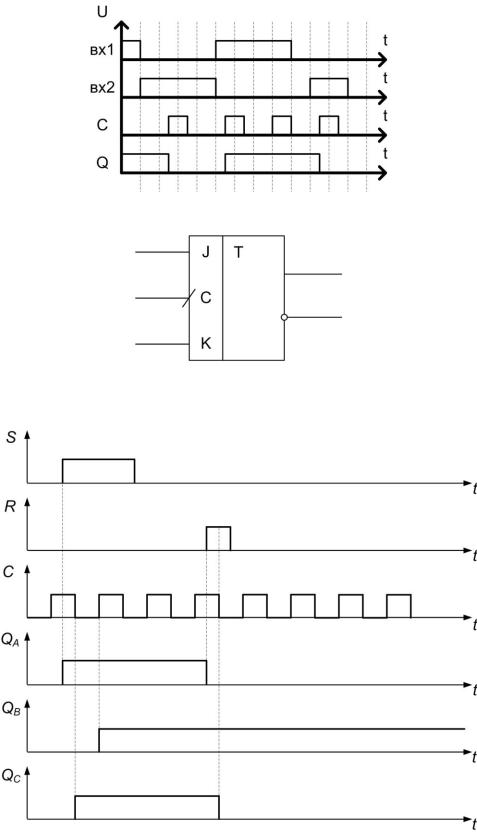

12.Имеется синхронный JK-триггер с динамическим управлением. Организуйте на его основе синхронные D-, T- и RS- триггеры.

13.Какая из приведённых диаграмм работы тактируемого RS- триггера соответствует синхронизации задним фронтом. Приведите условное обозначение такого триггера.

72

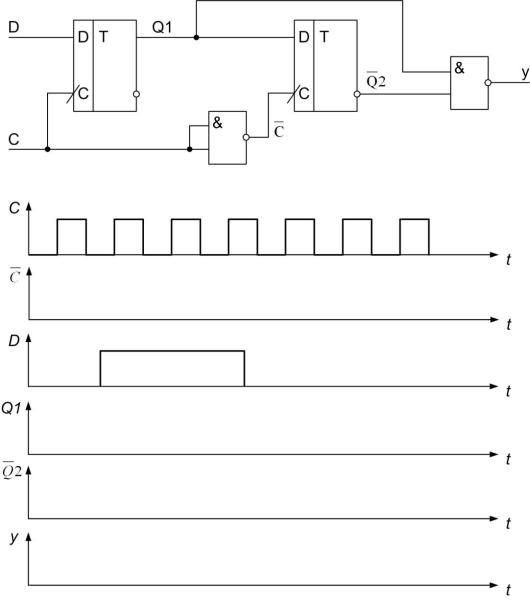

14. Приведите временные диаграммы на выходе приведённой ниже схемы при нахождении переключателя П в положении A и в положении B.

15. С помощью временных диаграмм определить назначение схемы, приведенной на рисунке:

73

74

4. ФУНКЦИОНАЛЬНЫЕ УЗЛЫ ПОСЛЕДОВАТЕЛЬНОСТНОГО ТИПА

4.1. Регистры

Регистры – последовательностное устройство, предназначенное для записи, хранения и (или) сдвига данных, представленных в виде многоразрядного двоичного кода.

В общем случае регистры могут выполнять следующие операции над словами:

1.Установка регистра в нулевое состояние.

2.Запись входных данных в последовательном коде.

3.Запись входных данных в параллельном коде.

4.Хранение данных.

5.Сдвиг хранимого кодового слова вправо или влево.

6.Выдача хранимых данных в последовательном коде.

7.Выдача хранимых данных в параллельном коде.

Любой n-разрядный регистр состоит из n однотипных ячеек – раз-

рядных схем, выходной сигнал каждой из которых ассоциируется с весовым коэффициентом соответствующего разряда двоичного кода, при этом каждая разрядная схема состоит из триггера, как элемента памяти и некоторой комбинационной схемы, преобразующей входные воздействия и состояния триггера в выходные сигналы регистра.

Регистры могут быть классифицированы по различным признакам. Рассмотрим основные из них.

По способу приёма и выдачи информации регистры подразде-

ляют на:

параллельные (статические) – приём и выдача данных производится по всем разрядам;

последовательные (сдвигающие) – данные записываются в последовательном коде разряд за разрядом; тактирующие сигналы перемещают слово в разрядной сетке;

параллельно-последовательные (универсальные) – имеют входы и выходы для приёма и выдачи данных, как последовательным, так и параллельным кодом.

По количеству каналов передачи переменных регистры делят на однофазные и парафазные. В парафазном регистре данные передаются по двум каналам – в прямом и инверсном коде.

75

По способу тактирования регистры разделяют на однотактные и многотактные. Первые управляются одной последовательностью синхроимпульсов, вторые – несколькими последовательностями синхроимпульсов.

4.1.1. Последовательные сдвигающие регистры

Последовательные сдвигающие регистры представляют собой цепи последовательных взаимосвязанных одноразрядных схем. В регистрах данного типа коды принимаются и выдаются разряд за разрядом. Тактирующие сигналы перемещают слово в разрядной сетке.

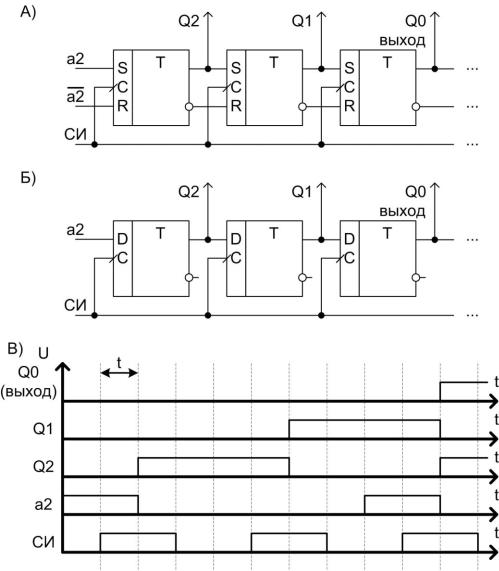

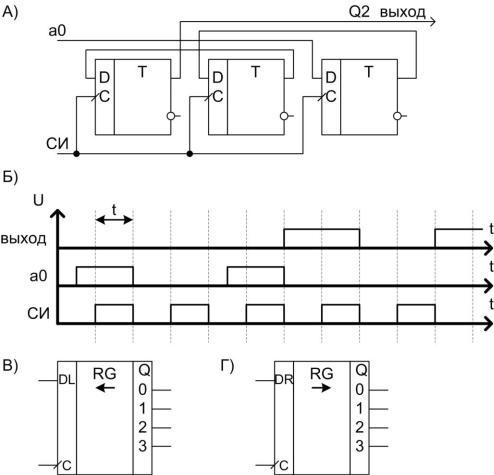

Рис. 4.1. DSR: А – парафазная функциональная схема; Б – однофазная функциональная схема; В – временные диаграммы работы; t – время переключения триггера

76

Воднотактных последовательных регистрах со сдвигом вправо (DSR – Data Serial Right) слово сдвигается на один разряд вправо при поступлении синхросигнала (рис. 4.1).

Воднотактных последовательных регистрах со сдвигом влево (DSR – Data Serial Left) слово сдвигается на один разряд влево при поступлении синхросигнала (рис. 4.2).

Рис. 4.2. DSL: А – функциональная схема; Б – временные диаграммы работы; t – время переключения триггера; В – УГО DSL; Г – УГО DSR

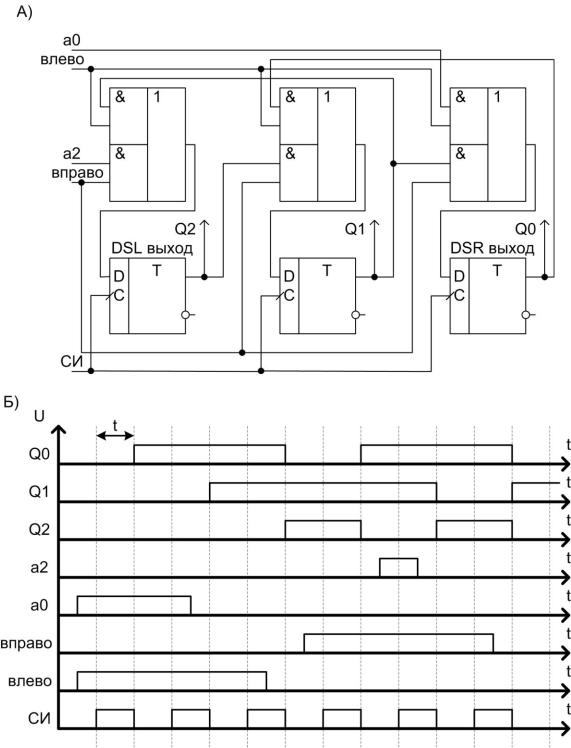

Реверсивный однотактный последовательный регистр совмещает в себе DSR и DSL. Для управления, записи и выдачи данных в разных режимах (сдвиг вправо или влево) имеются раздельные входы и выходы (рис. 4.3). Команды «влево» и «вправо» одновременно не подаются.

77

Рис. 4.3. Реверсивный регистр: А – функциональная схема; Б – временные диаграммы работы; t – время переключения триггера

В сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры, управляемые уровнем, поскольку некоторые триггеры могут за время

78

действия разрешающего уровня синхросигнала переключиться неоднократно, что недопустимо.

4.1.2. Регистровые файлы

ИС регистровых ЗУ входят в состав большинства серий, в том числе и микропроцессорные комплекты БИС в качестве регистров общего назначения (РОН) и многорежимных буферных регистров (МБР).

ЗУ на регистрах, построенных по схеме произвольного доступа, позволяет обращаться к любому регистру для записи или чтения данных. Они реализуются на параллельных регистрах. В отличие от них регистровое ЗУ с последовательным доступом для обращения к нужной информации требует перебор адреса в сторону увеличения или уменьшения адресов.

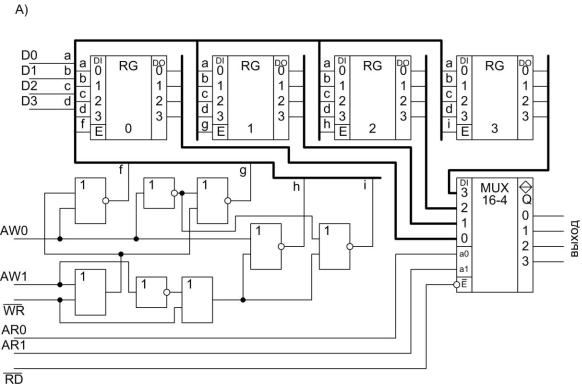

В качестве примера рассмотрим функциональную схему ИС ИР26 серии 1533 (рис. 4.4).

79

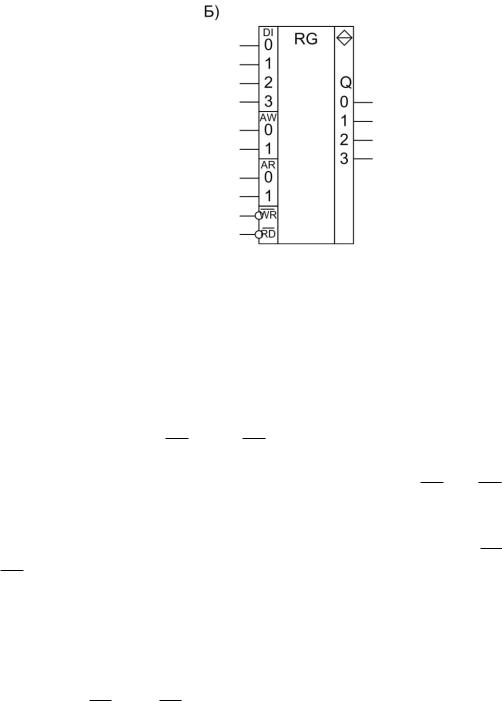

Рис. 4.4. К1533ИР26: А – функциональная схема; Б – УГО

В данной ИС можно хранить четыре 4-х разрядных слова. Возможна независимая и одновременная запись одного слова и чтения другого по разным адресам. Информационные входы регистров соединены параллельно, входы адресов записи AW1 и AW0 дают четыре комбинации, каждая из которых разрешает занести данные, присутствующие на входах D0-3, в соответствующий регистр (AW1 – старший разряд адреса, AW0 – младший). Запись данных осуществляется при наличии логического нуля на входе WR . При WR 1 – запись не производится. Рассматриваемая ИС асинхронная, т.е. запись и считывание данных осуществляется при наличии логического нуля на входах WR и RD соответственно. Считывание информации производят установкой адреса нужного регистра на адресных входах AR1 и AR0, где AR1 – старший разряд, а AR0 – младший. Чтение данных возможно только при RD 0 , если RD 1, то выходы ИС переводятся в высокоимпедансное состояние. Разделение адресов AW и AR позволяет одновременно осуществлять запись в один регистр, а считывать с другого. Таким образом, ИС может работать в четырёх режимах: запись слова в любой из регистров, считывание слова из любого регистра, одновременная запись слова в любой из регистров и считывание слова из любого регистра, хранение информации при WR 1 и RD 1.

Такие ИС допускают объединение одноимённых входов и выходов для наращивания разрядности регистров и объёмов. Поскольку выходные каскады с 3-мя состояниями, то одноимённые выходы отдельных ИС просто объединяются (до 128 ИС). При наращивании разрядности хранимых слов в ИС соединяют параллельно входы разрешения и адресации нескольких ИС, выходы которых в совокупности дают единое информационное слово.

80