- •«Кузбасский государственный технический университет

- •1. Описание цикла лабораторных работ

- •2. Описание архитектуры учебной эвм

- •2.1. Программные модели для изучения архитектуры эвм

- •2.2 Структура учебной эвм

- •2.3. Представление данных в модели

- •2.4. Система команд учебной эвм

- •2.5. Состояния и режимы работы учебной эвм

- •2.6. Интерфейс пользователя

- •2.7. Микрокомандный уровень учебной эвм

- •2.8. Внешние устройства

- •2.8.1 Общая характеристика моделей внешних устройств

- •2.8.2 Контроллер клавиатуры

- •2.8.3. Дисплей

- •2.8.4. Блок таймеров

- •2.8.5. Тоногенератор

- •2.8.6. Блок индикаторов

- •2.9. Подсистема прерываний

- •2.9. Программная модель кэш-памяти

- •2.10. Программная модель alu-1

- •2.10.1. Общие сведения о программной модели alu-1

- •2.10.2. Операционный автомат

- •2.10.3. Регистры операционного автомата

- •2.10.4. Арифметико-логический блок

- •2.10.5. Блок сдвигателя

- •2.10.6. Счетчик

- •2.10.7. Микрооперации и логические условия

- •2.10.8. Управляющий автомат с программируемой логикой (уапл)

- •3. Лабораторные работы

- •3.1. Лабораторная работа № 1. Основы работы с программной моделью учебной эвм

- •3.1.1. Цель работы

- •3.1.2. Общие положения

- •3.1.3. Последовательность выполнения работы

- •3.1.4. Варианты заданий

- •3.1.5. Пример выполнения работы

- •3.1.6. Содержание отчета

- •3.2.3. Последовательность выполнения работы

- •3.2.4. Варианты заданий

- •3.2.5. Пример выполнения работы

- •3.2.6. Содержание отчета

- •3.3.3. Последовательность выполнения работы

- •3.3.4. Варианты заданий

- •3.3.5. Пример выполнения работы

- •3.3.6. Содержание отчета

- •3.3.7. Задания повышенной сложности

- •3.3.8. Контрольные вопросы

- •3.4. Лабораторная работа №4. Подпрограммы и стек

- •3.4.1. Цель работы

- •3.4.2. Общие положения

- •3.4.3. Последовательность выполнения работы

- •3.4.4. Варианты заданий

- •3.4.5. Пример выполнения работы

- •3.4.6. Содержание отчета

- •3.5.5 Пример выполнения работы

- •3.5.4 Варианты заданий

- •3.5.5 Пример выполнения работы

- •3.5.6. Содержание отчета

- •3.5.7. Задания повышенной сложности

- •3.5.8. Контрольные вопросы

- •3.6. Лабораторная работа №6. Программирование внешних устройств

- •3.6.1. Цель работы

- •3.6.2. Общие положения

- •3.6.3. Последовательность выполнения работы

- •3.6.4. Содержание отчета

- •3.6.5. Варианты заданий

- •3.6.6. Пример выполнения работы

- •3.6.7. Задания повышенной сложности

- •3.6.8. Контрольные вопросы

- •3.7. Лабораторная работа №7. Принципы работы кэш-памяти

- •3.7.1. Цель работы

- •3.7.2. Общие положения

- •3.7.3. Последовательность выполнения работы

- •3.7.4. Содержание отчета

- •3.7.5. Варианты заданий

- •3.7.6. Контрольные вопросы

- •Рекомендуемая литература

- •Лабораторный практикум по архитектуре эвм и систем

- •230201 «Информационные системы и технологии»

1. Описание цикла лабораторных работ

Данный цикл лабораторных работ построен в расчете на изучение взаимодействия устройств в структуре ЭВМ с помощью программной модели некоторой абстрактной ЭВМ, которая программируется на языке ассемблера.

Предлагаемая для использования программная модель учебной ЭВМ отражает все основные особенности системы команд и структур современных простых ЭВМ, включает в себя помимо процессора и памяти, модели нескольких типичных внешних устройств. Модель позволяет изучить основы программирования на низком уровне, вопросы взаимодействия различных уровней памяти в составе ЭВМ и способы взаимодействия процессора с внешними устройствами.

Цикл лабораторных работ включает в себя работы, ориентированные на первичное знакомство с архитектурой процессора, системой команд, способами адресации, организацией кэш-памяти и системы ввода-вывода и основными приемами программирования на машинно-ориентированном языке.

2. Описание архитектуры учебной эвм

2.1. Программные модели для изучения архитектуры эвм

Современные процессоры и операционные системы не слишком благоприятная среда для изучения архитектуры ЭВМ. Одним из решений этой проблемы является разработка программных моделей учебной ЭВМ, которые с одной стороны, достаточно просты, чтобы обучаемый мог освоить базовые понятия архитектуры (система команд, командный цикл, способы адресации, способы взаимодействия процессора с памятью и внешними устройствами), с другой стороны – архитектурные особенности модели должны соответствовать тенденциям развития современных ЭВМ.

Программная модель позволяет реализовать доступ к различным элементам ЭВМ, обеспечивая удобство и наглядность. С другой стороны, модель позволяет игнорировать те особенности реальной ЭВМ, которые на данном уровне рассмотрения не являются существенными. Данная модель предназначена для начальных этапов изучения архитектуры ЭВМ. Именно этим объясняется использование в модели десятичной системы счисления для кодирования команд и представления данных.

2.2 Структура учебной эвм

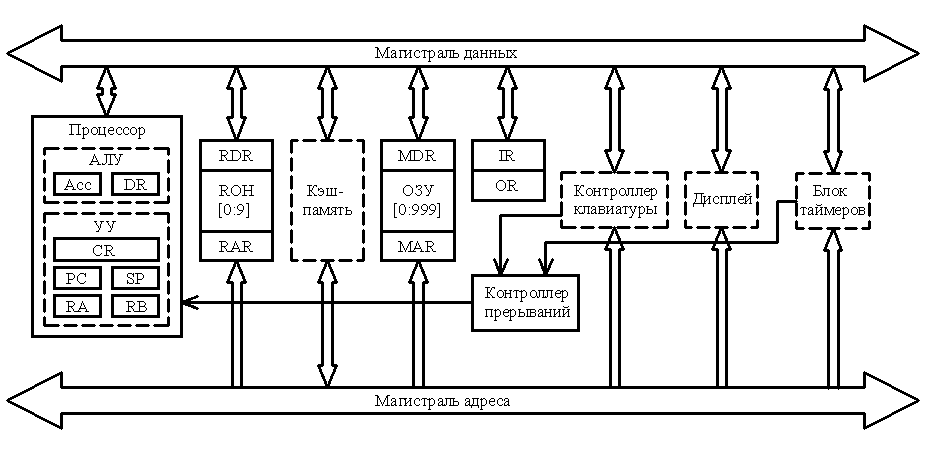

Моделируемая ЭВМ включает процессор, оперативную (ОЗУ) и сверхоперативную память, устройства ввода (УВв) и устройство вывода (УВыв). Процессор в свою очередь состоит из центрального устройства управления (УУ), арифметико-логического устройства (АЛУ) и системных регистров (CR, PC, SP, и др.). Структурная схема ЭВМ показана на рис. 2.1.

В ячейках ОЗУ хранятся команды и данные. Емкость ОЗУ составляет 1000 ячеек. По сигналу MWr выполняется запись содержимого регистра данных (MDR) в ячейку памяти с адресом, указанным в регистре адреса (MAR). По сигналу MRd происходит считывание – содержимое ячейки памяти с адресом, содержащимся в MAR, передается в MDR.

Сверхоперативная память с прямой адресацией содержит десять регистров общего назначения (РОН) R0 – R9. Доступ к ним осуществляется (аналогично доступу к ОЗУ) через регистры RAR и RDR.

АЛУ осуществляет выполнение одной операции, определяемой кодом операции (COP), над содержимым аккумулятора (Acc) и регистра операнда (DR). Результат операции всегда помещается в Асс.

В модели ЭВМ предусмотрены внешние устройства двух типов. Во-первых, это регистры IR и OR, которые могут обмениваться с аккумулятором с помощью безадресных команд IN (Acc := IR) и OUT (OR :=Acc). Во-вторых, это набор моделей внешних устройств, которые могут подключаться к системе и взаимодействовать с ней в соответствии с заложенными в моделях алгоритмами.

УУ осуществляет выборку команд из ОЗУ в последовательности, определяемой порядком выполнения команд или командами передачи управления; выборку из ОЗУ операндов, задаваемых адресами команды; инициирование выполнения операции, предписанной командой; останов или переход к выполнению следующей команды.

В состав УУ входят следующие элементы:

• РС – счетчик адреса команды, содержащий адрес текущей команды;

• СR – регистр команды, содержащий код команды;

• RB – регистр базового адреса, содержащий базовый адрес;

• SP – указатель стека, содержащий адрес верхушки стека;

• RA – регистр адреса, содержащий дополнительный адрес при косвенной адресации.