- •«Кузбасский государственный технический университет

- •1. Описание цикла лабораторных работ

- •2. Описание архитектуры учебной эвм

- •2.1. Программные модели для изучения архитектуры эвм

- •2.2 Структура учебной эвм

- •2.3. Представление данных в модели

- •2.4. Система команд учебной эвм

- •2.5. Состояния и режимы работы учебной эвм

- •2.6. Интерфейс пользователя

- •2.7. Микрокомандный уровень учебной эвм

- •2.8. Внешние устройства

- •2.8.1 Общая характеристика моделей внешних устройств

- •2.8.2 Контроллер клавиатуры

- •2.8.3. Дисплей

- •2.8.4. Блок таймеров

- •2.8.5. Тоногенератор

- •2.8.6. Блок индикаторов

- •2.9. Подсистема прерываний

- •2.9. Программная модель кэш-памяти

- •2.10. Программная модель alu-1

- •2.10.1. Общие сведения о программной модели alu-1

- •2.10.2. Операционный автомат

- •2.10.3. Регистры операционного автомата

- •2.10.4. Арифметико-логический блок

- •2.10.5. Блок сдвигателя

- •2.10.6. Счетчик

- •2.10.7. Микрооперации и логические условия

- •2.10.8. Управляющий автомат с программируемой логикой (уапл)

- •3. Лабораторные работы

- •3.1. Лабораторная работа № 1. Основы работы с программной моделью учебной эвм

- •3.1.1. Цель работы

- •3.1.2. Общие положения

- •3.1.3. Последовательность выполнения работы

- •3.1.4. Варианты заданий

- •3.1.5. Пример выполнения работы

- •3.1.6. Содержание отчета

- •3.2.3. Последовательность выполнения работы

- •3.2.4. Варианты заданий

- •3.2.5. Пример выполнения работы

- •3.2.6. Содержание отчета

- •3.3.3. Последовательность выполнения работы

- •3.3.4. Варианты заданий

- •3.3.5. Пример выполнения работы

- •3.3.6. Содержание отчета

- •3.3.7. Задания повышенной сложности

- •3.3.8. Контрольные вопросы

- •3.4. Лабораторная работа №4. Подпрограммы и стек

- •3.4.1. Цель работы

- •3.4.2. Общие положения

- •3.4.3. Последовательность выполнения работы

- •3.4.4. Варианты заданий

- •3.4.5. Пример выполнения работы

- •3.4.6. Содержание отчета

- •3.5.5 Пример выполнения работы

- •3.5.4 Варианты заданий

- •3.5.5 Пример выполнения работы

- •3.5.6. Содержание отчета

- •3.5.7. Задания повышенной сложности

- •3.5.8. Контрольные вопросы

- •3.6. Лабораторная работа №6. Программирование внешних устройств

- •3.6.1. Цель работы

- •3.6.2. Общие положения

- •3.6.3. Последовательность выполнения работы

- •3.6.4. Содержание отчета

- •3.6.5. Варианты заданий

- •3.6.6. Пример выполнения работы

- •3.6.7. Задания повышенной сложности

- •3.6.8. Контрольные вопросы

- •3.7. Лабораторная работа №7. Принципы работы кэш-памяти

- •3.7.1. Цель работы

- •3.7.2. Общие положения

- •3.7.3. Последовательность выполнения работы

- •3.7.4. Содержание отчета

- •3.7.5. Варианты заданий

- •3.7.6. Контрольные вопросы

- •Рекомендуемая литература

- •Лабораторный практикум по архитектуре эвм и систем

- •230201 «Информационные системы и технологии»

2.10. Программная модель alu-1

2.10.1. Общие сведения о программной модели alu-1

Программная модель ALU-1 включает в себя две основные части: операционный автомат и управляющий автомат.

Операционный автомат предназначен для реализации арифметических операций над двоичными числами с фиксированной запятой в формате 1 байт без знака (от 0 до 255) или 1 байт со знаком (от – 127 до + 127), а также логических операций над двоичными векторами длиной 1 байт.

2.10.2. Операционный автомат

Операционный автомат позволяет реализовывать следующие арифметические операции:

• сложение без знака;

• вычитание без знака;

• сложение/вычитание в прямом, обратном или дополнительном кодах;

• умножение (без знака или со знаком);

• деление (без знака или со знаком) способами с восстановлением остатка или без его восстановления.

Также операционный автомат может выполнять поразрядные логические операции:

• конъюнкция;

• дизъюнкция;

• неравнозначность;

• инверсия.

Результатом всех арифметических и логических операций (кроме умножения) является байт в формате исходных данных. Произведение может быть представлено в 8- или 16-разрядном формате.

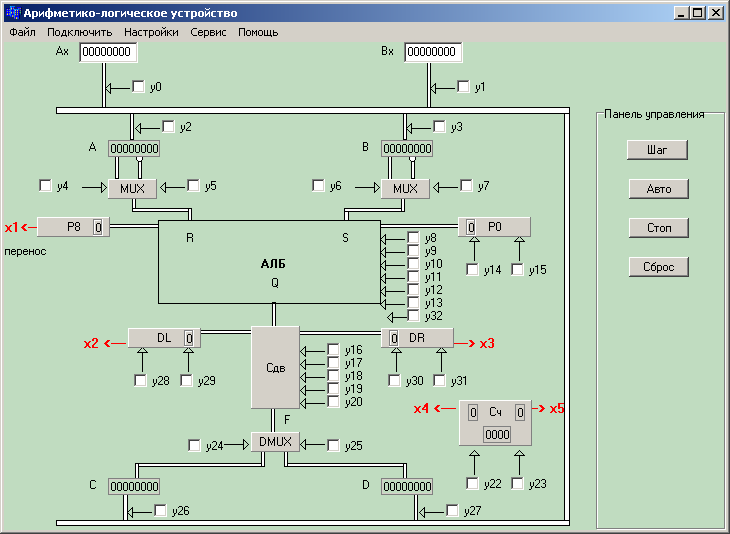

На рис. 2.18 показано главное окно операционного автомата.

Рис. 2.18. Операционный автомат ALU-1

Операционный автомат включает в себя следующие элементы:

• входные 8-разрядные регистры Ax и Bx, позволяющие загружать исходные операнды;

• 8-разрядные регистры операндов;

• 8-разрядный арифметико-логический блок (АЛБ) с триггерами входного P0 и выходного P8 переносов;

• два 8-разрядных двухвходовых мультплексора MUX, выбирающие для входов АЛБ прямые или инверсные значения регистров A и B;

• блок сдвигателя, который включает 8-разрядный реверсивный комбинационный сдвигатель Сдв и два триггера DL и DR, формирующие/принимающие данные слева и справа;

• два 8-разрядных регистра результата C и D;

• демультиплексор DMUX, передающий значение вектора F[7;0] с выхода блока;

• 8-разрядную шину, роль источников на которую могут играть регистры Ax, Bx, C, D, а приемников – A и/или B;

2.10.3. Регистры операционного автомата

Входные и выходные регистры операционного автомата Ax, Bx, C, D могут быть подключены к шине или отключены от нее. В данной модели шину можно рассматривать как набор из восьми переменных (по числу элементов памяти в регистрах), каждая из которых может принимать три значения: «неактивна», «0», «1».

2.10.4. Арифметико-логический блок

Арифметико-логический блок (АЛБ) включает комбинационную схему функционального преобразователя и два элемента памяти: триггеры P0 и P8.

Состояние триггера P0 может быть установлено с помощью микроопераций y14 и y15 и участвует в микрооперациях сложения (вычитания) в качестве значения переноса (заема) младшего разряда. Триггер P8 в арифметических операциях принимает значение переноса (заема), возникающего из старшего разряда, а в логических микрооперациях всегда устанавливается в «0». Остальные микрооперации сохраняют ранее установленное значение P8.

2.10.5. Блок сдвигателя

Блок сдвигателя включает в себя собственно реверсивный сдвигатель Сдв на один разряд и два триггера данных («слева» DL и «справа» DR). Каждый из этих триггеров может устанавливаться в произвольные значения микрооперациями (y28, y29, y30, y31) и принимать значение разрядов, теряемых при сдвиге вектора Q. Текущие значения триггеров могут рассматриваться как значения логических условий x2 и x3.