- •Features

- •Pin Configurations

- •Disclaimer

- •Overview

- •Block Diagram

- •AT90S8535 Compatibility

- •Pin Descriptions

- •Port A (PA7..PA0)

- •Port B (PB7..PB0)

- •Port C (PC7..PC0)

- •Port D (PD7..PD0)

- •RESET

- •XTAL1

- •XTAL2

- •AVCC

- •AREF

- •Resources

- •AVR CPU Core

- •Introduction

- •Architectural Overview

- •Status Register

- •Stack Pointer

- •Interrupt Response Time

- •SRAM Data Memory

- •Data Memory Access Times

- •EEPROM Data Memory

- •EEPROM Read/Write Access

- •I/O Memory

- •Clock Systems and their Distribution

- •Clock Sources

- •Default Clock Source

- •Crystal Oscillator

- •External RC Oscillator

- •External Clock

- •Timer/Counter Oscillator

- •Idle Mode

- •Power-down Mode

- •Power-save Mode

- •Standby Mode

- •Extended Standby Mode

- •Analog-to-Digital Converter

- •Analog Comparator

- •Brown-out Detector

- •Internal Voltage Reference

- •Watchdog Timer

- •Port Pins

- •Resetting the AVR

- •Reset Sources

- •Power-on Reset

- •External Reset

- •Brown-out Detection

- •Watchdog Reset

- •Watchdog Timer

- •Timed Sequences for Changing the Configuration of the Watchdog Timer

- •Safety Level 0

- •Safety Level 1

- •Safety Level 2

- •Interrupts

- •I/O-Ports

- •Introduction

- •Configuring the Pin

- •Reading the Pin Value

- •Unconnected pins

- •Alternate Port Functions

- •Alternate Functions of Port A

- •Alternate Functions Of Port B

- •Alternate Functions of Port C

- •Alternate Functions of Port D

- •External Interrupts

- •8-bit Timer/Counter0 with PWM

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Internal Clock Source

- •Prescaler Reset

- •External Clock Source

- •16-bit Timer/Counter1

- •Overview

- •Registers

- •Definitions

- •Compatibility

- •Counter Unit

- •Input Capture Unit

- •Input Capture Trigger Source

- •Noise Canceler

- •Using the Input Capture Unit

- •Output Compare Units

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •8-bit Timer/Counter2 with PWM and Asynchronous Operation

- •Overview

- •Registers

- •Definitions

- •Counter Unit

- •Output Compare Unit

- •Force Output Compare

- •Modes of Operation

- •Normal Mode

- •Fast PWM Mode

- •Phase Correct PWM Mode

- •Timer/Counter Prescaler

- •Slave Mode

- •Master Mode

- •Data Modes

- •USART

- •Overview

- •Clock Generation

- •External Clock

- •Synchronous Clock Operation

- •Frame Formats

- •Parity Bit Calculation

- •USART Initialization

- •Sending Frames with 5 to 8 Data Bits

- •Sending Frames with 9 Data Bits

- •Parity Generator

- •Disabling the Transmitter

- •Receiving Frames with 5 to 8 Data Bits

- •Receiving Frames with 9 Data Bits

- •Receiver Error Flags

- •Parity Checker

- •Disabling the Receiver

- •Flushing the Receive Buffer

- •Asynchronous Data Recovery

- •Using MPCM

- •Write Access

- •Read Access

- •Two-wire Serial Interface

- •Features

- •TWI Terminology

- •Electrical Interconnection

- •Transferring Bits

- •START and STOP Conditions

- •Address Packet Format

- •Data Packet Format

- •Overview of the TWI Module

- •SCL and SDA Pins

- •Bit Rate Generator Unit

- •Bus Interface Unit

- •Address Match Unit

- •Control Unit

- •TWI Register Description

- •Using the TWI

- •Transmission Modes

- •Master Transmitter Mode

- •Master Receiver Mode

- •Slave Receiver Mode

- •Slave Transmitter Mode

- •Miscellaneous States

- •Analog Comparator

- •Analog Comparator Multiplexed Input

- •Features

- •Operation

- •Starting a Conversion

- •Differential Gain Channels

- •Changing Channel or Reference Selection

- •ADC Input Channels

- •ADC Voltage Reference

- •ADC Noise Canceler

- •Analog Input Circuitry

- •ADC Accuracy Definitions

- •ADC Conversion Result

- •ADLAR = 0

- •ADLAR = 1

- •Boot Loader Features

- •Application Section

- •Boot Loader Lock Bits

- •Performing a Page Write

- •Using the SPM Interrupt

- •Setting the Boot Loader Lock Bits by SPM

- •Reading the Fuse and Lock Bits from Software

- •Preventing Flash Corruption

- •Simple Assembly Code Example for a Boot Loader

- •Fuse Bits

- •Latching of Fuses

- •Signature Bytes

- •Calibration Byte

- •Signal Names

- •Parallel Programming

- •Enter Programming Mode

- •Chip Erase

- •Programming the Flash

- •Programming the EEPROM

- •Reading the Flash

- •Reading the EEPROM

- •Programming the Lock Bits

- •Reading the Signature Bytes

- •Reading the Calibration Byte

- •Serial Downloading

- •Data Polling Flash

- •Data Polling EEPROM

- •Electrical Characteristics

- •Absolute Maximum Ratings*

- •DC Characteristics

- •External Clock Drive Waveforms

- •External Clock Drive

- •Two-wire Serial Interface Characteristics

- •ADC Characteristics

- •Active Supply Current

- •Idle Supply Current

- •Standby Supply Current

- •Pin Pullup

- •Pin Driver Strength

- •Internal Oscillator Speed

- •Register Summary

- •Instruction Set Summary

- •Ordering Information

- •Packaging Information

- •Errata

- •Changes from Rev. 2502E-12/03 to Rev. 2502G-06/04

- •Changes from Rev. 2502E-12/03 to Rev. 2502F-06/04

- •Changes from Rev. 2502D-09/03 to Rev. 2502E-12/03

- •Changes from Rev. 2502C-04/03 to Rev. 2502D-09/03

- •Changes from Rev. 2502B-09/02 to Rev. 2502C-04/03

- •Changes from Rev. 2502A-06/02 to Rev. 2502B-09/02

- •Table of Contents

ATmega8535(L)

Two-wire Serial Interface Characteristics

Table 112 describes the requirements for devices connected to the Two-wire Serial Bus. The ATmega8535 Two-wire Serial Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 127.

Table 112. Two-wire Serial Bus Requirements

Symbol |

Parameter |

|

|

|

|

|

|

Condition |

Min |

|

Max |

Units |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIL |

Input Low Voltage |

|

|

|

|

|

|

|

|

-0.5 |

|

0.3 VCC |

V |

|

VIH |

Input High Voltage |

|

|

|

|

|

|

|

|

0.7 VCC |

VCC + 0.5 |

V |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1) |

Hysteresis of Schmitt Trigger Inputs |

|

|

|

|

|

|

(2) |

– |

V |

|||

Vhys |

|

|

|

|

|

0.05 VCC |

||||||||

|

(1) |

Output Low Voltage |

|

|

|

|

|

3 mA sink current |

0 |

|

0.4 |

V |

||

VOL |

|

|

|

|

|

|

||||||||

|

(1) |

Rise Time for both SDA and SCL |

|

|

|

|

|

20 + 0.1C |

(3)(2) |

300 |

ns |

|||

tr |

|

|

|

|

|

|

|

|

|

|

b |

|

|

|

|

(1) |

Output Fall Time from V |

IHmin |

to V |

ILmax |

|

|

10 pF < C < 400 pF(3) |

20 + 0.1C |

(3)(2) |

250 |

ns |

||

tof |

|

|

|

|

|

|

b |

|

b |

|

|

|||

tSP(1) |

Spikes Suppressed by Input Filter |

|

|

|

|

|

0 |

|

50(2) |

ns |

||||

Ii |

Input Current each I/O Pin |

|

|

|

|

0.1VCC < Vi < 0.9VCC |

-10 |

|

10 |

µA |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

C (1) |

Capacitance for each I/O Pin |

|

|

|

|

|

|

– |

|

10 |

pF |

|||

|

i |

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

SCL |

SCL Clock Frequency |

|

|

|

f |

CK |

(4) > max(16f , 250kHz)(5) |

0 |

|

400 |

kHz |

||

|

|

|

|

|

|

|

|

SCL |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

fSCL ≤ 100 kHz |

VCC – 0.4V |

1000ns |

Ω |

||

|

|

|

|

|

|

|

|

|

|

|

---------------------------- |

------------------- |

||

Rp |

Value of Pull-up resistor |

|

|

|

|

|

|

|

|

3mA |

|

Cb |

|

|

|

|

|

|

|

|

fSCL > 100 kHz |

VCC – 0.4V |

300ns |

Ω |

|||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

---------------------------- |

--------------- |

||

|

|

|

|

|

|

|

|

|

|

|

3mA |

|

Cb |

|

tHD;STA |

Hold Time (Repeated) START Condition |

|

|

|

fSCL ≤ 100 kHz |

4.0 |

|

– |

µs |

|||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

fSCL > 100 kHz |

0.6 |

|

– |

µs |

|||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

f |

|

≤ 100 kHz(6) |

4.7 |

|

– |

µs |

tLOW |

Low Period of the SCL Clock |

|

|

|

SCL |

|

|

|

|

|

||||

|

|

|

fSCL > 100 kHz(7) |

1.3 |

|

– |

µs |

|||||||

|

|

|

|

|

|

|

|

|

||||||

tHIGH |

High Period of the SCL clock |

|

|

|

|

fSCL ≤ 100 kHz |

4.0 |

|

– |

µs |

||||

|

|

|

|

fSCL > 100 kHz |

0.6 |

|

– |

µs |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

tSU;STA |

Set-up Time for a Repeated START |

|

|

|

fSCL ≤ 100 kHz |

4.7 |

|

– |

µs |

|||||

Condition |

|

|

|

|

|

|

fSCL > 100 kHz |

0.6 |

|

– |

µs |

|||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

tHD;DAT |

Data hoLd Time |

|

|

|

|

|

|

fSCL ≤ 100 kHz |

0 |

|

3.45 |

µs |

||

|

|

|

|

|

|

fSCL > 100 kHz |

0 |

|

0.9 |

µs |

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSU;DAT |

Data Setup Time |

|

|

|

|

|

|

fSCL ≤ 100 kHz |

250 |

|

– |

ns |

||

|

|

|

|

|

|

fSCL > 100 kHz |

100 |

|

– |

ns |

||||

|

|

|

|

|

|

|

|

|

|

|||||

tSU;STO |

Setup Time for STOP Condition |

|

|

|

|

fSCL ≤ 100 kHz |

4.0 |

|

– |

µs |

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

fSCL > 100 kHz |

0.6 |

|

– |

µs |

||||||

|

|

|

|

|

|

|

|

|

|

|||||

tBUF |

Bus Free Time between a STOP and START |

|

|

|

fSCL ≤ 100 kHz |

4.7 |

|

– |

µs |

|||||

Condition |

|

|

|

|

|

|

fSCL > 100 kHz |

1.3 |

|

– |

µs |

|||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Notes: 1. In ATmega8535, this parameter is characterized and not 100% tested.

2.Required only for fSCL > 100 kHz.

3.Cb = capacitance of one bus line in pF.

259

2502K–AVR–10/06

4.fCK = CPU clock frequency.

5.This requirement applies to all ATmega8535 Two-wire Serial Interface operation. Other devices connected to the Two-wire Serial Bus need only obey the general fSCL requirement.

6.The actual low period generated by the ATmega8535 Two-wire Serial Interface is (1/fSCL - 2/fCK), thus fCK must be greater than 6 MHz for the low time requirement to be strictly met at fSCL = 100 kHz.

7.The actual low period generated by the ATmega8535 Two-wire Serial Interface is (1/fSCL - 2/fCK), thus the low time requirement will not be strictly met for fSCL > 308 kHz when fCK = 8 MHz. Still, ATmega8535 devices connected to the bus may communicate at full speed (400 kHz) with other ATmega8535 devices, as well as any other device with a proper tLOW acceptance margin.

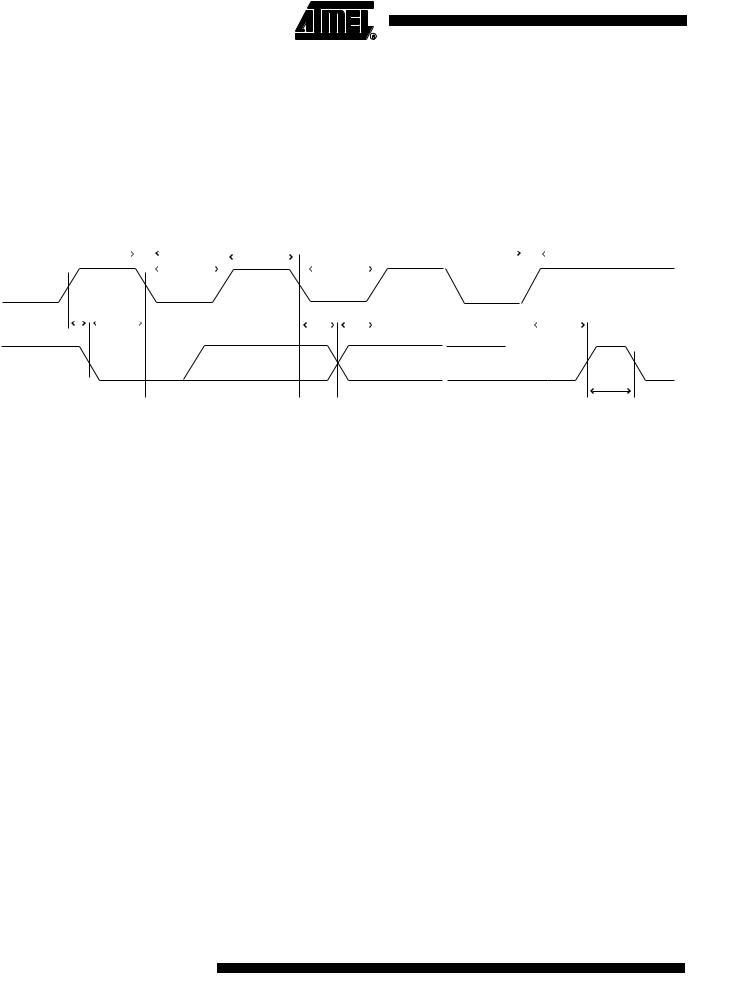

Figure 127. Two-wire Serial Bus Timing

|

|

|

|

|

|

|

|

|

|

tof |

|

|

tHIGH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tr |

||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

SCL |

|

|

|

|

|

|

|

|

|

tLOW |

|

|

|

|

tLOW |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSU;STA |

|

|

|

|

|

|

|

tHD;STA |

|

tHD;DAT |

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

SDA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SU;DAT |

|

|

|

|

tSU;STO |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tBUF

260 ATmega8535(L)

2502K–AVR–10/06

ATmega8535(L)

ATmega8535(L)

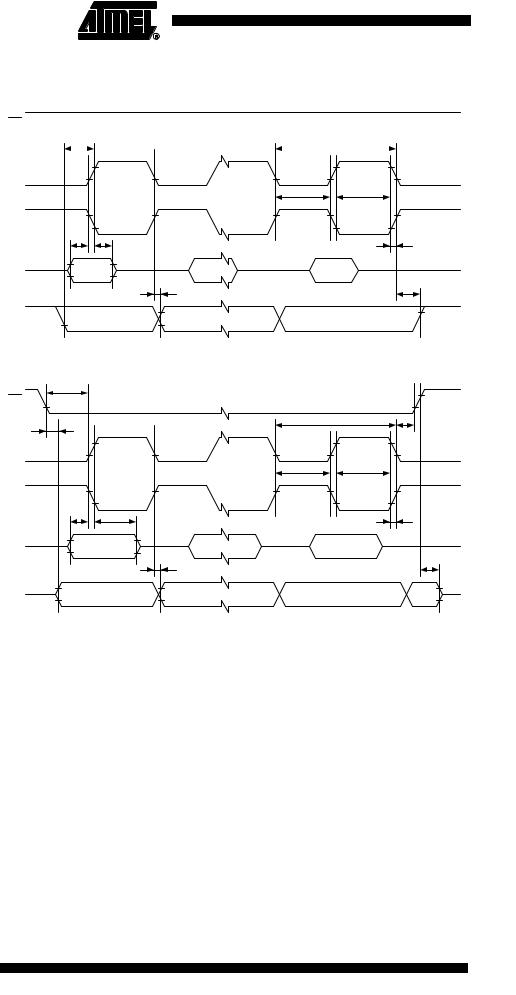

SPI Timing

Characteristics

See Figure 128 and Figure 129 for details.

Table 113. SPI Timing Parameters

|

|

Description |

Mode |

Min |

Typ |

Max |

|

|||

|

|

|

|

|

|

|

|

|||

1 |

|

SCK period |

Master |

|

See Table 59 |

|

|

|||

|

|

|

|

|

|

|

|

|||

2 |

|

SCK high/low |

Master |

|

50% duty cycle |

|

|

|||

|

|

|

|

|

|

|

|

|||

3 |

|

Rise/Fall time |

Master |

|

3.6 |

|

|

|||

|

|

|

|

|

|

|

|

|||

4 |

|

Setup |

Master |

|

10 |

|

|

|||

|

|

|

|

|

|

|

|

|||

5 |

|

Hold |

Master |

|

10 |

|

|

|||

|

|

|

|

|

|

|

ns |

|||

6 |

|

Out to SCK |

Master |

|

5 • tSCK |

|

||||

7 |

|

SCK to out |

Master |

|

10 |

|

|

|||

|

|

|

|

|

|

|

|

|||

8 |

|

SCK to out high |

Master |

|

10 |

|

|

|||

|

|

|

|

|

|

|

|

|||

9 |

|

SS low to out |

Slave |

|

15 |

|

|

|||

|

|

|

|

|

|

|

|

|||

10 |

|

SCK period |

Slave |

4 • tck |

|

|

|

|||

11 |

|

SCK high/low |

Slave |

2 • tck |

|

|

|

|||

12 |

|

Rise/Fall time |

Slave |

|

|

1.6 |

ns |

|||

|

|

|

|

|

|

|

|

|||

13 |

|

Setup |

Slave |

10 |

|

|

|

|||

|

|

|

|

|

|

|

|

|||

14 |

|

Hold |

Slave |

10 |

|

|

|

|||

|

|

|

|

|

|

|

|

|||

15 |

|

SCK to out |

Slave |

|

15 |

|

ns |

|||

|

|

|

|

|

|

|

|

|

|

|

16 |

|

SCK to |

|

high |

Slave |

20 |

|

|

||

|

SS |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||

17 |

|

|

high to tri-state |

Slave |

|

10 |

|

|

||

SS |

|

|

|

|||||||

18 |

|

SS low to SCK |

Slave |

2 • tck |

|

|

|

|||

261

2502K–AVR–10/06

Figure 128. SPI Interface Timing Requirements (Master Mode)

SS

6 |

|

1 |

SCK |

|

|

|

|

(CPOL = 0) |

|

|

|

|

|

|

2 |

2 |

|

SCK |

|

|

|

|

(CPOL = 1) |

|

|

|

|

4 |

5 |

|

3 |

|

MISO |

MSB |

... |

LSB |

|

(Data Input) |

||||

|

|

|

||

|

|

7 |

8 |

|

MOSI |

MSB |

... |

LSB |

|

(Data Output) |

||||

|

|

|

Figure 129. SPI Interface Timing Requirements (Slave Mode)

18 |

|

|

|

|

|

SS |

|

|

|

|

|

9 |

|

|

10 |

16 |

|

|

|

|

|

||

SCK |

|

|

|

|

|

(CPOL = 0) |

|

|

|

|

|

|

|

11 |

11 |

|

|

SCK |

|

|

|

|

|

(CPOL = 1) |

|

|

|

|

|

13 |

14 |

|

|

12 |

|

MOSI |

MSB |

... |

LSB |

|

|

(Data Input) |

|

||||

|

|

|

|

||

|

|

15 |

|

17 |

|

MISO |

MSB |

... |

LSB |

X |

|

(Data Output) |

|||||

|

|

|

|

262 ATmega8535(L)

2502K–AVR–10/06