Slides_OEVM_final

.pdf

Лекция 3. Структура и функции

центрального процессора

Арифметико-логическое устройство (АЛУ)

Структура АЛУ

Жесткая |

Магистральная |

Комбинационные схемы жестко |

БОД и регистры |

распределены между всеми |

взаимодействуют между собой |

регистрами |

с помощью магистралей (шин) |

81

© С. Г. Мосин, 2007

Лекция 3. Структура и функции

центрального процессора

АЛУ с жесткой структурой

РгА через логическую схему Л_А соединен со входом А.

Л_В обеспечивает

коммутацию выходного регистра РгC с регистром РгВ.

© С. Г. Мосин, 2007

РгA |

Л_B |

Л_A |

РгB |

A |

B |

|

C |

|

РгC |

|

82 |

Лекция 3. |

Структура и функции |

|

|||

|

центрального процессора |

||||

АЛУ с магистральной структурой |

|

|

|||

Мультиплексоры А |

|

Рг1 |

А |

|

|

и В обеспечивают |

|

|

|

|

|

|

|

|

|

|

|

выбор любого |

|

С |

Рг2 |

|

|

регистра Ргi в |

|

. |

|

|

|

|

|

|

|

||

|

|

. |

|

|

|

качестве операнда. |

|

. |

|

|

|

|

РгN |

В |

|

||

Демультиплексор |

|

|

|

||

С обеспечивает |

|

|

Блок регистров |

|

|

запись результата |

|

|

|

УС |

АЛУ |

в любой регистр. |

|

|

|

||

|

|

|

|

|

|

© С. Г. Мосин, 2007 |

|

|

|

|

83 |

|

|

|

|

|

|

Лекция 3. Структура и функции

центрального процессора

Арифметико-логическое устройство (АЛУ) Затраты времени на выполнение операции

Жесткая структура |

Магистральная структура |

T = tв + tоп + tc |

T = tв + tоп + tc + tMUX + t DMX |

tв – длительность выборки операнда из регистра,

tоп – длительность операции, tc – длительность сохранения результата в регистре, tMUX – задержка мультиплексора, tDMX – задержка демультиплексора.

84

© С. Г. Мосин, 2007

Лекция 3. |

Структура и функции |

|

||||||||

|

центрального процессора |

|

||||||||

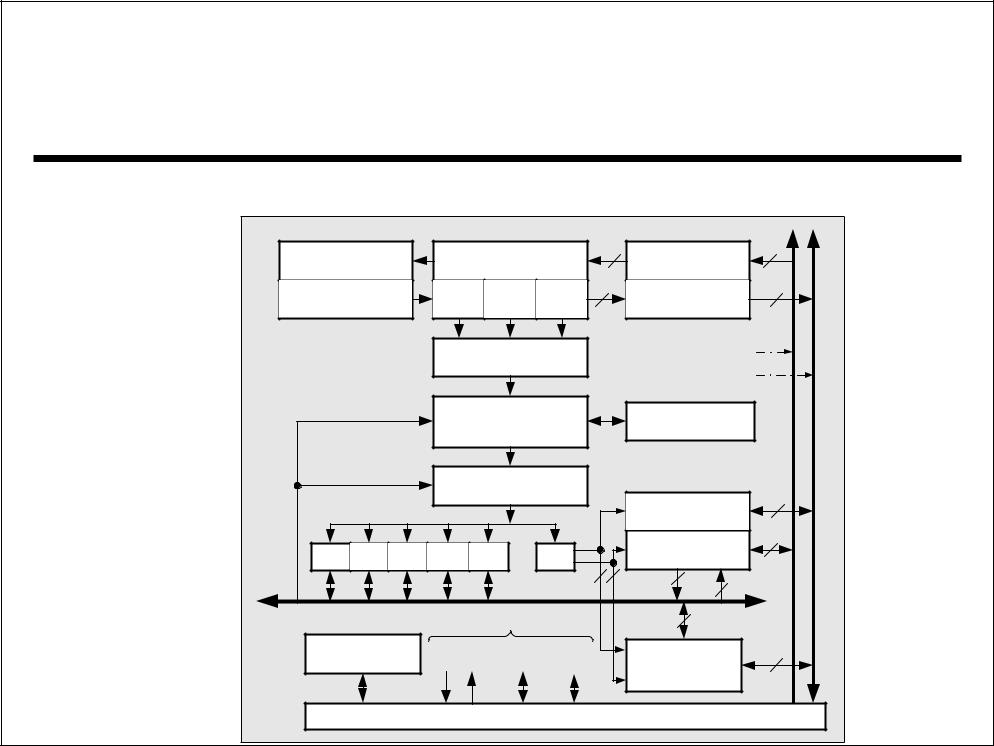

Структура процессора Intel P6 |

|

|

|

|

|

|

||||

|

|

|

|

Команды |

|

Команды |

|

|||

|

Блок предсказания |

Блок выборки |

256 |

Кэш-память |

64 |

|

||||

|

ветвлений |

декодирования |

|

|

команд (L1) |

|

|

|||

|

ВТВ |

DC1 DC2 |

DC3 |

|

Блок трансляции |

|

|

|||

|

31 |

адреса (TLB) |

36 |

|

||||||

|

|

|

|

|

|

|||||

|

Микрокоманды |

|

|

|

|

|

|

Адрес |

|

|

|

|

Блок распределения Адрес |

|

|

ШК |

|

||||

|

|

регистров (RAT) |

|

|

|

ШД |

|

|||

|

|

|

|

|

|

|

|

|

||

|

|

Блок изменения |

|

Блок регистров |

|

|

||||

|

|

последовательности |

|

|

|

|||||

|

|

|

замещения (RRF) |

|

||||||

|

|

команд (ROB) |

|

|

||||||

|

|

|

|

|

|

|

|

|||

|

|

Блок распределения |

|

|

|

|

Адрес |

|

||

|

|

команд (RS) |

|

|

Блок трансляции |

36 |

|

|||

|

|

|

|

32 |

|

адреса (TLB) |

|

|

||

|

|

|

|

|

Кэш-память |

|

|

|||

|

IU1 IU2 FPU MMX SSE |

MIU |

|

|

|

|||||

|

|

данных (L1) |

64 |

|

||||||

|

|

|

|

32 |

32 |

|

32 |

32 |

Данные |

|

|

|

|

|

АдрЗп |

|

|

|

|||

|

|

|

|

АдрЧт |

|

|

|

|||

|

Шины данных 2х32 |

системная шина |

|

|

32 |

|

|

|

||

|

|

|

|

|

|

|

||||

|

Кэш-память |

Сигналы Данные |

Адрес |

|

Буферный блок |

|

|

|||

|

A[35:3] |

|

|

|

||||||

|

2-го уровня (L2) |

управления D[63:0] |

BE[7:0] |

|

обращения к |

32 |

|

|||

|

|

|

|

|

|

памяти (MOB) |

|

|||

|

|

|

|

|

|

Данные |

85 |

|||

© С. Г. Мосин, 2007 |

|

Блок внешнего интерфейса (BIU) |

|

|

||||||

|

|

|

|

|||||||

|

|

|

|

|

||||||

Лекция 3. Структура и функции

центрального процессора

Структура процессора Intel P6

Блок внешнего интерфейса (BIU): реализует протокол обмена процессора с системной шиной.

Внутренняя кэш-память команд и данных: 16 кбайт каждая

служит для размещения наиболее часто используемых команд и данных.

Блок выборки декодирования выбирает из кэш-памяти команд 32 байта командного кода, производит выделение и декодирование команды. Простые команды (выполняются за 1 микрооперацию) декодируют DC1 и DC2. Сложные команды (требуют несколько микроопераций) декодирует DC3.

86

© С. Г. Мосин, 2007

Лекция 3. Структура и функции

центрального процессора

Структура процессора Intel P6

Блок предсказания ветвления формирует адрес следующей выбираемой команды при ветвлении программы (условные переходы).

Блок распределения регистров (RAT) производит выделение регистров, необходимых для выполнения декодированных команд. Для логических регистров с ФТ или ПТ выделяет один из 40 физических регистров из блока регистров замещения.

Блок изменения последовательности команд (ROB)

обеспечивает эффективное выполнение потока декодированных команд.

87

© С. Г. Мосин, 2007

Лекция 3. Структура и функции

центрального процессора

Структура процессора Intel P6

Блок распределения (RS) направляет микрокоманды в соответствующие исполнительные устройства (БОД). Обеспечивает выполнение трех команд одновременно.

Исполнительные блоки IU1 и IU2 производят обработку целых чисел (БФТ – блоки с фиксированной точкой).

Блок FPU выполняет операции над числами с плавающей точкой (БПТ – блок с плавающей точкой).

Блок MMX реализует одновременную обработку нескольких упакованных символов.

88

© С. Г. Мосин, 2007

Лекция 3. Структура и функции

центрального процессора

Структура процессора Intel P6

Блок SSE выполняет операции над потоком чисел с ПТ.

Блок интерфейса с памятью (MIU) вычисляет адреса операндов, выбираемых из памяти, и реализует интерфейс с кэш-памятью данных или внешней памятью.

Буферный блок обращения к памяти (MOB) обеспечивает спекулятивную выборку операнда из кэш-памяти второго

уровня или внешней памяти при чтении и промежуточное хранение 32 байтов при записи.

89

© С. Г. Мосин, 2007

Лекция 3. |

Структура и функции |

|||||||

|

|

|

центрального процессора |

|||||

Структура микропроцессора MPC604 (Motorola) |

||||||||

|

|

|

|

|

|

Кэш-команд |

Команды |

Адрес |

|

|

|

1. Выборка команды |

А[31:0] |

||||

|

Устройство |

(IC) 16 Кбайт |

|

|||||

BPU |

2. Декодирование |

|

Адрес |

|

||||

|

|

|

||||||

|

управления |

3. Распределение команд |

IMMU |

|

Данные |

|||

|

|

|

|

|||||

|

|

|

|

|

||||

|

|

|

|

4. Выполнение команд |

|

D[63:0] |

||

|

|

|

|

Шины операндов |

|

|

|

|

|

|

|

GPR |

Буфер |

|

FPU FPR |

Буфер |

BUI |

SIU1 |

SIU2 MIU2 |

|

GPR |

LSU |

FPR |

|||

|

|

32x32 |

12x32 |

|

32x64 |

8 x 64 |

|

|

|

|

|

|

|

|

|

||

|

|

Шина результатов |

|

|

|

|

||

|

|

5. Буфер результатов |

|

DMMU |

Адрес |

УС |

||

Блок завершения |

|

|

|

|||||

6. Обратная запись |

|

Кэш-данных |

Данные |

|

||||

|

|

|

|

|

|

(DC) 16 Кбайт |

|

90 |

© С. Г. Мосин, 2007 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||