Лекция 8. Внутренняя память:

характеристики ЗУ

• производительность ЗУ

Скорость передачи характеризует интенсивность информационного потока. Для ЗУ с произвольным доступом она обратно пропорциональна длительности цикла обращения.

Для других видов памяти данную характеристику определяют

как

TN = TA + NR

где TN – среднее время считывания или записи N битов; TA – среднее время доступа; R – скорость пересылки (бит/сек).

Лекция 8. Внутренняя память:

характеристики ЗУ

•физический тип ЗУ

-полупроводниковые;

-магнитные;

-оптические;

-магнитооптические.

Основная характеристика физического типа запоминающих устройств – энергонезависимость.

Для выбора ЗУ необходимы ответы:

Какой объем? Какое быстродействие? Какая стоимость?

Лекция 8. Внутренняя память:

типы полупроводниковых ЗУ

|

Название |

Операции |

Способ стирания |

Метод записи |

Энергонеза- |

|

висимость |

|

|

|

|

|

|

|

|

Электрическим |

Электрическим |

|

|

RAM |

Чтение/запись |

сигналом на уровне |

Зависимая |

|

сигналом |

|

|

|

отдельного байта |

|

|

|

|

|

|

|

ROM |

Только чтение |

Невозможно |

Маска при |

Независимая |

|

изготовлении |

|

|

|

|

|

|

|

|

|

Электрическим |

|

|

PROM |

Только чтение |

Невозможно |

сигналом при |

Независимая |

|

изготовлении |

|

|

|

|

|

|

|

|

|

микросхемы |

|

|

|

Основная – |

Ультрафиолетовая |

Электрическим |

|

|

EPROM |

чтение, |

засветка всей |

Независимая |

|

сигналом |

|

|

возможна запись |

микросхемы памяти |

|

|

|

|

|

|

|

Основная – |

Электрическим |

Электрическим |

|

|

EEPROM |

чтение, |

сигналом выборочно на |

Независимая |

|

сигналом |

|

|

возможна запись |

уровне отдельного байта |

|

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

Базовый элемент полупроводникового ЗУ – запоминающий элемент (ЗЭ), который представляет ячейку памяти обладающую следующими свойствами:

• возможность находиться в одном из двух устойчивых состояний, соответствующих логическим 0 и 1;

|

• в элемент можно записать двоичный Управление |

|

|

|

|

|

код, т.е. целенаправленно перевести |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в определенное состояние; |

Выборка |

Запоминающий |

|

|

|

|

|

|

|

|

элемент |

|

• текущее состояние можно считать. |

|

|

|

|

|

|

|

|

|

|

|

|

© С. Г. Мосин, 2007

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

По способу реализации различают статические и динамические запоминающие элементы.

В статических ЗЭ информация может храниться неограниченно

долго при наличии напряжения |

Уст. в 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

питания. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Статический ЗЭ реализуют в |

Выбор |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

виде триггера с двумя |

ячейки |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

устойчивыми состояниями. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

Динамический запоминающий элемент способен хранить информацию только в течение короткого промежутка времени,

по истечении которого требуется ее восстановление (регенерация), иначе информация будет утеряна.

Существует три основные методы регенерации:

1. Одним сигналом RAS |

Вход |

(ROR – RAS Only Refresh); |

Выход |

|

2. Сигналом CAS, до появления RAS

(CBR – CAS Before RAS);

3. Автоматическая регенерация (SR – Self Refresh). |

236 |

© С. Г. Мосин, 2007 |

|

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

Запоминающий элемент обеспечивает хранение

одного бита информации.

Для построения запоминающего устройства большей разрядности используют совокупность ЗЭ,

адресные и управляющие входы которых (выборка и управление) объединены.

© С. Г. Мосин, 2007

Выборка |

Запоминающий |

|

элемент |

Управление |

|

Запоминающий |

Выборка |

элемент |

Вход0 /

выход0

Вход1 /

выход1

237

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

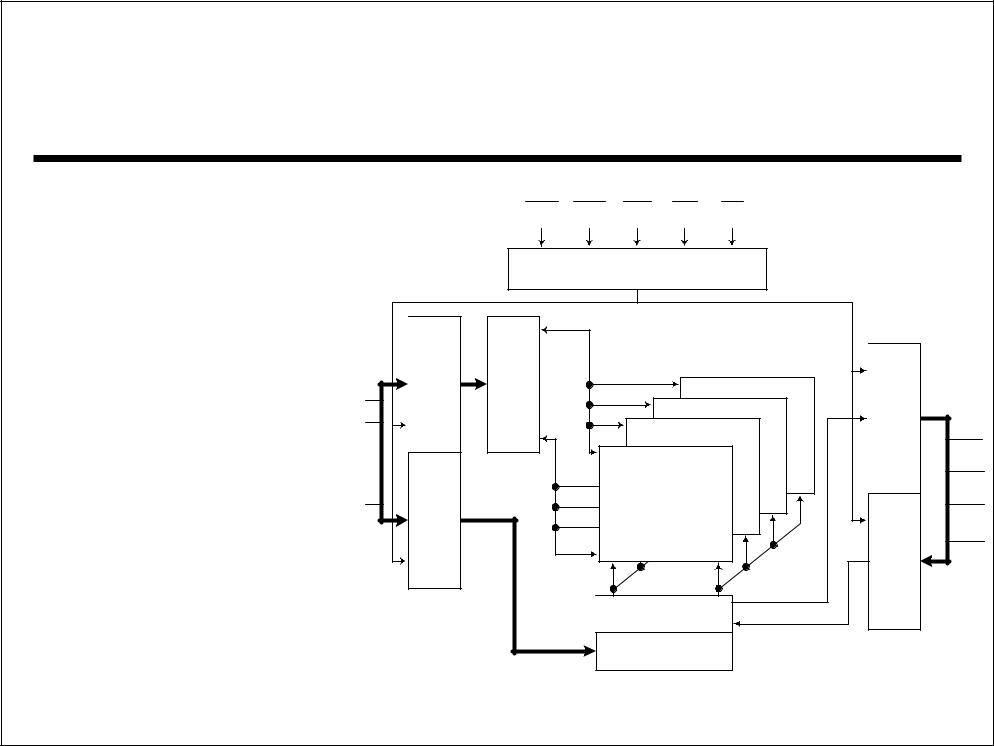

Модулем памяти называют микросхему ЗУ или совокупность микросхем ЗУ, обеспечивающую требуемую разрядность слова памяти, которая определена типом и архитектурой процессора.

Один или несколько модулей образуют банк памяти.

А0 Аm

CS

WR

© С. Г. Мосин, 2007

Dn-1 |

D1 |

D0 |

ИС ЗУn-1 ... |

ИС ЗУ1 |

ИС ЗУ0 |

|

|

238 |

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

2048 х 2048 = 222 ЗЭ |

Синхронизация и управление |

|

|

11 битов для |

|

|

|

|

|

|

|

адреса |

|

|

|

|

|

|

|

адресации |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

строк, |

A0 |

|

|

|

|

|

|

Буфер |

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 битов |

. |

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

адреса |

для |

A10 |

|

|

|

|

|

. |

|

|

|

|

|

|

|

адресации |

|

|

|

|

|

|

|

Буфер |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

столбцов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

© С. Г. Мосин, 2007

столбца строки

строки ... |

2048 x 2048 x 1 |

Выходнойбуфер |

|

2048 x 2048 x 1 |

|

|

2048 x 2048 x 1 |

|

|

Матрица ЗЭ |

|

2048 x 2048 x 1 |

буфер |

|

... |

Входной |

Усилители |

|

чтения / записи |

|

Дешифратор |

|

столбца |

|

данных

данных