Slides_OEVM_final

.pdf

Лекция 7. Устройство управления

Процесс проектирования устройства управления

Три стадии:

1.Определение базовых функциональных элементов процессора;

2.Составление перечня микроопераций, которые процессор будет выполнять;

3.Определение требуемых от УУ действий для организации выполнения последовательности микроопераций.

161

© С. Г. Мосин, 2007

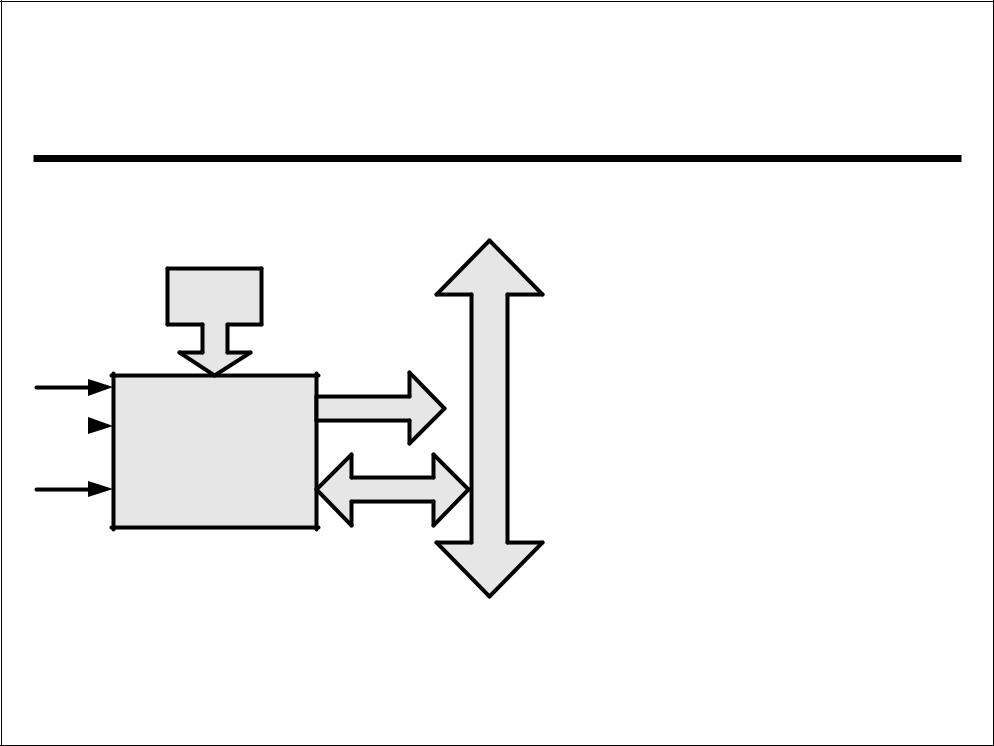

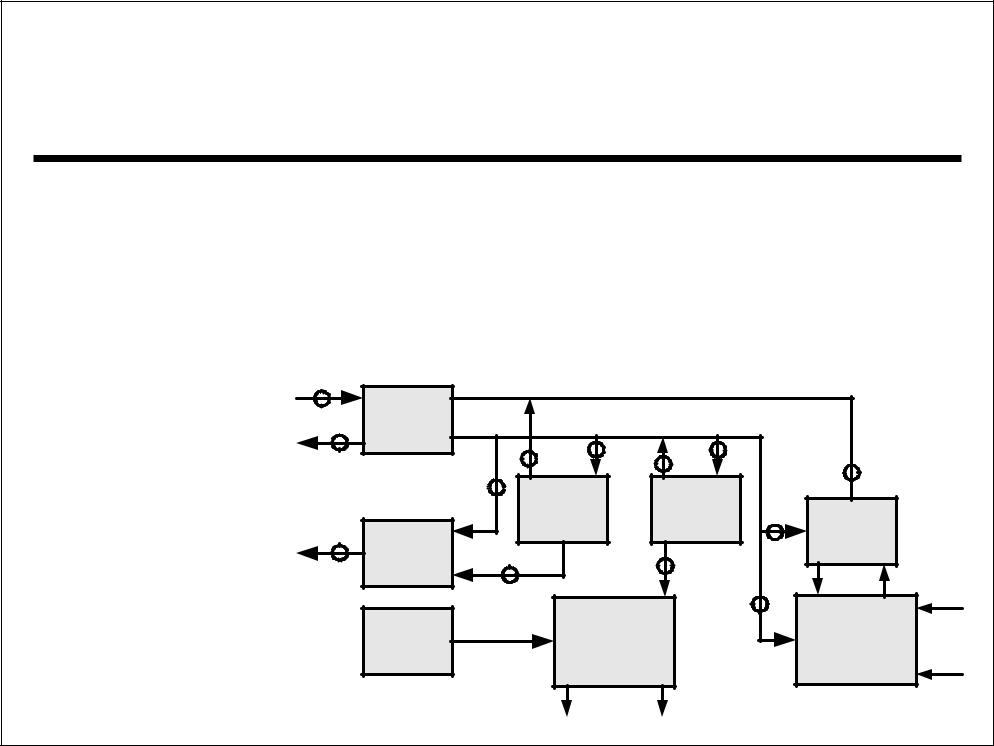

Лекция 7. Устройство управления:

управляющие сигналы

РгК Внутренние управляющие

сигналы

Флаги

Устройство ТИ управления

Управляющие сигналы системной магистрали

ШУ системной магистрали

Для функционирования УУ должно получать со входа определенную информацию о текущем состоянии системы и формировать выходные управляющие сигналы,

которые задают дальнейшее поведение системы.

162

© С. Г. Мосин, 2007

Лекция 7. Устройство управления:

управляющие сигналы

|

|

|

РгК |

Внутренние |

магистрали |

|

|

|

|

|

|||

|

|

|

|

управляющие |

|

|

|

|

|

|

|

сигналы |

|

|

|

|

|

|

|

|

Флаги |

Устройство |

|

|

системной |

||

|

ТИ |

|

|

|||

|

|

|

|

|||

|

управления |

|

|

|

||

|

|

|

|

|

|

ШУ |

|

|

|

|

|

|

|

|

|

|

Управляющие |

|||

|

|

|

|

|||

сигналы системной магистрали

© С. Г. Мосин, 2007

Управляющие сигналы:

1.Тактовые импульсы

синхронизируют выполнение всех операций во времени.

2.Поле КОП регистра команд определяет, какую

последовательность микроопераций должно

сформировать УУ. |

163 |

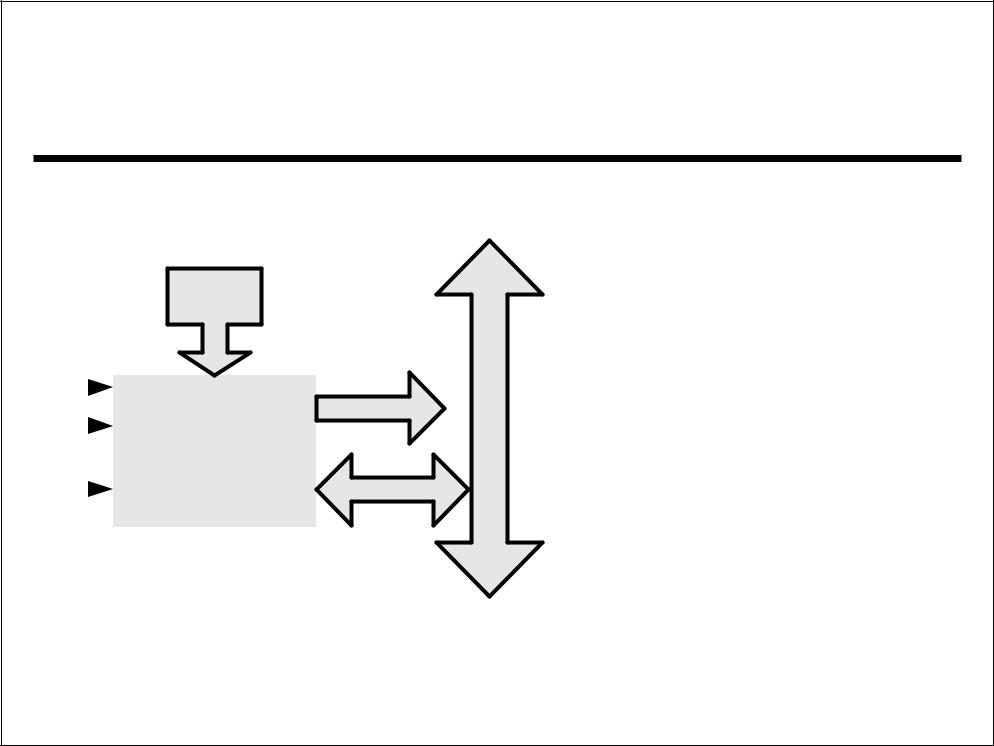

Лекция 7. Устройство управления:

управляющие сигналы

|

|

|

РгК |

Внутренние |

магистрали |

|

|

|

|

|

|||

|

|

|

|

управляющие |

|

|

|

|

|

|

|

сигналы |

|

|

|

|

|

|

|

|

Флаги |

Устройство |

|

|

системной |

||

|

ТИ |

|

|

|||

|

|

|

|

|||

|

управления |

|

|

|

||

|

|

|

|

|

|

ШУ |

|

|

|

|

|

|

|

|

|

|

Управляющие |

|||

|

|

|

|

|||

сигналы системной магистрали

© С. Г. Мосин, 2007

Управляющие сигналы:

3.Флаги необходимы для определения текущего состояния процессора и результата выполнения последней операции в АЛУ.

4.Сигналы ШУ системной магистрали, включающие

запросы на прерывания и подтверждения от внешних устройств. 164

Лекция 7. Устройство управления:

управляющие сигналы

Управляющие сигналы, формируемые УУ:

1.УС, распространяемые внутри процессора:

-сигналы передачи данных из одного регистра в другой;

-сигналы запуска определенных операций в АЛУ.

2.Сигналы, передаваемые по ШУ системной магистрали:

-сигналы, управляющие работой памяти;

-сигналы, управляющие работой модулей ввода/вывода.

165

© С. Г. Мосин, 2007

Лекция 7. Устройство управления:

управляющие сигналы

Управление на фазе извлечения машинной команды:

1.Пересылка содержимого CчАК в РгАдр (УС С2).

2.Чтение слова из

памяти и приращение кода адреса СчАК

(- УС С0;

-УС Read;

-УС С5;

-УС С3).

©С. Г. Мосин, 2007

С5 |

|

|

|

|

|

|

С12 |

РгД |

|

|

|

|

|

|

С1 |

С3 |

С14 |

С4 |

С11 |

|

|

С8 |

|

|

|

С10 |

|

С0 |

СчАК |

|

РгК |

|

|

|

РгАдр |

|

|

|

Акк |

|

|

|

|

С13 |

|

С7 |

С9 |

|

|

С2 |

|

|

|||

|

|

|

|

|||

|

|

|

|

С6 |

|

|

|

ТГ |

УУ |

|

|

УС |

|

|

|

|

АЛУ |

|||

|

|

УС |

|

|

|

166 |

|

|

|

|

|

|

Лекция 7. Устройство управления:

управляющие сигналы

Управление циклом обработки команды:

|

Извлечение |

РгАдр |

← (СчАК) |

С2 |

|

|

РгД |

← Память |

С5, Read |

|

|

|

команды |

СчАК |

← (СчАК) + I |

С3 |

|

|

|

РгК |

← РгД |

С4 |

|

|

|

|

|

|

|

|

Косвенная |

РгАдр ← РгК(Адр) |

С14, С8 |

|

|

|

адресация |

РгД ← Память |

С5, Read |

|

|

|

|

РгК(Адр) ← РгД(Адр) |

С4 |

|

|

|

|

|

|

|

|

|

Обработка |

РгД ← РгК |

С1 |

||

|

РгАдр ← Адр_сохр |

|

|

||

|

прерываний |

СчАК ← Адр_п/прогр |

|

|

|

|

|

Память ← (РгД) |

С12, Write |

||

167

© С. Г. Мосин, 2007

Лекция 7. Устройство управления:

управляющие сигналы

Управление циклом обработки команды:

УУфункционирует, зная только исполняемую команду и свойства результата выполнения предыдущей команды.

УУне имеет доступа к значениям обрабатываемых данных и полученных результатов.

168

© С. Г. Мосин, 2007

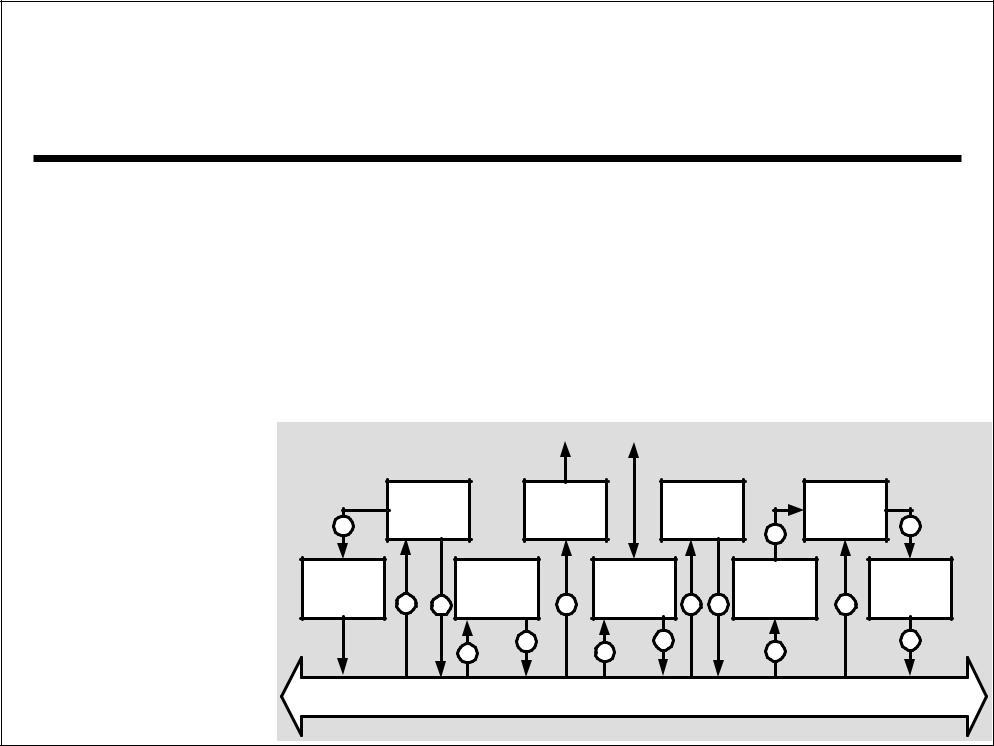

Лекция 7. Устройство управления:

управляющие сигналы

АЛУ и все регистры процессора подключены к единой внутренней магистрали. Группы вентилей на входе и выходе каждого элемента обеспечивают подключение.

Достоинство: минимизация коммутационного пространства Суммирование значения из памяти со значением аккумулятора:

t1: РгАдр ← РгК(Адрес) |

Линия адреса |

Линия данных |

|

|||

t2: РгД ← Память |

|

РгК |

РгАдр |

|

Акк |

АЛУ |

t3: Y ← (РгД) |

|

|

||||

|

|

|

|

|

|

|

t4: Z ← (Акк)+(Y) |

УУ |

|

СчАК |

РгД |

Y |

Z |

t5: Акк ← (Z)

Внутренняя магистраль процессора |

169 |

© С. Г. Мосин, 2007 |

|

Лекция 7. Устройство управления

Устройство управления

Сжесткой логикой

Ввиде конечного автомата,

формирующего выходные сигналы управления в зависимости от текущего состояния и значений осведомительных входных сигналов

Микропрограммного

управления

В виде устройства выбора из микропрограммной памяти микрокоманд, содержащих набор управляющих сигналов,

в нужной последовательности и загрузки их в регистр микрокоманд.

170

© С. Г. Мосин, 2007