Slides_OEVM_final

.pdf

Лекция 3. Структура и функции

центрального процессора

Структура микропроцессора MPC604 (Motorola) BPU – блок обработки ветвлений.

SIU1, SIU2 – устройства выполнения простых одноцикловых целочисленных операций.

МIU – устройство выполнения сложных многоцикловых целочисленных операций.

FIU – устройство обработки чисел в формате с плавающей точкой.

LSU – блок выборки данных из памяти и загрузки в регистры данных GPR и FPR.

91

© С. Г. Мосин, 2007

Лекция 3. Структура и функции

центрального процессора

Цикл обработки машинной команды

Процесс обработки отдельной команды принято называть циклом обработки. Основные операции:

•Вычисление адреса команды (СчК = СчК + const);

•Извлечение команды (РгК = ОП[СчК] );

•Расшифровка кода операции;

•Вычисление адреса операнда;

•Извлечение операнда;

•Обработка данных;

•Сохранение результата;

•Обработка прерываний.

92

© С. Г. Мосин, 2007

Лекция 3. |

Структура и функции |

||||||

|

|

|

центрального процессора |

||||

Цикл обработки машинной команды |

|

||||||

Извлечение |

|

Извлечение |

|

Сохранение |

Анализ |

||

|

|

запросов |

|||||

команды |

|

|

операнда |

|

|

результата |

|

|

|

|

|

прерывания |

|||

|

|

|

|

|

|

|

|

|

|

Несколько |

|

Несколько |

|

Запрос на |

|

|

|

операндов |

|

результатов |

прерывание |

||

Вычисление |

Расшифровка |

Вычисление |

|

Вычисление |

|

||

кода |

Обработка |

|

|||||

адреса |

|

адреса |

|

адреса |

Прерывание |

||

|

операции в |

|

данных |

||||

операнда |

|

операнда |

|

операнда |

|

||

|

команде |

|

|

|

|||

|

|

|

|

|

|

|

|

|

Выполнение команды завершено. |

Возврат при выполнении операций |

Нет запросов |

||||

|

Извлечь следующую команду. |

над строками или векторами |

|

на прерывание |

|||

© С. Г. Мосин, 2007 |

|

|

|

|

93 |

||

|

|

|

|

|

|||

Лекция 3. Структура и функции |

|

|

центрального процессора |

|

|

Цикл обработки машинной команды |

|

|

Поток данных на фазе извлечения машинной команды |

|

|

СчАК |

РгАдр |

|

|

Память |

|

|

УУ |

|

РгК |

РгД |

|

Процессор |

ША ШД ШУ |

94 |

© С. Г. Мосин, 2007 |

|

|

|

|

|

Лекция 3. Структура и функции |

|

|

центрального процессора |

|

|

Цикл обработки машинной команды |

|

|

Поток данных на фазе прерывания |

|

|

СчАК |

РгАдр |

|

|

Память |

|

|

УУ |

|

|

РгД |

|

Процессор |

ША ШД ШУ |

95 |

© С. Г. Мосин, 2007 |

|

|

|

|

|

Лекция 4. Конвейерная обработка

машинных команд

Повышение производительности

•За счет совершенствования элементной базы (переход к новой интегральной технологии, рост плотности размещения компонентов на единице площади кристалла, рост частоты).

•За счет рациональной организации процесса выполнения команд в компьютере (параллелизм, архитектурные решения: CISC и RISC).

96

© С. Г. Мосин, 2007

Лекция 4. Конвейерная обработка

машинных команд

Особенности архитектур RISC и CISC

CISC – компьютер с полным набором машинных команд; RISC – компьютер с сокращенным набором машинных команд.

|

Наименование |

CISC |

RISC |

1. |

Количество команд |

много |

мало |

2. |

Длина программы |

короткие |

длинные |

3. |

Формат команд |

сложный |

простой |

4. |

Выполнение команд |

за несколько циклов |

за цикл |

5. |

Скорость выполнения программы |

выше (?) |

ниже (?) |

6. |

Типы адресации |

сложные (КА) |

простые (Рг) |

7. |

Количество регистров |

мало |

много |

8. |

Устройство управления |

МПУ |

жесткая логика |

97

© С. Г. Мосин, 2007

Лекция 4. Конвейерная обработка

машинных команд

Конвейеризация вычислений

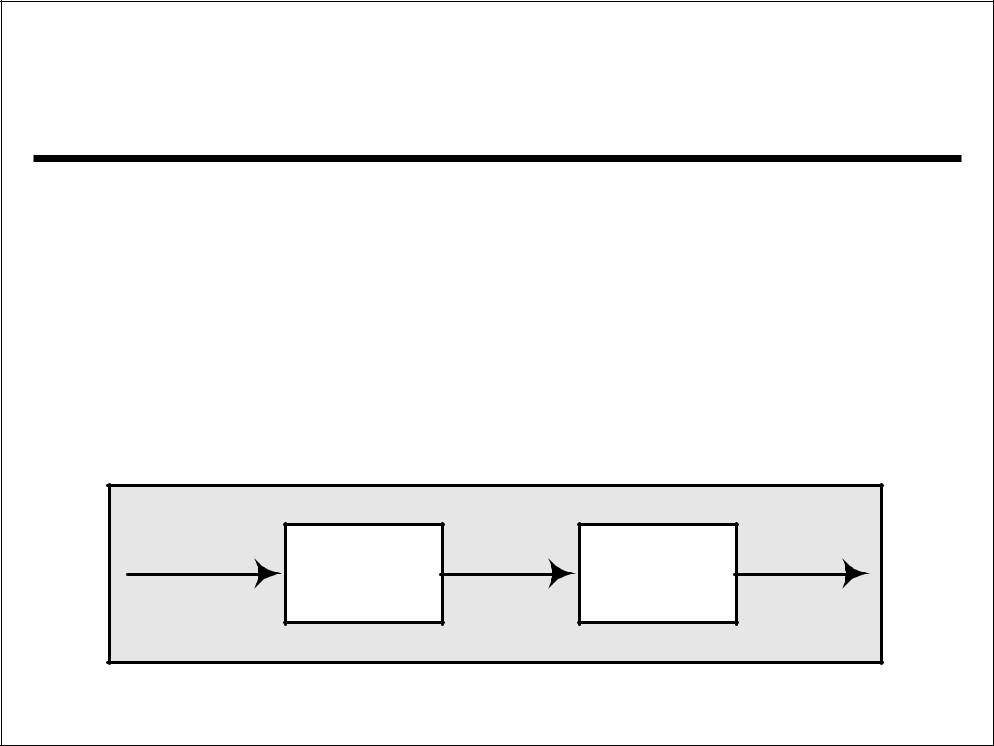

Конвейер имеет два независимых блока обработки – извлечения и выполнения команды.

Пока команда выполняется на втором блоке, первый блок может загружать следующую машинную команду.

Команда |

Команда |

Результат |

|

Извлечение |

Выполнение |

© С. Г. Мосин, 2007 |

|

98 |

|

|

Лекция 4. Конвейерная обработка

машинных команд

Конвейеризация вычислений

Причины снижения производительности конвейера:

•Время выполнения больше времени извлечения команды;

•В командах условного перехода нельзя заранее предсказать адрес следующей выполняемой команды.

Ожидание |

Новый адрес |

Ожидание |

Команда |

Команда |

Результат |

Извлечение |

|

Выполнение |

Аннулирование |

|

|

© С. Г. Мосин, 2007 |

|

99 |

|

|

|

Лекция 4. Конвейерная обработка

машинных команд

Конвейеризация вычислений

Для достижения быстродействия конвейера необходимо:

•разделить ЦОК на большее количество независимых этапов;

•время выполнения команды на каждом этапе одинаково (такт конвейера).

ti ≈ const

100

© С. Г. Мосин, 2007