Энциклопедия PC

.pdf216iS. Процессоры

^черню и совместную работу нескольких процессоров. Эти режимы практически незаметны прикладному программисту и пользователю, но представление о них дает болееполнуюкартину «жизни» процессора вкомпьютере.

5.4.1. Запускиинициализацияпроцессоров

Аппаратный сброс (hardware reset) выполняется процессором при включении питания и по сигналу RESET#. По низкому уровню сигнала RESET# процессор прекращает выполнение инструкций и перестает управлять системной шиной. В момент окончания сигнала аппаратного сброса процессор воспринимает уровни сигналов на некоторых линиях интерфейса, что определяет его интерфейсные свойства. Процессору устанавливается коэффициент умножения тактовой частоты, режим (WB/WT) работы кэша, роль процессора в многопроцессорных системах, способ подачи сигналов прерываний (для процессоров, имеющих APIC) и некоторые другие параметры. Эти уровни задаются чипсетом системной платы в соответствии с ролью процессора и установками джамперов и CMOS Setup. Сброс переводит процессор в реальный режим и устанавливает ряд регистров в определенноесостояние.

Аппаратный сброс аннулирует строки кэш-памяти, буферов трансляции (TLB) и таблиц переходов (ВТВ). После сброса процессор начинает выполнение инструкции, считанной по физическому адресу FFFFFFFOh. Исполняемый программный код должен обеспечить инициализацию системы (регистров процессора, структур данных в памяти). Из этого следует, что, по крайней мере, на начальный период времени после сигнала RESET# компьютер должен иметь образ BIOS в

адресах FFFFFFFO-FFFFFFFFh, в то время как в PC на 8086/88 ROM BIOS

располагаласьподграницейпервогомегабайта(FFFFFh), a AT-286 имелиееобрази подграницей 16-гомегабайта (FFFFFFh).

Процессоры Р6 допускают смену положения вектора начального запуска на OFFFFOh, правда, этой возможностью, похоже, никто не пользуется (в Pentium 4 этойвозможностиуженет).

Процессоры Pentium+ имеют дополнительный вход INIT, по которому выполняются примерно те же действия, но не очищается внутренняя кэш-память, не изменяется состояние FPU и регистров MSR. Этот сигнал может использоваться для перевода процессора в реальный режим (в стиле 80286) с сохранением данных в кэше. Такой же «мягкий» сброс возможен и по сообщению, получаемому процессоромпошинеAPI С.

5.4.2. Обновлениемикрокода

Фирма Intel постоянно модернизирует свои процессоры, и даже в пределах одной модели процессоры разного времени выпуска различаются степпингом (см. п. 5.5.2). Для процессоров каждого степпинга известны свои ошибки (errata) и методы их исправления. Микроархитектура Р6 позволяет исправлять эти ошибки путем загрузки в процессор блока «заплаток», являющегося, очевидно, набором фрагментов микропрограмм. Обновление микрокода (Microcode Update) должно выполняться во время инициализации процессора после аппаратного

5.4. Особыережимыработыпроцессора 217

сброса, загруженный микрокод действует только до следующего аппаратного сброса (инициализация сигналом 11М1Т# на загруженное обновление не влияет). Фирма Intel отвечает за корректность работы своих процессоров только при загруженных «заплатках» и для каждого степпинга выпускает специальный блок данных (в виде файла). Таким образом, процессор определенного степпинга рассматривается как комплект из собственно процессора и «заплаток». Заплатки фирма помещает на своем сайте, правда, доступ к ним закрыт паролями. Пароли сообщаются официальным дилерам, так что за свежими «заплатками» следует обращаться именно к ним. Если дилер не способен предоставить «заплатки» (или сообщить пароль), то можно усомниться в его легальности. Загрузка актуальных заплаток в процессор организуется в два этапа: требуемый образ «зашивается» в BIOS изготовителем компьютера или пользователем; на этапе инициализации компьютера BIOS организует загрузку микрокода в процессор. Если BIOS не поддерживает процессор требуемого степпинга, следует обновить либо всю систему BIOS (см. п. 4.2.6), либо только область с микрокодами. Для обновления в BIOS области с микрокодом могут быть использованы функции DMI. Более полно процедура обновления описана в книге [2]. Если требуемое обновление микрокода

вBIOS встроить не удается, можно использовать загружаемые утилиты обновления, запускаемые на платформах DOS/ Windows 9x из файла AUTOEXEC.BAT прикаждойзагрузкеОС.

«Заплатки» поставляются в виде блоков данных размером 2048 байт и никакого исполняемого кода не содержат. Блок состоит из 48-байтного заголовка (номер версии заголовка указывается в самом его начале) и собственно данных обновления (2000 байт). Целостность всего блока проверяется контрольной суммой. Поле версии обновления позволяет определить, загружено ли данное обновление

впроцессор. Блок обновления приемлем только для процессора, имеющего тот же идентификатор (тип, семейство, модель, степпинг), который указан в заголовке блока. Обновление должно загружаться загрузчиком, версия которого соответствует указанной в заголовке. Загрузчик версии 1 (другие пока не описаны) просто записывает линейный адрес данных (адрес блока +48) в MSR 79h. Обновление может выполняться многократно без каких-либо побочных эффектов. Успешность иверсию произведенного обновления можно проверить программно, не изменяя состояния обновления. Попытка загрузить обновление с идентификатором, не соответствующим данному процессору, не удастся (процессор проигнорирует эту попытку). В мультипроцессорных системах обновляемые данные для каждого процессора должны соответствовать его типу, модели, степпингуиидентификаторуплатформы.

5.4.3. РежимсистемногоуправленияSMM

Современныемодели32-разрядныхпроцессоров(начинаяснекоторыхмодификаций 486 и 386SL) кроме обычных режимов — реального, защищенного и V86 — имеют дополнительный режим системного управления SMM (System Management Mode). Этот режим предназначен для выполнения ряда действий с полной изоляцией их от прикладного программного обеспечения и даже от операционной

218 Глава5. Процессоры

системы. Главным образом, этот режим предназначен для реализации системы управленияэнергопотреблением, хотяможетиспользоватьсяивиныхцелях.

В режим SMM процессор может войти только по сигналу на входе SMI# (System Management Interrupt), процессоры P5+ могут войти в SMM и по приему соответствующего сообщения по шине API С. Сигнал SMI# для процессора является немаскируемым прерыванием с наивысшим приоритетом. Обнаружив активный сигнал SMI# (низкий уровень), процессор по завершении текущей инструкции и выгрузки буферов записи переключается в режим SMM, о чем сигнализирует своим интерфейсом. Сразу при входе в SMM процессор сохраняет свой контекст — почти все регистры — в специальной памяти SMRAM (не в стеке!), которая представляет собой выделенную область физической памяти, доступ к которой разрешается внешними (по отношению к процессору) схемами в шинных циклах обращения к памяти только при сигнализации процессором о нахождении в режиме SMM. После сохранения контекста процессор переходит к выполнению обработчика SMI, который расположен в той же памяти SMRAM. Обработчик представляет собой последовательность обычных инструкций, исполняемых процессором в режиме, напоминающем реальный. При входе в режим SMM автоматически запрещаются аппаратные прерывания (включая и немаскируемые) и не генерируются исключения, так что действия процессора однозначно определяются программой обработчика SMI. Процедура обработчика завершается инструкцией RSM, по которой процессор восстанавливает свой контекст из образа, хранившегося в SMRAM, и возвращается в обычный режим работы.

При возврате из SMM возможны некоторые варианты в зависимости от действий обработчика: он может программно внести изменения в образ контекста процессора, а также запросить рестарт (повторное исполнение) инструкции, предшествующейпоявлениюсигналаSMI#.

Возможность рестарта инструкции ввода-вывода расширяет режим SMM, позволяя организовать на уровне BIOS управление энергопотреблением совершенно прозрачно для прикладного ПО и ОС. Прозрачность SMM обеспечивается следующимисвойствамиэтогорежима:

» возможностью только аппаратного входа в SMM;

и исполнениемкодаSMM вотдельномадресномпространстве;

»полнымсохранениемсостоянияпрерваннойпрограммывобластиSMRAM;

»запретомобычныхпрерываний;

»восстановлениемсостоянияпрерваннойзадачиповыходуизрежимаSMM.

Память SMRAM должна быть физически или логически выделенной областью размером от 32 Кбайт (минимальные потребности SMM) до 4 Гбайт. В ней выделяются область сохранения контекста и точка входа в обработчик SMI, кроме того, имеетсясвободнаяобласть.

Карта сохранения контекста имеет «официальную» часть, в которой находятся образы архитектурных (видимых) регистров, и не публикуемую часть (зарезервированные поля). Неосторожная модификация полей, запрещенных для записи, может привести к непредсказуемым (для непосвященных) результатам. В зарезервированных полях скрывается автоматически сохраняемый уп-

5.4. Особыережимыработыпроцессора 219

зааляющий регистр CR4 и программно невидимые скрытые регистры дескрипторов для всех сегментов, но местоположение и формат их образа зависят от моделипроцессора.

Если режим SMM используется для отключения питания процессора с возможностью быстрого «пробуждения», память SMRAM, хранящая контекст прозессора, должна быть энергонезависимой и схемотехнически защищенной от догтупа прикладных программ. Если SMRAM не является энергонезависимой, то системная логика должна обеспечить возможность ее инициализации (записи программного кода обработчика) процессором из обычного режима работы до !юявлениясигналаSMI#.

5.4.4. Синхронизацияиуправление энергопотреблением

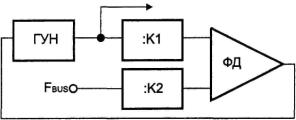

Синхронизация процессоров осуществляется внешним сигналом, определяющим частоту системной шины (FSB Clock). Ядро процессора синхронизируется с помощью умножителя частоты, выполненного по схеме генератора с фазовой автоподстройкой частоты. Схема фазовой автоподстройки поддерживает заданное гоотношение частоты внутреннего генератора и внешнего сигнала BCLK. Умножение частоты в процессоре выполняется с помощью внутреннего управляемого генератора, включенного в контур системы фазовой автоподстройки частоты < ФАПЧ). Структурная схема умножителя приведена на рис. 5.3. Контур фазо-юй автоподстройки PLL (Phase Lock Loop) в установившемся режиме обеспечивает нулевой фазовый сдвиг (а следовательно, и совпадение частот) на входах фазового детектора. Эти сигналы образуются путем деления частот FBUS (частота шины) и FCORE (частота ядра) на соответствующие целочисленные коэффициенты, следовательно, встационарномрежиме выполняется условие:

FBus/k2 или F |

CORE FBUSx kl/k2 |

FCORE

Рис. 5.3. Схемаумножениячастоты(ГУН— генератор, управляемыйнапряжением; ФД— фазовыйдетектор)

Целочисленное деление частоты обеспечивается триггерами или управляемыми счетчиками. Нулевой сдвиг фаз, необходимый для точной привязки внутренних тактов к синхронизации внешней шины, обеспечивается системой автоматического регулирования с астатизмом. Это подразумевает некоторую инерцион-эость — при изменении частоты FBUS на время переходного процесса условия синхронизации выполняться небудут. Точнотак жепереходный процесс возни-

220 Глава5. Процессоры

кает при смене коэффициентов. Поскольку поведение процессора, у которого внутреннее тактирование не привязано к синхронизации внешней шины, непредсказуемо, смена внешней частоты и коэффициентов деления допустима только во время аппаратного сброса. После установки параметров синхронизации аппаратный сброс должен удерживаться еще некоторое время, за которое переходный процесс завершится и установится нулевой сдвиг фаз.

Коэффициент умножения частоты либо фиксирован (на конечном этапе изготовления процессора), либо задается уровнями сигналов на определенных входах процессора во время действия сигнала RESET*. Диапазон частот системной шины, при котором обеспечивается захват в системе ФАПЧ, ограничен и задается в спецификациях на процессоры.

Современные процессоры потребляют значительную мощность (десятки ватт), которая, естественно, выделяется в виде тепла. Мощность (и тепловыделение) растет с повышением тактовой частоты. Если от процессора не требуется максимально возможная производительность, его можно «притормозить» для снижения потребления. Минимальную мощность процессор потребляет при остановленном тактовом генераторе, при этом он не выполняет никаких функций, а последующая подача синхронизации должна сопровождаться сигналом аппаратного сброса RESET. Схемы внутреннего умножения требуют стабильности внешней частоты во время работы процессора, так что для временного снижения потребления приходится использовать специальные механизмы. На рис. 5.4. приведены состояния (с точки зрения потребления), в которых могут находиться современные процессоры. В нормальном состоянии (Normal State) процессор выполняет все свои функции, здесь потребление максимальное.

ИнструкцияHALT

1. Normal State

INIT#, BINIT#, INTR, SMI#, RESET#

STPCLK# снят,

в«З» входилииз«2»

Событиеслежения

Завершениеобслуживаниясобытияслежения

Остановсинхронизации(BCLK)

Восстановлениесинхронизации(BCLK) Рис. 5.4.

Диаграммапереходоврежимовпониженногоэнергопотребления

По сигналу STPCLK# процессор выгружает буферы записи и входит в режим Stop Grant, в котором прекращается тактирование большинства узлов процессора, что вызывает снижение энергопотребления примерно в 10 раз. В этом состоянии он прекращает исполнение инструкций и не обслуживает прерывания, однако продолжает слежениеза шиной, отслеживая кэш-попадания. Из этого со-

5.4. Особыережимыработыпроцессора 221

стояния процессор выходит по снятию сигнала STPCLK#. Управление сигналом STPCtK* совместно с использованием режима SMM реализует механизм расширенного управления питанием АРМ (Advanced Power Management). При отсутствии активности внешняя схема (чипсет) по команде, исполненной в режиме $ММ. устанавливает данный сигнал. По пробуждающему событию внешняя схема (без участия процессора, который «спит») снимает сигнал, и процессор продолжает работу. Кроме того, с помощью сигнала STPCLK* возможно замедление про-t&ctopa (с пропорциональным снижением потребляемой мощности), если на этот иод подавать периодический импульсный сигнал. Скважность импульсов будет определять коэффициент простоя процессора и, следовательно, его производительность (это как бы эквивалентно снижениюусловной тактовой частоты).

В состояние пониженного энергопотребления Auto HALT PowerDown процессор переходит при исполнении инструкции HALT. В этом состоянии процессор реагирует на всепрерывания и также продолжает слежениеза шиной.

Всостоянии Sleep (спящий режим), которое вызывается сигналом SLP#, процессор не тактирует свои внутренние узлы (кроме схемы умножителя частоты). Прерывания и циклы слежения не воспринимаются. Процессор может реагировать только на сигналы SLP#, STPCLK# и RESET*. По снятию сигнала SLP# процес-:ор возвращается в состояние Stop Grant и возобновляет тактирование своего £лока управления шиной и APIC. Потребляемый ток менее1 А.

Всостояние «глубокого сна» Deep Sleep процессор переходит при остановке тактового сигнала на входе BCLK. В этом режиме процессор не выполняет никаких функций и его ток потребления снижается додолей ампера.

Средства управления потреблением появились с процессорами Pentium второго поколения, где реализованы состояния 1-4. Процессоры Pentium II/III и Celeron имеют дополнительные состояния 5 и 6 (процессоры Хеоп состояния 6 неимеют).

5.4.5. Мультипроцессорныеиизбыточные системы

В современных ПК встречаются варианты установки нескольких (двух или более) процессоров на одной системной шине. При этом возможна мультипроцессорная

(SMP — Symmetric Multi-Processing) конфигурация и системы с избыточным контролем функциональности (FRC — Functional Redundancy Checking). В

симметричных мультипроцессорных системах в принципе могут использоваться процессоры различного степпинга, но частоты ядра у них должны совпадать (внешняя частота у них, естественно, должна быть единой). Из «не-интеловских» процессоров х86 возможность работы в SMP имеют пока только процессоры Athlon фирмы AMD. Поддержка FRC появилась, начиная с процессоров Intel Pentium, но не во всех последующих моделях; она имеется иупроцессоров фирмы

AMD.

Симметричныемультипроцессорныесистемы

Процессоры Pentium (начиная со второго поколения) имеют специальные интерфейсныесредствадляпостроениямультипроцессорныхсистем(сдвумяи

222 Глава5. Процессоры

более процессорами). Целью объединения процессоров является симметричная мультипроцессорная обработка SMP (Symmetric Multi-Processing). В симметричной системе SMP каждый процессор выполняет свою задачу, порученную ему операционной системой. Поддержку SMP имеют такие ОС, как Novell NetWare, Microsoft Windows NT и различные диалекты UNIX. Процессоры, объединенные общей локальной шиной, разделяют ресурсы компьютера, включая память и внешние устройства. В каждый момент времени шиной может управлять только одинпроцессор, поопределеннымправиламонименяются ролями.

Поскольку каждый из процессоров имеет свой внутренний первичный кэш, интерфейс обязан поддерживать согласованность данных во всех иерархических ступенях оперативной памяти — в первичном и вторичном кэшах и основной памяти (в Pentium вторичный кэш у процессоров общий). Эта задача решается с помощью локальных циклов слежения, воспринимаемых процессором, даже не управляющимшинойвданныймомент.

Симметричные системы имеют специальные механизмы арбитража доступа к локальной шине. Процессор — текущий владелец шины — отдаст управление шиной другому процессору по его запросу только по завершении операции. Интерфейс Pentium (начиная со второго поколения) позволяет на одной локальной системной шине устанавливать два процессора, при этом почти все их одноименные выводы просто непосредственно объединяются. Роль конкретного процессора в системе фиксирована — она определяется внешними сигналами во время спада сигнала RESET. Один из процессоров назначается первичным (Primary) или

загрузочным (BSP — Bootstrap Processor), другой — вторичным (DP — Dual Processor). После сигнала RESET сразу начинает функционировать только первичный процессор (BSP), выполняя программный код инициализации. Второй про цессор начнет функционирование только после приема соответствующего сообщения по шинеAPIC, посланного подуправлениемпрограммы инициализации.

В процессорах Р6 заложены более развитые возможности SMP. Системная шина Р6, в отличие от локальной шины Pentium, изначально ориентирована на разделяемое управление множеством симметричных (до четырех на шине) и несимметричных (до восьми) агентов. Сокет 8 (Pentium Pro) и слот 2 (Pentium II Хеоп) позволяют объединять до четырех процессоров, слот 1 (Pentium II) допускает объединение не более двух процессоров. Процессоры Pentium II OverDrive для сокета 8 тоже допускают объединение не более двух процессоров. Фирма Intel объясняет это ограничение большой паразитной индуктивностью контактов сокета (звучит неубедительно, поскольку внешняя шина работает на тех же частотах, что и Pentium Pro). Какой из процессоров станет первичным (BSP), определяется по загрузочному протоколу, — здесь нет жесткой аппаратной привязки роли процессора к его «географическому» адресу. Это позволяет повысить надежность SMP-системы, поскольку любой процессор может без механического вмешательства во время инициализации взять на себя роль BSP. Протокол мультипроцессорной инициализации работает на шине APIC, он позволяет управлять инициализацией до 15 процессоров. Процессоры могут пользоваться содержимым «чужого» кэша без его предварительной выгрузки в основную память.

5.5. Совместимостьиидентификацияпроцессоров 223

Процессоры Celeron официально предназначены лишь для однопроцессорных конфигураций. Однако реально у процессоров на ядре Mendocino имеется сигнал BR1#, требуемый для SMP, правда, не там, где хотелось бы. Если использовать такой процессор в корпусе PGA с переходником в слот 1 (для двухпроцессорной системной платы), то на переходнике достаточно организовать связь контакта В75 краевого разъема с контактом AN15 процессорного сокета. Есть и переходники, подготовленные к дуальному использованию Celeron самим изготовителем — на них имеется специальный джампер для штатного и нештатного назначения контакта В75. На процессорах в картриджах SEPP умельцы ухитряются освобождать контакт В75 и соединять его с выводом сигнала BR1# кристалла ядра. Таким образом удается использовать Celeron и в двухпроцессорных системах, что привлекательно, учитывая относительную дешевизну этого процессора. Однако Celeron на ядре Coppermine SMP уже не поддерживает (как и некоторые модели Pentium III Coppermine).

Системысизбыточнымконтролемфункционирования

В конфигурации с избыточным контролем функционирования FRC (Functional Redundancy Checking) два процессора (пара Master/Checker) выступают как один логический. Основной процессор (Master) работает в обычном однопроцессорном режиме. Проверочный процессор (Checker) выполняет все те же операции «про себя», не управляя шиной, и сравнивает выходные сигналы основного (проверяемого) процессора с теми сигналами, которые он генерирует сам, выполняя те же операции без выхода на шину. В случае обнаружения расхождения вырабатывается сигналошибки, который может обрабатываться как прерывание.

5.5. Совместимостьиидентификация процессоров

Как уже говорилось, во всех IBM PC-совместимых компьютерах применяются процессоры семейства х86 как от фирмы Intel, так и от других производителей. Это семейство компьютеров живет долго благодаря совместимости программного обеспечения с различными процессорами. Однако программам (и пользователям) отнюдь не все равно, на каком процессоре работать. Далее рассматриваются некоторые вопросы совместимости, способы идентификации, а также сравнительныехарактеристикираспространенныхпроцессоров.

5.5.1. Совместимостьпроцессоров

Для всех процессоров, применяемых в PC, характерна принадлежность к единой архитектурной линии Intel Architecture (IA-32), в которой процессоры следующих моделей вбирают в себя все свойства и инструкции предыдущих. Правда, некоторые инструкции объявлены не архитектурными, а зависящими от модели, т их наличие и функционирование в следующих моделях не гарантируется. Состав регистров и флагов помере«взросления» процессоров постоянно расширя-

224 Глава5. Процессоры

ется. Для совместимости программного обеспечения, написанного для ранних моделей процессоров, со следующими моделями следует осторожно обращаться с неиспользуемыми(зарезервированными) битамиирегистрами:

»неизменятьзначениябит, неиспользуемыхвданномпроцессоре;

»гарантировать нечувствительность программкзначениюэтихбит;

*призагрузкерегистроввзарезервированные битызаписыватьнули;

« непытатьсяиспользоватьэтибитыдляхранениякаких-либопризнаков.

Декларируемая обратная совместимость новых моделей с предыдущими означает, что программный код, написанный для процессора 8088, должен таким же образом исполняться и на 80386, и на Pentium 4, и на любых других совместимых процессорах. В большинстве случаев так это и происходит, но программы на более новых процессорах исполняются, естественно, быстрее. Здесь и кроется один из подводных камней совместимости. Дело в том, что большинство программ для PC выполняет не только вычисления, но и управляет различным внутренним и внешним оборудованием. При этом оборудование требует определенной последовательности действий и соблюдения временных характеристик. Устройства с невысоким быстродействием не могут, например, воспринимать последовательные обращения к ним, идущие в соседних тактах системной шины ввода-вывода. Программные способы организации задержек должны опираться на сведения о модели (и, если есть возможность, о тактовой частоте) процессора, на котором исполняется код. Иначе возможны перекосы в обе стороны, которые могут приводить к разнообразным неприятным эффектам. С программными задержками были связаны, в частности, проблемы применения некоторых процессоров Cyrix. Их архитектурные преимущества оборачиваются неработоспособностью некоторых программ.

Для введения программных задержек при обращении к портам ввода-вывода в BIOS компьютеров на процессорах 8088, 80286 и 80386 использовались команды короткого безусловного перехода (JMP SHORT) на следующий адрес. Эта команда сбрасывала конвейер (очередь декодированных инструкций), и процессор был вынужден снова делать выборку кода операции из памяти, а в это время порт «переводил дух» перед следующим обращением. Такой способ задержиприменялся не только в BIOS, но и в загружаемых программах.

Однакоэтотспособвведенияпрограммнойзадержкидляпроцессоров, имеющих внутренний кэш (то есть 486 и выше, а также некоторые модели 80386). ы- пригоден. ЗдеськомандаJMP, ранеебезусловноприводящаякгенерациивнешнего цикла обращения к памяти, скорее всего, будет обслужена из внутреннего кэша, и желаемой задержки не произойдет. Одним из способов введения внешнегоцикла шинымеждуцикламивыводаявляетсяявнаяоперациячтениянею*-шируемой области памяти. Эта операция в процессорах с упорядоченным вы полнением инструкцийбудетвыполненатолькопослезавершенияпредыдущейцикла вывода, а последующая операция вывода начнется только по завершени этогочтения.

В процессорах шестого поколения возможно изменение порядка выполнен.» операций, и чтение памяти может обогнать другие операции на внешней шин Еслипорядокопераций, включаячтение памяти, имеетсущественное значени

5.5. Совместимостьиидентификацияпроцессоров 225

имеется возможность задания сериализации выполнения операций. Сериализа-ция означает, что все модификации флагов, регистров и памяти, выполняемые предыдущими инструкциями, должны завершиться до выборки из памяти и исполнения последующей инструкции. При этом очищается очередь предварительно выбранных инструкций. Инструкция CPU ID позволяет выполнять сериализацию на любомуровне привилегий.

Кроме быстродействия процессоры отличаются и некоторыми нюансами выполнения инструкций, которые обычно не влияют на выполнение программ, но могут использоваться для идентификации процессоров. Так, например, инструкция PUSH SP на процессоре 8086/88 исполняется иначе, чем на 80286 и более поздних версиях, — различие касается порядка выполнения декремента указателя стека и его сохранения встеке.

Процессорыпоследнихпоколений имеютархитектурныерасширения, полагаться на которые без предварительной идентификации типа процессора весьма рискованно. Определив возможности процессора, программа может эффективно использовать поддерживаемые им расширения архитектуры. Путем программирования регистров MSR можно управлять расширениями архитектуры, естественно, только всторону отключенияимеющихся возможностей.

5.5.2. Идентификацияпроцессоров

Возможность программного определения типа процессора была заложена в архитектуру процессоров х86 с самого начала. В любом процессоре IA-32 сразу после аппаратного сброса в регистре (E)DX можно прочитать номер семейства (3 — 386, 4

— 486, 5 — Pentium, 6 — Р6...), модели, типа и степпинга. Начиная с процессоров Pentium, появилась инструкция CPU ID, по которой любая программа на любом уровне привилегий в любой момент времени может получить ту же информацию, что и BIOS после сброса, и, вдобавок, 32-битный набор флагов расширений базовой архитектуры, реализованных в данном процессоре. Полученную информацию программа может использовать, например, для выбора исполняемого кода, оптимального для данного процессора (или отказа исполнения на «недостойном» ее процессоре), а также для настройки констант программных реализаций задержек. Инструкция CPUID поддерживалась и в ряде последних моделей процессоров класса 486. Формат инструкции практически безгранично расширяем, с ее помощью процессор может выдать хоть весь свой словесный портрет (если эту возможность заложат его разработчики). Однако информация для CPUID «зашивается» в процессор на этапе изготовления кристалла, что не позволяет, например, «выпытать» у процессора его официальную тактовую частоту (она определяется позже — на этапе тестирования уже готового процессора). Эта информация была бы полезна для борьбы, например, с пиратским разгоном (перемаркировкой) процессоров, что, в общем-то, волнует изготовителя.

В процессоре Pentium II Хеоп имеется специальная постоянная (только для чтения) память процессорной информации PIROM (Processor Information ROM), которая хранит такие данные, как электрические спецификации ядра процессора и кэш-памяти (диапазоны частот и питающих напряжений), степпинг и 64-битный серийный номер процессора. Кроме того, имеется энергонезависимая