- •Пояснительная записка

- •Введение

- •3.2. Выбор наилучшего варианта реализации

- •Выбор и описание используемой серии элементов

- •4.1. Выбор типа системы элементов и конкретной серии

- •4.2. Описание элементов используемой серии в целом

- •4.3. Условные обозначения, назначение отдельных выводов и технические характеристики конкретных микросхем, используемых в разрабатываемом узле.

- •Тм2 (к555тм2) - два d-триггера со сбросом и предустановкой

- •5 Выбор и описание интерфейсных микросхем, необходимых для сопряжения разрабатываемого узла с заданным интерфейсом

- •6. Разработка принципиальной схемы узла, включая схему сопряжения с интерфейсом

- •7. Ориентировочный расчет мощности и максимального времени переходных процессов

- •7.1. Расчет максимального времени переходных процессов.

- •7.2. Расчет мощности

- •8. Заключения и выводы по проделанной работе

- •9. Список использованной литературы

Министерство образования и науки РФ

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина) (СПбГЭТУ)

Кафедра ВТ

Пояснительная записка

к курсовой работе по дисциплине

«Узлы и устройства ЭВМ»

Вариант №10

Выполнил: Головин В.В.

группа 1305

Преподаватель: Фураев И.А.

Санкт-Петербург

2014 г.

Содержание

1. Задание……………………………………………………………………………………...3

2. Введение…………………………………………………………………………………….4

3 Сравнительный анализ возможных вариантов реализации……………………………..5

3.1 Описание возможных вариантов реализации разрабатываемого узла на уровне функциональных схем без конкретизации логического базиса………………….….5

3.1.1. Схема на основе реверсивного счетчика……………………………...…..5

3.1.2. Схема на основе компаратора…………………………………………......6

3.2 Выбор наилучшего варианта реализации………………………………………..8

4 Выбор и описание используемой серии элементов……………………………………...9

4.1 Выбор типа системы элементов и конкретной серии…………………………....9

4.2 Описание элементов используемой серии в целом……………………..……….9

4.3 Условные обозначения, назначение отдельных выводов и технические характеристики конкретных микросхем, используемых в разрабатываемом узле...10

5. Выбор и описание интерфейсных микросхем, необходимых для сопряжения разрабатываемого узла с заданным интерфейсом………………………………………….12

6. Разработка принципиальной схемы узла, включая схему сопряжения с интерфейсом..13

7. Ориентировочный расчет максимального времени переходных процессов в схеме и потребляемой мощности………………………………………………………………………14

7.1 Расчет максимального времени переходных процессов………………………….14

7.2 Расчет потребляемой мощности…………………………………………………….14

8. Заключения и выводы по проделанной работе……………………………………………14

9. Список используемой литературы…………………………………………………………14

Задание

Шифр: задание – 10, вариант – 1, система элементов – 6, критерий затрат – 2.

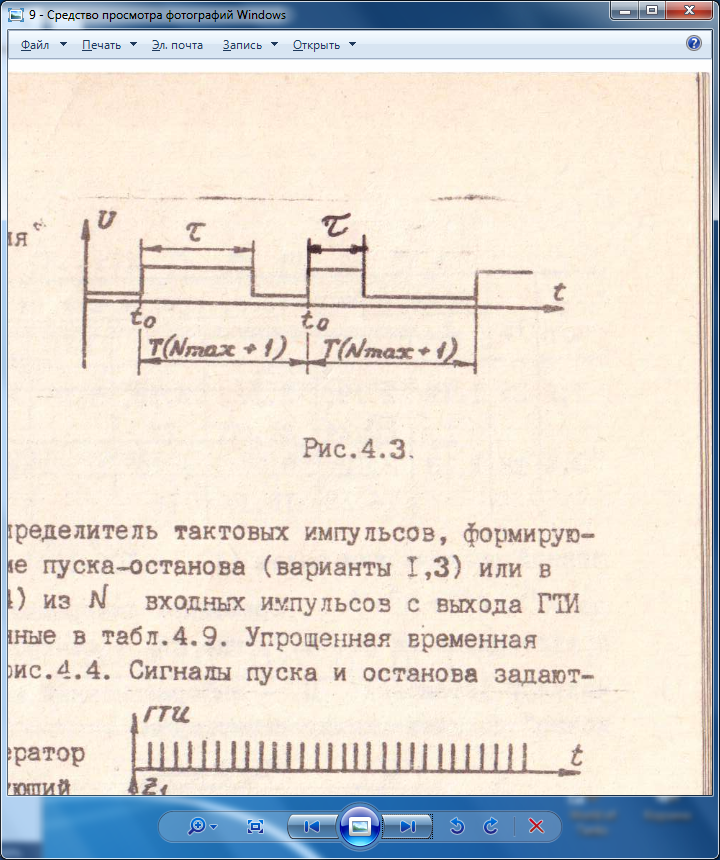

Рисунок 1. Упрощенная временная диаграмма работы преобразователя.

Разработать узел для преобразования n-разрядного параллельного кода в широтно-модулированный импульсный сигнал. Пример выхода представлен на рисунке 1.

Узел работает в режиме запуска-останова. Входной код, сигналы пуска и останова постопают из процессора.

Моменты приема информации отстоят друг от друга на время T(Nmax+1), где T – период сигнала, Nmax – максимальное числовое значение входного кода.

Разрядов n=8.

Система элементов ТТЛШ (серии 530, 531, 533, 1533), критерий затрат – максимум быстродействия.

Тип используемого интерфейса – Microbus.

Введение

Микроэлектроника является одной из наиболее быстро развивающихся областей науки и техники. Непрерывно улучшаются технические характеристики и расширяются функциональные возможности микроэлектронных изделий – интегральных схем. Совершенствование микросхем достигается благодаря прогрессу в физике, технологии и схемотехники.

Все разнообразные средства цифровой техники: ЭВМ, микропроцессорные системы измерения и автоматизации технологических процессов, цифровая связь и телевидение и т.д. строятся на единой элементной базе, в состав которой входят чрезвычайно разные по сложности микросхемы – от логических элементов, выполняющих простейшие операции, до сложнейших программируемых кристаллов, содержащих миллионы логических элементов.

Важнейшей задачей, решаемой с помощью методов и средств микросхемотехники, является схемотехническая разработка новых типов интегральных схем. Одним из крупнейших достижений микроэлектроники и вычислительной техники является создание микропроцессоров.

Следует заметить, что отсутствие отечественных микросхем современного уровня компенсируется сейчас доступностью зарубежной элементной базой.

Сравнительный анализ возможных вариантов реализации

3.1. Описание возможных вариантов реализации разрабатываемого узла на уровне функциональных схем без конкретизации логического базиса

Схема на основе реверсивного счетчика

Необходимо получить широтно-модулированный импульсный сигнал из 8-разрядного параллельного кода. Для этого используем реверсивные счетчики с предустановкой.

Процессор формирует прямой параллельный код и подает на порт процессора, затем производится предустановка счетчиков потенциальным сигналом. Далее вырабатывается сигнал старта (фронт) на D-триггер, у которого на выходе при сигнале START формируется единичный потенциальный сигнал. Запускается счетчик. Так как код на входе у нас прямой, следовательно, с каждым тактом необходимо вычитать единицу; при переполнении первого счетчика (когда все разряды Q0..Q3 равны нулю) происходит перенос на следующий счетчик. Так происходит до тех пор, пока выходы обоих счетчиков не будут равны нулю. Выход переноса второго счетчика подается на вход D-триггера. Выход на D-триггере становится равным нулю на процессор идет сигнал, уведомляющий о завершении работы. Для выполнения следующего цикла сброс счетчиков не требуется, так как выполняется предустановка.

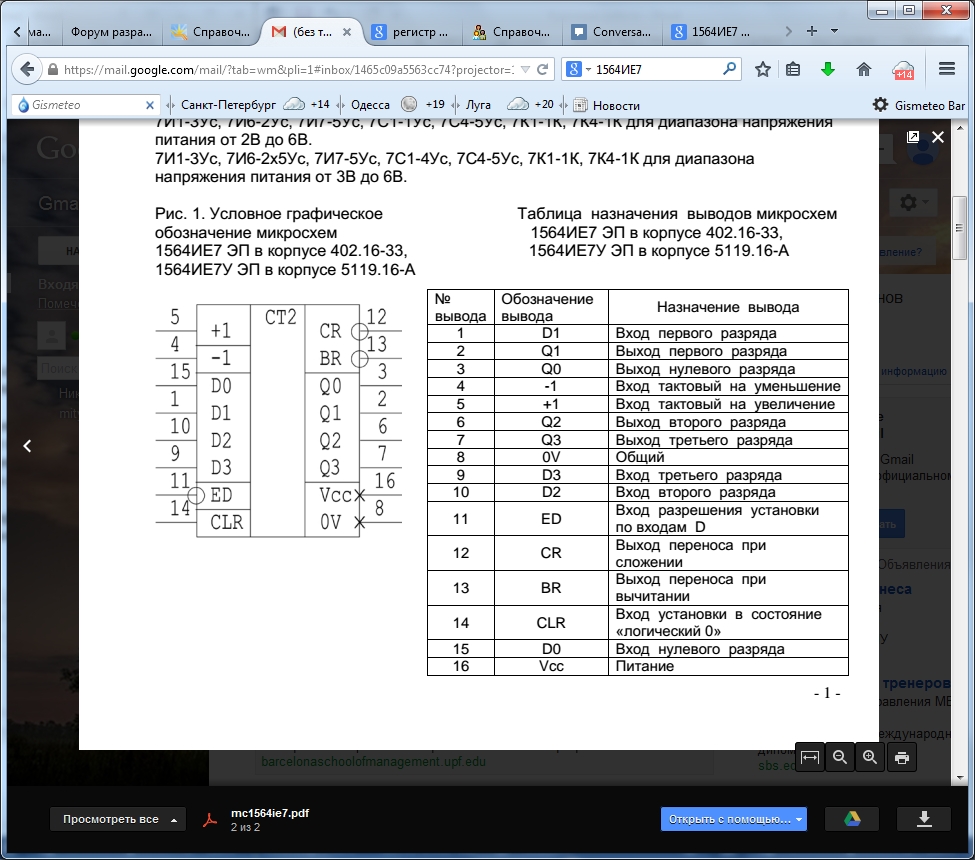

Реализуем счетчики наращиванием на основе четырёхразрядных счетчиков. В качестве примера возьмем синхронные реверсивные 533ИЕ7: К555ИЕ7 (двоичный, рис. 2).

Рисунок 2. Счетчик К555ИЕ7.

Функциональная схема узла предоставлена в приложении 1.

Временная диаграмма работы схемы (для одного из счетчиков) представлена в приложении 3.

Схема на основе компаратора

Необходимо получить широтно-модулированный импульсный сигнал из 8-разрядного параллельного кода. Для этого возьмем компаратор с двоичным счетчиком.

Процессор формирует

прямой параллельный код, который подается

из портов процессора на входы P0..P7

компараторов. Далее вырабатывается

сигнал старта (фронт) на D-триггер,

у которого на выходе при сигнале START

формируется единичный потенциальный

сигнал. Производится запуск первого

двоичного счётчика. Код с выхода счетчика

сравнивается с кодом, который подается

из портов процессора на компаратор,

когда они будут равны на выходе “=”

появится ноль. Запустится второй счетчик.

Так происходит до тех пор, пока последний

третий компаратор не выдаст на выходе“=”

( )

ноль. Выходы компараторов через элемент

“или” подаются на входCL

D-триггера.

Выход на D-триггере

становится равным нулю, на процессор

идет сигнал, уведомляющий о завершении

работы. Для выполнения следующего цикла

сброс счетчиков выполняется процессором

через Reset.

)

ноль. Выходы компараторов через элемент

“или” подаются на входCL

D-триггера.

Выход на D-триггере

становится равным нулю, на процессор

идет сигнал, уведомляющий о завершении

работы. Для выполнения следующего цикла

сброс счетчиков выполняется процессором

через Reset.

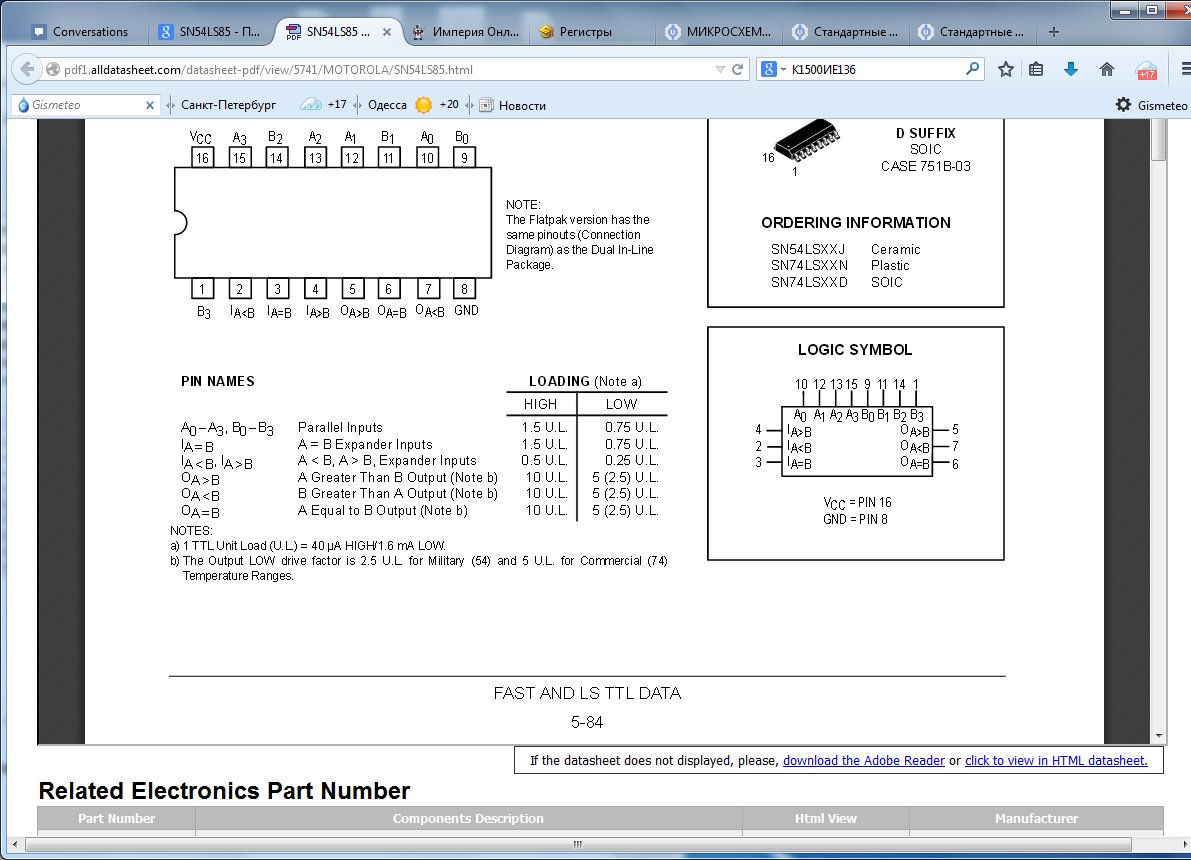

В качестве примера возьмем четырехразрядный компаратор К555СП1, аналог приведен на рисунке 3 (SN74LS85).

Рисунок 3. 4-разрядный цифровой компаратор К555СП1.

Функциональная схема узла предоставлена в приложении 2.