- •Программируемые цифровые устройства (часть 1) содержание

- •1 Микропроцессор. Основные сведения

- •Основные характеристики мп

- •1.2 Архитектура микропроцессора. Основные понятия

- •1.2.2 Состав типичного микроконтроллера

- •1.3 Структура мп устройства.

- •1.3.1 Мп с микропрограммным управлением (микропрограммируемая архитектура)

- •Структурная схема устройства микропрограммного управления

- •Структура микро эвм с микропрограммным управлением

- •1.4 Запоминающие устройства.

- •1.4.1 Оперативное запоминающее устройство

- •Статическое озу на биполярных и полевых транзисторах

- •1.4.2 Постоянные зу

- •Однократно программируемое пзу

- •1.5 Команды, форматы команд, система команд

- •1.6 Принцип работы микропроцессора.

- •1.6.1 Модель программирования микропроцессора.

- •1.7 Способы адресации

- •1.8 Основы программирования. Ассемблер.

- •1.9 Организация передачи информации в мпс. Интерфейс.

- •2 Архитектура 8- разрядных микроконтроллеров.

- •2.1 Последовательные интерфейсы микропроцессорных систем

- •2.1.1 Последовательный интерфейс rs-232c

- •2.1.2 Шина 1-Wire

- •Формат команды 1-Wire протокола

- •2.1.3 Интерфейс can4

- •Топология сети can.

- •Data frame стандарта can 2.0a.

- •Побитовый арбитраж на шине can.

- •2.2 Организация портов ввода/вывода

- •2.3 Таймеры и процессоры событий

- •2.4 Ввод/вывод аналоговых сигналов

- •Структурная схема типового модуля ацп

- •Цап на основе таймера в режиме шим

- •2.5 Контроллеры последовательного ввода/вывода

- •2.5.1 Модуль последовательного обмена uart

- •Упрощенная структура модуля uart.

- •2.5.2 Последовательный периферийный интерфейс spi

- •2.5.3 Синхронный последовательный интерфейс i2c

- •Временные диаграммы шины i2c

- •Взаимосинхронизация на шине i2c

- •2.6 Минимизация потребления энергии

- •2.7 Повышение надежности работы мк

- •2.7.1 Мониторинг напряжения питания мк

- •Временные диаграммы работы схемы por

- •Переход мк в состояние сброса по сигналам схемы por и модуля пониженного напряжения питания

- •2.7.2 Сторожевой таймер

- •Структурная схема сторожевого таймера

- •Принцип действия сторожевого таймера

- •3 Периферийные устройства

- •3.1 Генератор и схема начального сброса

- •3.2 Кнопки и датчики

- •3.3 Подключение светодиодных индикаторов

- •3.4 Подключение жидкокристаллических индикаторов

- •3.5 Комбинированное использование портов

- •3.6 Подключение реле и электромагнитных исполнительных устройств

- •3.7 Подключение мк к компьютеру через последовательный порт

- •3.8 Подключение интегрального датчика температуры с интерфейсом 1- Wire

- •4 Микроконтроллеры с архитектурой mcs-51

- •4.1 Особенности архитектуры mcs-51

- •4.2 Структура микроконтроллеров mcs-51

- •4.2.1 Внутренняя структура mcs-51

- •Структура микроконтроллера mcs-51

- •4.2.2 Организация памяти и программно доступные ресурсы

- •Организация памяти в микроконтроллерах семейства 8051

- •4.2.3 Система команд и методы адресации

- •4.3 Современные мк с архитектурой mcs-51

- •5 Микроконтроллеры с risc- архитектурой

- •5.2 Однокристальные risc- контроллеры avr

- •5.2.1 Способы адресации в микроконтроллерах avr

- •5.3 Микроконтроллеры семейства msp430

- •5.3.1 Архитектура

- •5.3.2 Система тактирования

- •5.3.3 Встроенная эмуляция

- •5.3.4 Адресное пространство

- •5.4 Сравнение микроконтроллеров различных семейств

- •6 Разработка систем на бис программируемых цифровых устройств

- •6.1 Основы проектирования систем на микроконтроллерах и плис

- •6.2 Технология разработки микропроцессорных контроллеров

- •6.2.1 Основные этапы цикла разработки микропроцессорного контроллера

- •Литература

5.3.4 Адресное пространство

Семейство MSP430 имеет фон Неймановскую архитектуру с единым адресным пространством для регистров специального назначения (SFR), периферии, ОЗУ и Flash-памяти программ. Общий объем адресуемой памяти составляет 64 кБ.

Рис. – Карта памяти MSP 430

Конкретное распределение памяти можно узнать из справочных данных на интересующее устройство. Доступ к программному коду выполняется всегда по четным адресам. Данные могут быть доступны как байты или как слова.

Flash-память программ

Начальный адрес Flash-памяти зависит от объема имеющейся памяти и различается для разных устройств. Конечный адрес Flash-памяти всегда 0FFFFh. Flash- память может использоваться как для программного кода, так и для данных. Байты или слова таблиц данных могут сохраняться и использоваться непосредственно в Flash-памяти, что исключает необходимость копировать эти таблицы в ОЗУ перед дальнейшим использованием.

Таблица векторов прерываний занимает верхние 16 слов адресного пространства Flash-памяти, при этом вектор прерывания с наивысшим приоритетом находится в самом верхнем адресном слове Flash-памяти (0FFFEh).

ОЗУ

ОЗУ начинается с адреса 0200h. Конечный адрес ОЗУ зависит от объема представленной памяти и различается для каждого конкретного устройства. ОЗУ может использоваться как для программного кода, так и для данных.

Периферийные модули

Периферийные модули отображены в адресном пространстве. Адреса с 0100 до 01FFh зарезервированы для 16-разрядных периферийных модулей. Они будут доступны с помощью команд-слов. Если используются однобайтные команды, допустимы только четные адреса, при этом старший байт результата всегда будет содержать "0".

Адресное пространство с 010h no 0FFh зарезервировано для 8-разрядных периферийных модулей. Эти модули доступны с помощью однобайтных команд. Чтение байтов модулей с помощью команд-слов приведет к появлению в старшем байте непредсказуемого содержимого. Если в байт модуля будут записываться данные в виде слова, то в регистре периферийного модуля сохранится только младший байт этого слова, старший будет проигнорирован.

Регистры специального назначения (SFRs)

Некоторые функции периферии конфигурируются в SFRs. Регистры специального назначения расположены в низших 16-ти байтах адресного пространства и организованы в виде байтов. Обращение к регистрам SFRs производится только с использованием однобайтных команд. Назначение отдельных битов регистров SFRs описывается в техническом руководстве на каждое конкретное устройство.

Организация памяти

Байты расположены в четных или нечетных адресах Слова располагаются только в четных адресах.

Рис. – Биты, байты и слова в памяти, организованной побайтно

При работе с командами-словами должны использоваться только четные адреса. Младший байт слова всегда расположен по четному адресу. Старший байт – в следующем нечетном адресе Например, если слово данных расположено по адресу ххх4h, то младший байт слова данных будет иметь адрес ххх4h, а старший байт слова адрес xxx5h.

5.4 Сравнение микроконтроллеров различных семейств

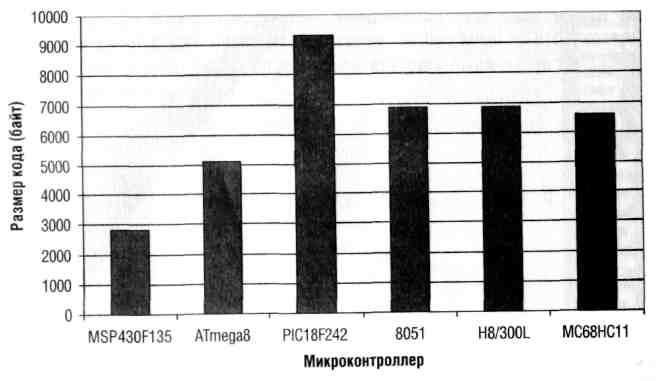

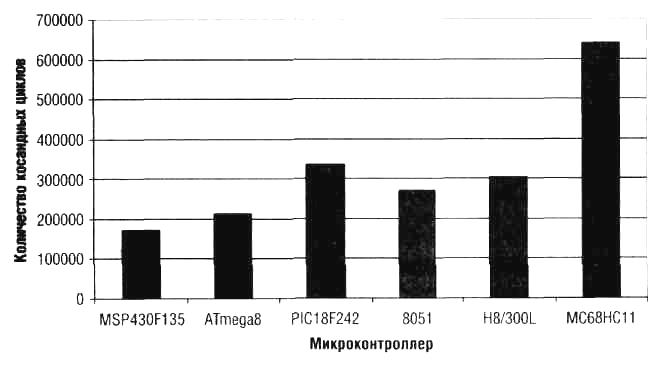

Здесь приведены результаты сравнения микроконтроллеров нескольких производителей. Для разработки кода различных простейших операций и выполнения его в режиме симулятора была использована платформа разработчика Embedded Workbench™ компании IAR Systems. Эти часто используемые приложения были выполнены на каждом микроконтроллере. Для всех рассмотренных применений были посчитаны суммарные размер кода программы и количество командных циклов, требуемых для выполнения. На рисунке 1 и рисунке 2 приведены диаграммы сравнения размеров кодов программ и количество командных циклов для каждого исследованного микроконтроллера.

Диаграмма сравнения суммарных размеров кодов программ

Диаграмма сравнения суммарного количества командных циклов

В таблице приведены коэффициенты деления частоты задающего генератора для формирования сигналов синхронизации вычислительного ядра рассмотренных микроконтроллеров. Полное время выполнения любого кода можно рассчитать как произведение количества командных циклов и коэффициента деления.

Таблица – Коэффициенты деления частоты задающего генератора для формирования сигналов синхронизации вычислительного ядра

-

Микроконтроллер

Коэффициент деления

MSP430F135

1

АТ Mega 8

1

PIC18F242

4

8051

12

H8/300L

2

МС68НС11

4