- •Декомпозиция задачи ввода данных в озу

- •Структуры данных

- •Разработка структуры данных программы для ввода данных в озу

- •Алгоритмизация программы

- •Подходы к алгоритмизации

- •Иерархическая организация алгоритма

- •Алгоритмизация программы для ввода данных в озу

- •1. Модуль "Тестовый контроль озу по шд" (dTstContr)

- •2. Модуль "Тестовый контроль озу по ша" (aTstContr)

- •3. Модуль "Вывод сообщений об ошибках" (ErMesOut)

- •4. Модуль "Ввод режимов" (ModeInput)

- •5. Модуль "Вывод сообщения о типе ввода" (InTpMesOut)

- •6. Модуль "Ввод с клавиатуры" (KbdInput)

- •7. Модуль "Контроль ввода с клавиатуры" (KbdInContr)

- •8. Модуль "Преобразование очередной цифры" (NxtDigTrf)

- •9. Модуль "Формирование информации" (InfoForm)

- •10. Модуль "Формирование массивов отображения" (DispForm)

- •11. Модуль "Вывод числовой информации" (NumInfOut)

- •12. Модуль "Функциональная подготовка" (FuncPrep)

- •3.4.4. Кодирование программы

- •Реализация логических конструкций структурного программирования

- •Кодирование программы для ввода данных в озу

- •3.4.5. Тестирование и отладка программы

- •3.4.6. Занесение программы на рабочий носитель

- •3.4.7. Оформление документации на программу

- •3.5. Проектирование аппаратных средств

- •3.5.1. Схемотехническое проектирование процессора

- •3.5.2. Схемотехническое проектирование памяти

- •Банкирование памяти

- •Организация банков памяти

- •Проектирование запоминающих устройств

- •3.5.3. Схемотехническое проектирование интерфейса

- •Организация ввода/вывода данных

- •3.5.4. Тестирование и настройка аппаратных средств

- •Тестирование статическими сигналами

- •Свободный прогон микропроцессора

- •3.6. Комплексная отладка микропроцессорной системы

- •Заключение

- •Список рекомендуемых источников

1. Модуль "Тестовый контроль озу по шд" (dTstContr)

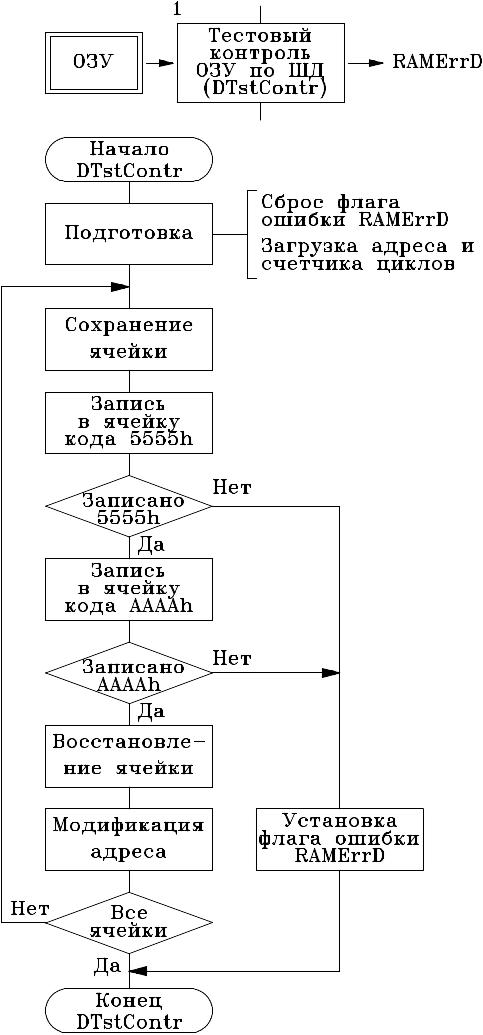

Этот модуль служит для тестового контроля ОЗУ по ШД (см. рис. 3.24).

В процессе эксплуатации устройства работоспособность ОЗУ может нарушаться. При этом в общем случае возникают два типа ошибок: ошибки по ШД и ошибки по ША.

Ошибки по ШД проявляются в том, что из ОЗУ считываются данные, отличающиеся от тех, которые в него записывались МП. Эти ошибки возникают вследствие неисправностей в линиях ШД (обрывы, замыкания), а также в аппаратных средствах ОЗУ с этой стороны.

Для выявления подобных ошибок необходимо попытаться записать в каждую ячейку ОЗУ два взаимнообратных решетчатых кода 5555h и AAAAh. Если это удается для всех ячеек, то ОЗУ работоспособно. В противном случае ОЗУ неисправно, и необходимо зафиксировать ошибку.

Эта идея реализована ГСА модуля DTstContr, приведенной на рис. 3.26. Для сохранения информации в тестируемом ОЗУ содержимое каждой ячейки сохраняется перед ее контролем, а затем восстанавливается.

Для удобства разработки алгоритма на этом же рисунке приведена выкопировка из макроуровня программы (см. рис. 3.24), относящаяся к этому модулю. Она наглядно представляет обрабатываемые модулем входные и выходные данные, не позволяя забыть ни об одном из них.

2. Модуль "Тестовый контроль озу по ша" (aTstContr)

Этот модуль предназначен для реализации тестового контроля ОЗУ по ША (см. рис. 3.24).

Ошибки по ША проявляются в том, что некоторые данные записываются не в те ячейки, которые адресуются МП. Эти ошибки возникают вследствие неисправностей в линиях ША (обрывы, замыкания), а также в аппаратных средствах ОЗУ с этой стороны. Они приводят к совмещению нескольких ячеек памяти и, следовательно, к уничтожению ранее записанных данных (по одному адресу) путем записи новых данных (по другому адресу).

Рис. 3.26. Алгоритм модуля "Тестовый контроль ОЗУ по ШД"

Для выявления подобных ошибок необходимо во все ячейки ОЗУ сначала записать некоторый закономерно изменяющийся код (как правило, адрес той же ячейки), а затем проанализировать записанные числа. При исправности ОЗУ наложение ячеек отсутствует, и считанное содержимое каждой из них будет равно ее адресу. В противном случае ячейки памяти накладываются друг на друга, что приведет к замене ранее записанного числа другим (позже записываемым) числом. В результате считанное содержимое некоторых ячеек не будет совпадать с их адресом. При обнаружении этого факта необходимо зафиксировать ошибку.

Эта идея реализована ГСА модуля ATstCotr, приведенной на рис. 3.27. Для уменьшения времени выполнения модуля тестируются не все ячейки ОЗУ, а лишь так называемые ячейки влияния. К ним относится ячейка по нулевому адресу, а также 16 ячеек, в адресе которых имеется единственный единичный бит (А0, А1, А2, . . ., А15). Для сохранения информации в ячейках влияния их содержимое сохраняется перед тестированием и восстанавливается после него.

3. Модуль "Вывод сообщений об ошибках" (ErMesOut)

Задачей этого модуля является вывод на знакосинтезирующие дисплеи сообщений о соответствующих ошибках на основании анализа признаков ошибок ввода с клавиатуры и тестового контроля (см. рис. 3.24).

ГСА модуля ErMesOut приведена на рис. 3.28. При одновременном наличии обеих ошибок тестового контроля ОЗУ на дисплей будет выведено сообщение об отказе ОЗУ по шине данных. Такое решение обусловлено тем, что при неисправной шине данных тест шины адреса гарантированно зафиксирует ошибку даже при отсутствии неисправности в ней.