- •Декомпозиция задачи ввода данных в озу

- •Структуры данных

- •Разработка структуры данных программы для ввода данных в озу

- •Алгоритмизация программы

- •Подходы к алгоритмизации

- •Иерархическая организация алгоритма

- •Алгоритмизация программы для ввода данных в озу

- •1. Модуль "Тестовый контроль озу по шд" (dTstContr)

- •2. Модуль "Тестовый контроль озу по ша" (aTstContr)

- •3. Модуль "Вывод сообщений об ошибках" (ErMesOut)

- •4. Модуль "Ввод режимов" (ModeInput)

- •5. Модуль "Вывод сообщения о типе ввода" (InTpMesOut)

- •6. Модуль "Ввод с клавиатуры" (KbdInput)

- •7. Модуль "Контроль ввода с клавиатуры" (KbdInContr)

- •8. Модуль "Преобразование очередной цифры" (NxtDigTrf)

- •9. Модуль "Формирование информации" (InfoForm)

- •10. Модуль "Формирование массивов отображения" (DispForm)

- •11. Модуль "Вывод числовой информации" (NumInfOut)

- •12. Модуль "Функциональная подготовка" (FuncPrep)

- •3.4.4. Кодирование программы

- •Реализация логических конструкций структурного программирования

- •Кодирование программы для ввода данных в озу

- •3.4.5. Тестирование и отладка программы

- •3.4.6. Занесение программы на рабочий носитель

- •3.4.7. Оформление документации на программу

- •3.5. Проектирование аппаратных средств

- •3.5.1. Схемотехническое проектирование процессора

- •3.5.2. Схемотехническое проектирование памяти

- •Банкирование памяти

- •Организация банков памяти

- •Проектирование запоминающих устройств

- •3.5.3. Схемотехническое проектирование интерфейса

- •Организация ввода/вывода данных

- •3.5.4. Тестирование и настройка аппаратных средств

- •Тестирование статическими сигналами

- •Свободный прогон микропроцессора

- •3.6. Комплексная отладка микропроцессорной системы

- •Заключение

- •Список рекомендуемых источников

3.5.3. Схемотехническое проектирование интерфейса

Для ввода/вывода данных в МПС на базе МП ВМ86/ВМ88 могут использоваться два типа структур интерфейса:

структура с изолированным интерфейсом;

структура с неизолированным или общим интерфейсом.

В структуре с неизолированным интерфейсом порты ввода/вывода рассматриваются как ячейки памяти, и обращение к ним осуществляется сигналами чтения и записи . Это обеспечивает высокую гибкость ввода/вывода, т. к. любая команда обращения к памяти выполняет обращение и к интерфейсу. Однако при этом проблема распределения адресного пространства МП распространяется и на интерфейс, что может привести к усложнению селектирующих дешифраторов. Кроме того, команды обращения к памяти выполняются дольше и имеют больший формат. Использование такой структуры интерфейса необходимо для пересылки блоков данных между ЗУ и УВВ с помощью строковых команд.

В

структуре с изолированным интерфейсом

ввод/вывод данных осуществляется

командами ввода IN и вывода OUT, а обращение

к портам сигналами

ввода

![]() и вывода

и вывода

![]() .

Это обеспечивает передачу данных между

портами и аккумуляторами МП. В зависимости

от типа аккумулятора (AL или AX), указанного

в команде, осуществляется обмен байтами

или словами. Изолированное адресное

пространство ввода/вывода не сегментировано

и составляет 64 Кбайт. При этом первые

256 портов могут адресоваться прямо или

косвенно, а остальные

только косвенно. Прямой адрес port

представляется байтом и указывается в

команде, а косвенный адрес выбирается

из регистра DX.

.

Это обеспечивает передачу данных между

портами и аккумуляторами МП. В зависимости

от типа аккумулятора (AL или AX), указанного

в команде, осуществляется обмен байтами

или словами. Изолированное адресное

пространство ввода/вывода не сегментировано

и составляет 64 Кбайт. При этом первые

256 портов могут адресоваться прямо или

косвенно, а остальные

только косвенно. Прямой адрес port

представляется байтом и указывается в

команде, а косвенный адрес выбирается

из регистра DX.

Допустимые форматы команд ввода/вывода и полное описание реализуемых ими функций приведены в табл. 3.5.

Таблица 3.5

Форматы и функции команд ввода/вывода

Форматы команд |

Описание функций |

IN AL, port |

(AL) (port) |

IN AX, port |

(AX) (port + 1:port) |

IN AL, DX |

(AL) ((DX)) |

IN AX, DX |

(AX) ((DX) + 1:(DX)) |

OUT port, AL |

(port) (AL) |

OUT port, AX |

(port + 1:port) (AX) |

OUT DX, AL |

((DX)) (AL) |

OUT DX, AX |

((DX) + 1:(DX)) (AX) |

Из этой таблицы следует, что обращение к портам осуществляется аналогично обращению к памяти.

При вводе данных командой IN байт вводится в регистр AL из порта с указанным адресом (port или (DX)), а слово в регистр AX из двух смежных адресов (port + 1:port или (DX) + 1:(DX)), причем младший байт передается в AX из порта с меньшим адресом.

Обращение к портам при выводе данных командой OUT осуществляется аналогичным образом.

При проектировании интерфейса необходимо обеспечить возможность схемотехнического обращения к портам в соответствии с табл. 3.5.

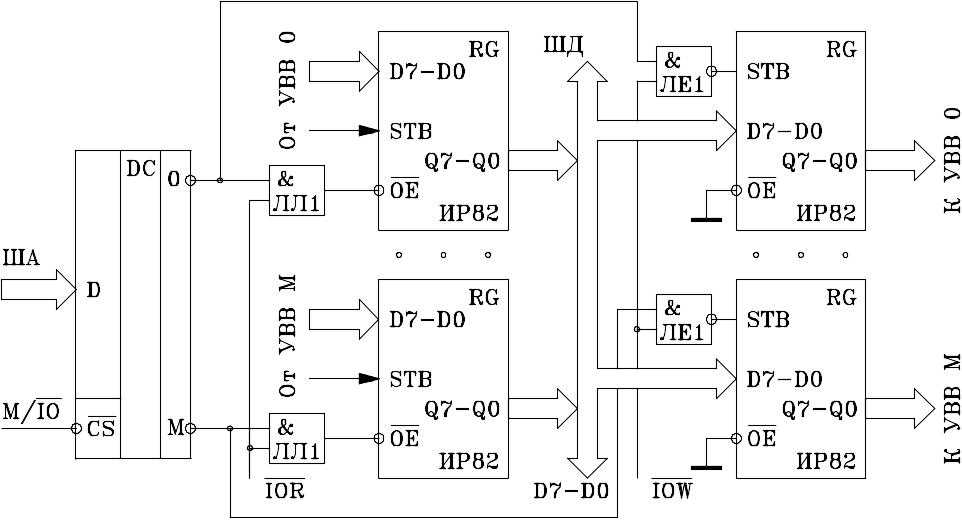

В

МПС на базе МП ВМ 88, имеющих однобайтную

шину данных, все порты ввода/вывода

подключаются к этой шине, а их выборка

осуществляется выходными сигналами с

дешифратора, декодирующего адрес портов,

появляющийся на шине адреса при выполнении

команд IN и OUT. Схема интерфейса с

использованием ИМС ИР82 в качестве портов

ввода/вывода приведена на рис. 3.52.

Учитывая кодирование адресных и

управляющих сигналов обращения к портам,

с целью упрощения интерфейса целесообразно

формировать сигналы выборки портов

ввода с помощью логических элементов

ИЛИ (К555ЛЛ1), а сигналы записи в порты

вывода с помощью

элементов ИЛИНЕ

(К555ЛЕ1). Для упрощения анализа при

настройке МПС адресный дешифратор DC

целесообразно стробировать сигналом

МП M/![]() ,

разделяющим адресные пространства

памяти и ввода/вывода, таким образом,

чтобы его работа разрешалась лишь при

обращении к интерфейсу.

,

разделяющим адресные пространства

памяти и ввода/вывода, таким образом,

чтобы его работа разрешалась лишь при

обращении к интерфейсу.

Для

адресации портов ввода и вывода можно

использовать отдельные дешифраторы,

стробируемые соответственно сигналами

![]() и

и

![]() .

В этом случае логических элементов для

формирования сигналов обращения к

портам не потребуется.

.

В этом случае логических элементов для

формирования сигналов обращения к

портам не потребуется.

Рис. 3.52. Схема интерфейса для МП ВМ88

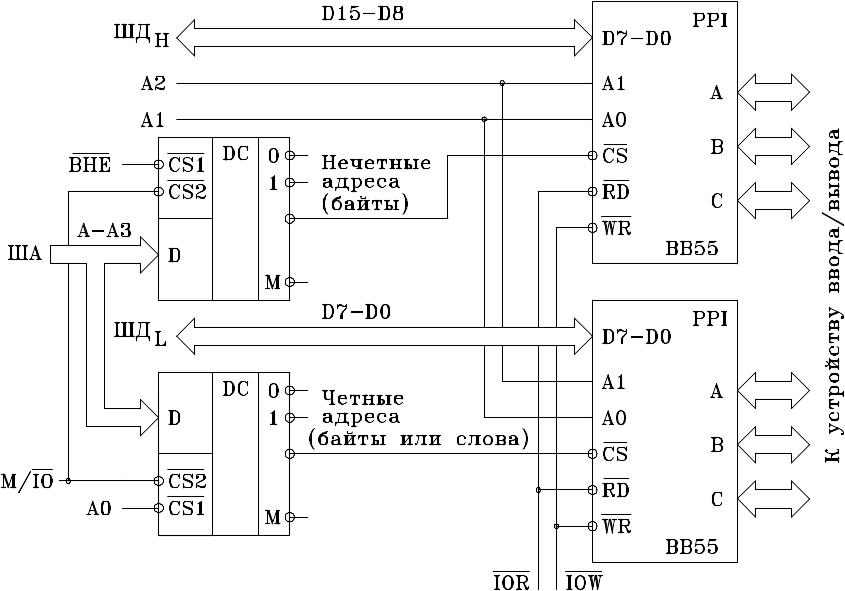

В МПС на базе МП ВМ86, имеющих двухбайтную шину данных, порты ввода/вывода однобайтных УВВ можно подключать к старшей или младшей половинам шины данных, равномерно распределяя нагрузку на эту шину. Все порты, подключенные к линиям D15D8 шины данных, должны иметь нечетные адреса (A0 = 1( = 0)), а порты, подключенные к ее линиям D7D0 четные адреса (A0 = 0). В этом случае четные и нечетные адреса дешифрируются отдельными дешифраторами, стробируемыми сигналами A0 и соответственно, и схема интерфейса с использованием ИМС КР580ВВ55А в качестве портов ввода/вывода приведена на рис. 3.53. Линии А2, А1 шины адреса используются для адресации внутренних регистров ВВ55.

Порты двухбайтных УВВ подключаются и к старшей и к младшей половинам шины данных. Обращение к портам осуществляется аналогично обращению к банкам памяти (см. табл. 3.4). При этом имеется возможность передавать как байты, так и слова по любому адресу. Для повышения производительности системы двухбайтные порты должны иметь четные адреса. Тогда чтение слова осуществляется за один цикл шины.

Рис. 3.53. Схема интерфейса для МП ВМ86

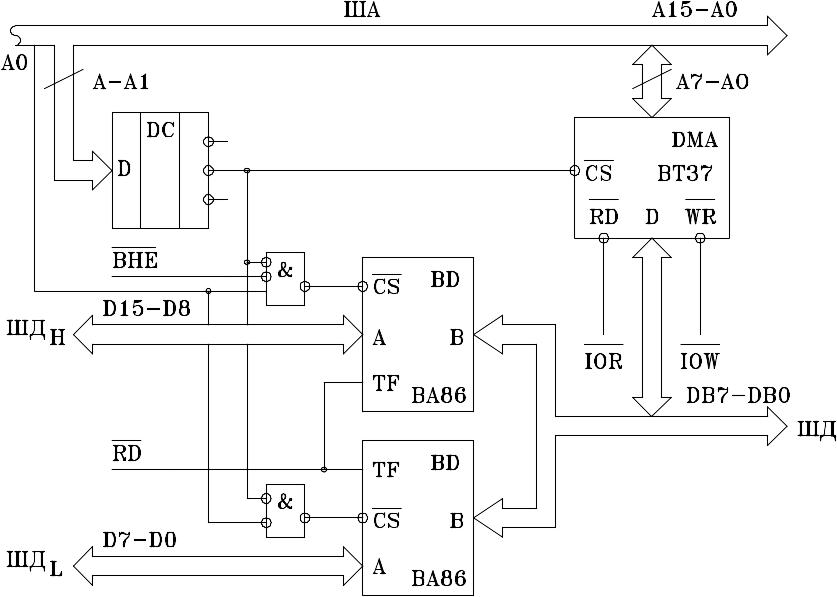

При необходимости обращения к одному и тому же однобайтному УВВ по последовательным адресам следует преобразовать двухбайтную шину данных МП ВМ86 в однобайтную в соответствии с рис. 3.54. Это, в частности, требуется при подключении контроллеров ПДП К1810ВТ37 и КР580ВТ57.

Обращение к УВВ, подключенному к внешней однобайтной шине данных осуществляется с помощью сигналов и A0 в соответствии с табл. 3.6. При обращении к УВВ на шине адреса появляется его адрес, декодируемый дешифратором. Сигнал на соответствующем выходе дешифратора DC активируется и разрешает по одному из входов логических элементов выборку шинных буферов.

При

передаче байтов с нечетным адресом

= 0, A0 = 1 и выбирается буфер, подключающий

линии D15D8 к внешней

шине данных. При передаче байтов с четным

адресом

= 1, A0 = 0 и выбирается буфер, подключающий

линии D7D0 к внешней

шине данных. Направление передачи данных

через шинные буферы определяется

сигналом

![]() ,

поступающим с МП. Буферы включаются

так, что в исходном состоянии они

подключены к системной шине данных

входами и лишь при вводе данных

подключаются к ней выходами.

,

поступающим с МП. Буферы включаются

так, что в исходном состоянии они

подключены к системной шине данных

входами и лишь при вводе данных

подключаются к ней выходами.

Рис. 3.54. Схема преобразования двухбайтной шины данных в однобайтную

Таблица 3.6

Доступ к порту на внешней шине

|

A0 |

Тип обращения |

0 |

0 |

Не используется (доступ запрещён) |

0 |

1 |

Байт с нечётным адресом на старшую половину шины (D15D8) |

1

|

0

|

Байт с чётным адресом на младшую половину шины (D7D0) |

1 |

1 |

Доступ отсутствует |

Комбинация сигналов = 0 и A0 = 0 никогда не должна появляться, т. к. при обращении к однобайтному УВВ команды передачи слов не используются. Однако, с целью защиты от ошибок программиста оба логических элемента выборки буферов застробированы сигналом A0 в противофазном значении. Поэтому при любом значении сигнала A0 может активироваться лишь один буфер, что гарантирует сохранность аппаратуры и при недопустимых обращениях.

Регистры УВВ, подключенного к внешней однобайтной шине данных, могут иметь как четные, так и нечетные адреса, выбираемые произвольным образом.