- •1.Основные архитектуры эвм и их сравнительная оценка (Неймановская, Гарвардская, risc, cisc, прочие). Понятие архитектуры, организации и реализации эвм

- •Принцип программного управления и машина фон Неймана

- •Архитектура системы команд. Архитектуры cisc и risc.

- •2.Базовая структура Неймановской машины. Порядок выполнения команд.

- •3.Система операций и форматы команд эвм. Структура и форматы команд эвм

- •Форматы команд эвм

- •5. Cisc-процессоры семейства 80х86 – основные блоки и их назначение.

- •6. Cisc-процессоры семейства 80х86. Блок выборки и декорирования команд (бвдк), очередь команд. Взаимодействие бвдк, iu,fpu.

- •7. Cisc-процессоры семейства 80х86. Регистровая структура операционного блока. Способы адресации(используемые в х86!!).

- •8. Cisc-процессоры семейства 80х86. Блок сегментации. Формирование адреса в линейном, действительном и защищенном режимах.

- •9.Иерархия памяти эвм.

- •10.Память «кэш» -назначение, основные структуры.

- •13.Ввод-вывод в программном режиме. Порт ввода-вывода.

- •14. Прерывания: определение, виды прерываний, порядок обслуживания внешних прерываний.

- •15.Приоритетные прерывания, контроллер прерываний.

- •17.Контроллер пдп.

- •18. Процессоры гарвардской архитектуры: общие принципы и архитектура микроконтроллера Intel 8051 (на основе лабораторных работ).

- •19.Принципы архитектуры risc. Способы адресации и форматы команд.

- •20. Процессоры Power-pc (м60х)-обрабатывающий блок (очередь команд, блок выдачи команд, fpu, iu, bpu).

- •22.Современные тенденции развития х86-современных процессоров.

- •23.Предсказание переходов в современных процессорах.

- •26. Системы массового параллелизма и многоядерные процессоры: структура, организация взаимодействий.

2.Базовая структура Неймановской машины. Порядок выполнения команд.

Фон-неймановская архитектура

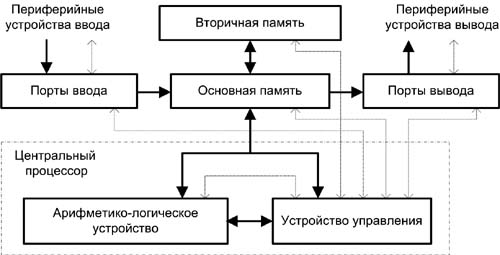

В статье фон Неймана определены основные устройства ВМ, с помощью которых должны быть реализованы вышеперечисленные принципы. Большинство современных ВМ по своей структуре отвечают принципу программного управления. Типичная фон-неймановская ВМ (рис. 1.3) содержит: память, устройство управления, арифметико-логическое устройство и устройство ввода/вывода.

Рис.

1.3.

Структура фон-неймановской вычислительной

машины

Рис.

1.3.

Структура фон-неймановской вычислительной

машины

В любой ВМ имеются средства для ввода программ и данных к ним. Информация поступает из подсоединенных к ЭВМ периферийных устройств (ПУ) ввода. Результаты вычислений выводятся на периферийные устройства вывода. Связь и взаимодействие ВМ и ПУ обеспечивают порты ввода и порты вывода. Термином порт обозначают аппаратуру сопряжения периферийного устройства с ВМ и управления им. Совокупность портов ввода и вывода называют устройством ввода/вывода (УВВ) или модулем ввода/вывода ВМ (МВВ).

Введенная информация сначала запоминается в основной памяти, а затем переносится во вторичную память, для длительного хранения. Чтобы программа могла выполняться, команды и данные должны располагаться в основной памяти (ОП), организованной таким образом, что каждое двоичное слово хранится в отдельной ячейке, идентифицируемой адресом, причем соседние ячейки памяти имеют следующие по порядку адреса. Доступ к любым ячейкам запоминающего устройства (ЗУ) основной памяти может производиться в произвольной последовательности. Такой вид памяти известен как память с произвольным доступом. ОП современных ВМ в основном состоит из полупроводниковых оперативных запоминающих устройств (ОЗУ), обеспечивающих как считывание, так и запись информации. Для таких ЗУ характерна энергозависимость — хранимая информация теряется при отключении электропитания. Если необходимо, чтобы часть основной памяти была энергонезависимой, в состав ОП включают постоянные запоминающие устройства (ПЗУ), также обеспечивающие произвольный доступ. Хранящаяся в ПЗУ информация может только считываться (но не записываться).

Размер ячейки основной памяти обычно принимается равным 8 двоичным разрядам — байту. Для хранения больших чисел используются 2, 4 или 8 байтов, размещаемых в ячейках с последовательными адресами. В этом случае за адрес числа часто принимается адрес его младшего байта. Так, при хранении 32-разрядного числа в ячейках с адресами 200, 201, 202 и 203 адресом числа будет 200. Такой прием называют адресацией по младшему байту или методом «остроконечников» (little endian addressing). Возможен и противоположный подход — по меньшему из адресов располагается старший байт. Этот способ известен как адресация по старшему байту или метод «тупоконечников» (big endian addressing)1. Адресация по младшему байту характерна для микропроцессоров фирмы Intel и мини-ЭВМ фирмы DEC, а по старшему байту — для микропроцессоров фирмы Motorola и универсальных ЭВМ фирмы IBM. В принципе выбор порядка записи байтов существенен лишь при пересылке данных между ВМ с различными формами их адресации или при манипуляциях с отдельными байтами числа. В большинстве ВМ предусмотрены специальные инструкции для перехода от одного способа к другому.

Для долговременного хранения больших программ и массивов данных в ВМ обычно имеется дополнительная память, известная как вторичная. Вторичная память энергонезависима и чаще всего реализуется на базе магнитных дисков. Информация в ней хранится в виде специальных программно поддерживаемых объектов — файлов (согласно стандарту ISO, файл — это «идентифицированная совокупность экземпляров полностью описанного в конкретной программе типа данных, находящихся вне программы во внешней памяти и доступных программе посредством специальных операций»).

Устройство управления (УУ) — важнейшая часть ВМ, организующая автоматическое выполнение программ (путем реализации функций управления) и обеспечивающая функционирование ВМ как единой системы. Для пояснения функций УУ ВМ следует рассматривать как совокупность элементов, между которыми происходит пересылка информации, в ходе которой эта информация может подвергаться определенным видам обработки. Пересылка информации между любыми элементами ВМ инициируется своим сигналом управления (СУ), то есть управление вычислительным процессом сводится к выдаче нужного набора СУ в нужной временной последовательности. Цепи СУ показаны на рис. 1.3 полутоновыми линиями. Основной функцией УУ является формирование управляющих сигналов, отвечающих за извлечение команд из памяти в порядке, определяемом программой, и последующее исполнение этих команд. Кроме того, УУ формирует СУ для синхронизации и координации внутренних и внешних устройств ВМ.

Еще одной неотъемлемой частью ВМ является арифметико-логическое устройство (АЛУ). АЛУ обеспечивает арифметическую и логическую обработку двух входных переменных, в результате которой формируется выходная переменная. Функции АЛУ обычно сводятся к простым арифметическим и логическим операциям, а также операциям сдвига. Помимо результата операции АЛУ формирует ряд признаков результата (флагов), характеризующих полученный результат и события, произошедшие в процессе его получения (равенство нулю, знак, четность, перенос, переполнение и т. д.). Флаги могут анализироваться в УУ с целью принятия решения о дальнейшей последовательности выполнения команд программы.

УУ и АЛУ тесно взаимосвязаны и их обычно рассматривают как единое устройство, известное как центральный процессор (ЦП) или просто процессор. Помимо УУ и АЛУ в процессор входит также набор регистров общего назначения (РОН), служащих для промежуточного хранения информации в процессе ее обработки.

зовая структура Неймановской машины. Порядок выполнения команды.

Структура фон-неймановской архитектуры вычислительной машины (ВМ). Структура ВМ с непосредственными связями; структура ВМ с общей шиной.

Информация на ВМ от периферийных устр-в ввода через модули (устр-ва) вывода поступают в основную память и далее обрабатываются основными программами. Результаты вычислительного процесса через модуль (устр-во) вывода передаются на периферийное устр-во вывода. Часть результатов передается во внешнюю память для долговременного хранения. Основная память в подавляющем большинстве случаев реализуется как память с произвольным доступом т.е. процессору в любой момент доступно содержимое ячейки.

Основная память делится на:

1) Оперативную память, хранящую слова используемые в вычислительном процессе

2) Постоянную память, ячейки которой содержат информацию предназначенную только для чтения и которая как правило не может быть изменена (перезаписана).

Оперативная память энергозависима т.е. информация хранится только в процессе работы.

Постоянная память не энергозависима.

Внешняя память реализована в виде накопителя на различных носителях, чаще всего на магнитных дисках. Эта память энергонезависима, отличается большим объемом и большим временем доступа.

Устр-во управления реализованное автоматическим выполнением программы путем реализации ф-ций управления, что позволяет работать ВМ как единой системе. Пересылка информации между любыми элементами, структурами инициируется сигналами управления, которые вырабатываются устр-вами управления. Сигнала управления используются для синхронизации и координации работы узлов и систем как самой ВМ, так и подключаемых периферийных устр-в.

Арифметико-логическое устр-во (АЛУ) выполняет арифметическую и/или логическую обработку входных переменных, в результате которой формируется выходная переменная. Помимо результата операции АЛУ формирует ряд признаков результата, характеризующих полученный результат и события произошедшие в ходе его получения (знак результата, рав-во нулю, четность, перенос).

Флаги используются устр-вом управления для анализа хода выполнения программы и изменения, при необходимости, естественной последовательности выполнения команд.

Устр-во управления и АЛУ совместно образуют структуру называемую центральным процессором.

Основные типы структур ВМ

Особенности определяющие достоинства и недостатки архитектуры ВМ изначально зависит от способа соединения (способа организации взаимодействия) основных структурных компонентов машины.

Различают 2 основных типа структур ВМ

1) Структура с непосредственными связями (классическая Фон Неймановская структура). Особенности связи в такой структуре (число линий в шине) определяется видом информации, характером и интенсивностью обмена. Основное достоинство такой структуры связано с возможностью устранения узких мест в информации, обмене путем изменения лишь отдельных связей, не затрагивая систему в целом. Основной недостаток – невозможность изменения, реконфигурации.

2) Структура на основе общей шины.

Общая шина служит для передачи всей информации. Достоинство – простота реализации ВМ, простота реконфигурирования. В каждый момент времени идет передача информации через шину. Основную нагрузку на шину создает общая информация между процессором и основной памятью, связанная с извлечением команды данных из памяти и запись в нее результатов вычислений. На долю операции ввода-вывода остается небольшая часть пропускной способности шины.