- •Классификация устройств управления. Устройства управления с жесткой и программируемой логикой.

- •Схемное устройство управления

- •Описание автоматов Мура и Мили на языке vhdl

- •Описание динамического триггера и дешифратора на языке vhdl

- •Описание шифратора и драйвера шины на языке vhdl.

- •Описание озу на языке vhdl

- •Программируемые логические матрицы. Программируемая матричная логика. Базовые матричные кристаллы.

- •Архитектура сложных программируемых логических устройств (cpld). Структура макроячейки (на примере xc9500)

- •Программируемые вентильные матрицы (fpga). Структура блока типа slicel в fpga Spartan3

- •Структура клб на примере Spartan-3

- •Структура блока типа slicel

- •Процесс проектирования цифровых устройств с использованием плис

- •Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по данным.

- •Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по управлению.

- •Архитектура конвейерного суперскалярного процессора: статическое и динамическое предсказание переходов.

Структура клб на примере Spartan-3

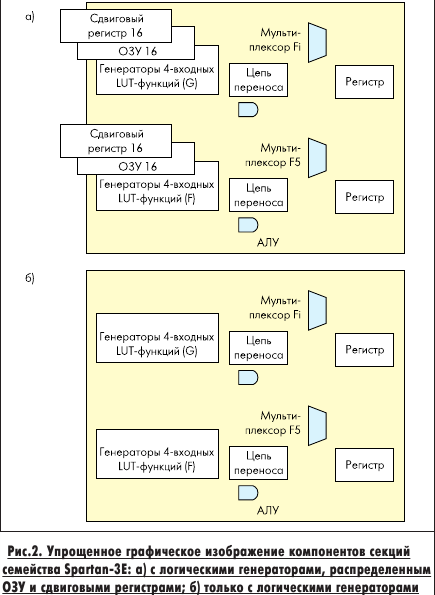

Каждый конфигурируемый логический блок (КЛБ) ПЛИС семейства Spartan-3 состоит из четырех секций, сгруппированных в пары, каждая пара имеет независимую цепь переноса. Левая пара называется SLICEM и содержит полнофункциональные логические генераторы, которые могут использоваться также в качестве распределенного ОЗУ или сдвигового регистра. Правая же пара – SLICEL – может реализовать только логику.

Все четыре секции содержат:

1. Два функциональных генератора.

2. Два элемента памяти.

3. Мультиплексоры, применяемые для создания функций пяти и более переменных.

4. Логику ускоренного переноса.

5. Логические вентили, предназначенные для реализации арифметических функций.

Функциональные генераторы реализованы в виде четырех входовых таблиц преобразования (Look-Up Table - LUT). Кроме использования в качестве функциональных генераторов, каждый LUT-элемент, расположенный в секции SLICEM, может быть также использован как синхронное ОЗУ размерностью 16x1 бит или 16-битовый сдвиговый регистр. Более того, из двух LUT-элементов в рамках одной секции можно реализовать синхронное ОЗУ размерностью 16х2 бита или 32х1 бит, либо двухпортовое синхронное ОЗУ размерностью 16х1 бит.

Запоминающие элементы в КЛБ могут конфигурироваться в виде динамических триггеров D-типа, чувствительных к фронту сигнала, или в виде триггеров-защелок, чувствительных к уровню сигнала.

Каждый КЛБ имеет внутренние быстродействующие линии связи и соединен с переключающей матрицей, осуществляющей доступ к глобальным трассировочным ресурсам.

Структура блока типа slicel

Каждая секция в блоке типа SLICEL (рис. 11) состоит из двух блоков LUT, двух схем сложения по модулю 2, схем формирования ускоренного переноса (элементы 1, 2, 3, 7, 8, 9, 13), мультиплексоров выбора режима (элементы 5, 6, 11, 12), двух динамических триггеров, схемы наращивания размерности мультиплексора (элемент 10), независимого мультиплексора 4. Адресные входы мультиплексоров на рис. 11 не показаны. Блок SLICEM отличается от блока SLICEL тем, что в нем реализована дополнительная схе-

ма управления сдвигом.

Секция в блоке SLICEL может функционировать в качестве:

• комбинационной схемы, реализующей функции Y и X от четырех переменных (G1..G4 и F1..F4) с помощью блока LUT и мультиплексоров 5 и 11;

• мультиплексора 4 с двумя входами FXINA и FXINB и адресным входом BY;

• комбинационной схемы, реализующей функцию F5 от девяти переменных (G1..G4, F1..F4, BX) на блоке LUT и мультиплексоре 10;

• мультиплексора с пятью адресными линиями (G1..G4 или F1..F4, BX) на блоке LUT и мультиплексоре 10;

• сумматора с ускоренным переносом, реализующего сложение двухразрядных чисел (G2F2, G1F1) с учетом переноса в младший разряд (CIN). С помощью двух элементов блока LUT вырабатываются функции F1 XOR F2 и G1 XOR G2. Эти функции используются для формирования разрядов суммы на элементах сложения

по модулю 2 с разрядом переноса, а также для формирования переноса в старший разряд с помощью мультиплексоров 3, 9 и мультиплексоров выбора режима 1, 2, 7, 8;

• двух триггеров для хранения сигналов Y и X или сигналов BX и BY.

Сумматор с ускоренным переносом может также функционировать в качестве счетчика при выборе на мультиплексорах 1 и 7 одного из двух разрядов чисел G и F и подаче единицы на вход CIN. Другие входы мультиплексоров 1 и 7 служат для задания константных значений.