- •Классификация устройств управления. Устройства управления с жесткой и программируемой логикой.

- •Схемное устройство управления

- •Описание автоматов Мура и Мили на языке vhdl

- •Описание динамического триггера и дешифратора на языке vhdl

- •Описание шифратора и драйвера шины на языке vhdl.

- •Описание озу на языке vhdl

- •Программируемые логические матрицы. Программируемая матричная логика. Базовые матричные кристаллы.

- •Архитектура сложных программируемых логических устройств (cpld). Структура макроячейки (на примере xc9500)

- •Программируемые вентильные матрицы (fpga). Структура блока типа slicel в fpga Spartan3

- •Структура клб на примере Spartan-3

- •Структура блока типа slicel

- •Процесс проектирования цифровых устройств с использованием плис

- •Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по данным.

- •Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по управлению.

- •Архитектура конвейерного суперскалярного процессора: статическое и динамическое предсказание переходов.

Схемное устройство управления

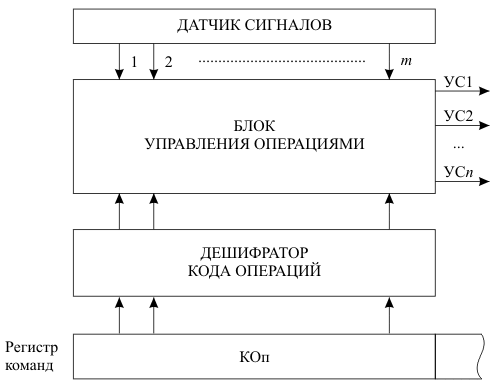

Устройство управления схемного типа состоит из:

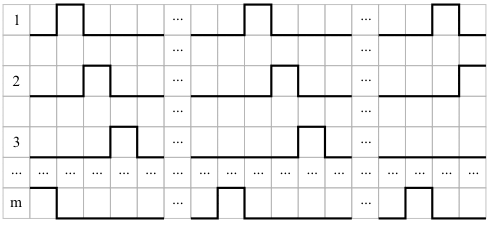

датчика сигналов, вырабатывающего последовательность импульсов, равномерно распределенную во времени по своим шинам

(n - общее количество управляющих сигналов, необходимых для выполнения любой операции; m - количество тактов, за которое выполняется самая длинная операция); Датчик сигналов обычно реализуется на основе счетчика с дешифратором или на сдвиговом регистре.

блока управления операциями, осуществляющего выработку управляющих сигналов, то есть коммутацию сигналов, поступающих с ДС, в соответствующем такте на нужную управляющую шину;

дешифратора кода операций, который дешифрирует код операции команды, присутствующей в данный момент в регистре команд, и возбуждает одну шину, соответствующую данной операции; этот сигнал используется блоком управления операциями для выработки нужной последовательности управляющих сигналов.

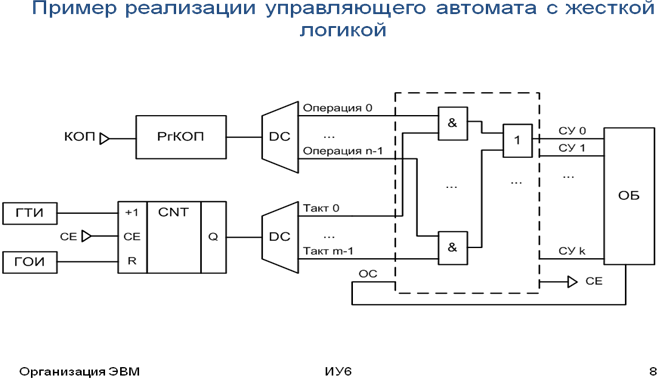

Данная реализация соответствует приведенному ощему описанию:

Верхний DC – дешифратор кода операций;

Нижний DC, CNT, ГТИ (генератор тактовых импульсов), ГОИ (генератор опорных импульсов) – датчик сигналов;

Выделенная пунктиром логика представляет собою блок управления операциями, который вырабатывает управляющие сигналы, которые поступают в операционный блок (ОБ).

Устройство управления с программируемой логикой

Принцип микропрограммного управления.

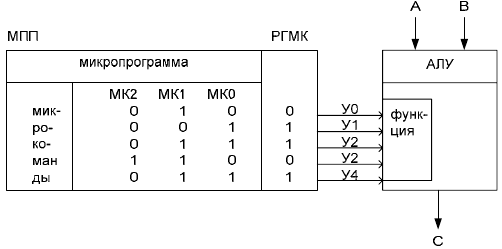

Управляющий автомат с хранимой в памяти логикой; строится на основе принципа программного управления, использующего операционную и адресную структуру управляющего слова; Алгоритм управления представляется упорядоченной совокупностью управляющих слов. Управляющее слово определяет порядок функционирования устройства и называется микрокомандой (МК).

В 1951 году этот принцип предложил Уилксон.

Свойства:

• простота принципа управления

• возможность изменения алгоритма управления путём изменения содержимого

управляющей памяти

• регулярность структуры УУ, удобство реализации на кристалле

• возможность параллельного изготовления аппаратной и программной части УУ

• возможность использования языков микропрограммирования

• универсальность способов построения УУ

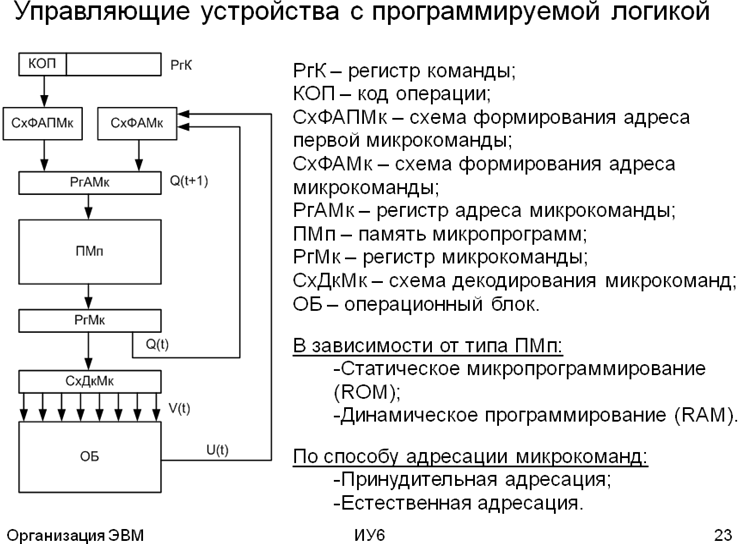

СхФАПМк микрокоманды преобразует код операции команды, присутствующей в данный момент в регистре команд, в начальный адрес микропрограммы, реализующей данную операцию. СхФАМк определяет адрес следующей микрокоманды выполняемой микропрограммы по значению адресной части текущей микрокоманды (Q(t)) и управляющего сигнала из ОБ.

Также (не указано на рисунке) производится запись новой команды в РгК, в случае выполнения последней микропрограммы.

Если управляющая память выполнена как постоянная, то имеет место статическое

микропрограммное управление, а если как ОЗУ – динамическое (мягкое)

у правление.

правление.

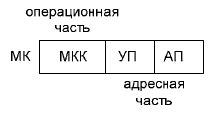

МК состоит из:

МКК – код микрокоманды

УП – условие перехода

АП – адрес перехода

В ЭВМ используется два способа адресации:

• принудительная - адрес перехода указывается в самой МК

• естественная - адрес следующей команды не указывается (он равен IP++)

------------------------------------------------------------------------------------------------------------

Язык VHDL:

Язык VHDL используется для:

- описания поведения цифровых устройств во времени и при изменении входных воздействий;

- описания структуры цифровых устройств с различной степенью детализации (на системном и блочном уровнях, на уровне регистровых передач, на уровне вентилей);

- моделирования цифровых устройств;

- описания тестовых воздействий при моделировании устройств;

- автоматизации преобразования исходного описания схемы в описание на более низком уровне (вплоть до вентильного уровня).

Стили описания:

- поведенческий стиль, при котором для описания проекта используются причинно-следственные связи между событиями на входах устройства и событиями на его выходах (без уточнения структуры);

- структурный стиль описания, при котором устройство представляется в виде иерархии взаимосвязанных простых устройств (подобно стилю, принятому в схемотехнике);

- потоковый стиль описания устройства основан на использовании логических уравнений, каждое из которых преобразует один или несколько входных информационных потоков в выходные потоки.

Полное VHDL-описание объекта состоит как минимум из двух отдельных описаний: описание интерфейса объекта (внешнее описание) и описание тела объекта (описание архитектуры, внутренне описание - функционирование).

Интерфейс описывается в объявлении объекта entity declaration и определяет входы и выходы объекта, его входные и выходные порты ports и параметры настройки generic. Параметры настройки отражают тот факт, что некоторые объекты могут иметь управляющие входы, с помощью которых может производиться настройка экземпляров объектов в частности, задаться временем задержки.

Тело объекта специфицирует его структуру или поведение. Его описание по терминологии VHDL содержится в описании его архитектуры architecture.

VHDL позволяет отождествлять с одним и тем же интерфейсом несколько архитектур. Это связано с тем, что в процессе проектирования происходит проработка архитектуры объекта: переход от структурной схемы к электрической принципиальной, от поведенческого к структурному описанию.

Структура программы на VHDL:

<объект проекта>::=

[<описание library>]

[<описание use>]

<объявление объекта>

<тело архитектуры>

[<объявление конфигурации>]

[<описание library>]::= library <идентификатор> {, <идентификатор>};

[<описание use>]::= use <селективное имя> {, <селективное имя> };

<селективное имя>::= <имя1>. <имя2>

<имя>::= <идентификатор> | <символьный литерал> |all

Примеры :

use IEEE.std_logic_arith."-", IEEE.std_logic_arith."+" ;

use IEEE.std_logic_arith.all;

<объявление объекта>::=

entity <идентификатор> is

[generic(<объявление настроечной константы> {; <объявление настроечной константы>});]

[port (<объявление порта> {;<объявление порта>});]

{<объявление в объекте>}

[begin

{<оператор assert> | <пассивный вызов процедуры> | <пассивный процесс> }]

end [entity][<идентификатор>];

<объявление портов объекта>::=

port (<объявление порта> {; <объявление порта>});

<объявление порта>::= <идентификатор>: in|out|inout|buffer|link <тип>

[:=<начальное значение>].

<объявление настроечных констант>::=

generic(<объявление настроечной константы>

{; <объявление настроечной константы>});

<объявление настроечной константы> ::= <идентификатор>:<тип>[:=<начальное значение>]

<тело архитектуры>::=

architecture <идентификатор> of <имя объекта> is

{<объявление в блоке>}

begin

{ <параллельный оператор>}

end [architecture][<идентификатор>];

<Тип>::= TYPE <Идентификатор> IS <Описание типа>;

<Процесс>::=

[<Метка>:][POSTPONED] PROCESS (<Список чувствительности>) [IS]

<Декларативная часть>

BEGIN

<Последовательные операторы>

END [POSTPONED] PROCESS [<Метка>] ;

Пример:

Синтаксис операторов:

Entity entity_name IS

PORT ( port_interface_List)

END ENTITY;

ARHITECTURE atrch_name OF

entity name IS

BEGIN {concurrent. statement}

END ARCHITECTURE arch_name;