- •Классификация устройств управления. Устройства управления с жесткой и программируемой логикой.

- •Схемное устройство управления

- •Описание автоматов Мура и Мили на языке vhdl

- •Описание динамического триггера и дешифратора на языке vhdl

- •Описание шифратора и драйвера шины на языке vhdl.

- •Описание озу на языке vhdl

- •Программируемые логические матрицы. Программируемая матричная логика. Базовые матричные кристаллы.

- •Архитектура сложных программируемых логических устройств (cpld). Структура макроячейки (на примере xc9500)

- •Программируемые вентильные матрицы (fpga). Структура блока типа slicel в fpga Spartan3

- •Структура клб на примере Spartan-3

- •Структура блока типа slicel

- •Процесс проектирования цифровых устройств с использованием плис

- •Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по данным.

- •Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по управлению.

- •Архитектура конвейерного суперскалярного процессора: статическое и динамическое предсказание переходов.

Программируемые логические матрицы. Программируемая матричная логика. Базовые матричные кристаллы.

Первые представители БИС с программируемой и репрограммируемой структурой: программируемые логические матрицы ПЛМ (PLA), программируемая матричная логика ПМЛ (PAL) и базовые матричные кристаллы БМК (GA). PLA и PAL объединяются под термином PLD. Простые – SPLD, сложные – CPLD.

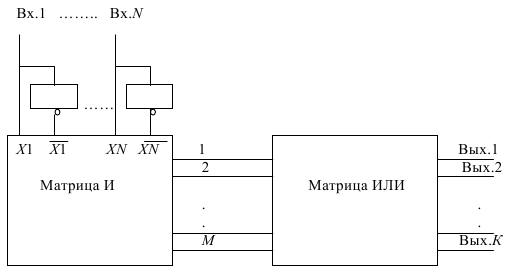

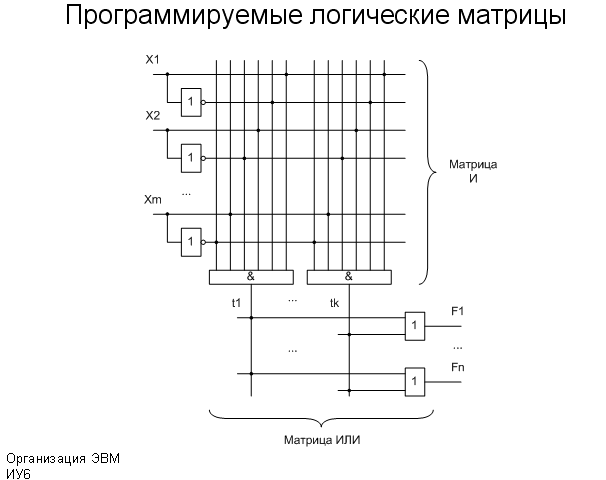

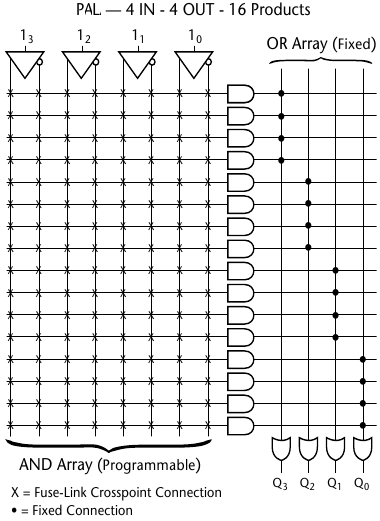

PLD - Programmable Logic Devices, программируемые логические приборы, или ПЛМ - программируемые логические матрицы) состоят из двух логических матриц: матрицы элементов И, на которую подаются прямые и инверсные значения входных сигналов, и матрицы ИЛИ, на которую подаются сформированные в матрице И логические произведения входных сигналов. Таким образом, PLD реализует логическую сумму произведений.

Эти устройства, в свою очередь, делятся на PROM, PLA и PAL в зависимости от того, структура какой из логических матриц является фиксированной, а какой - программируемой.

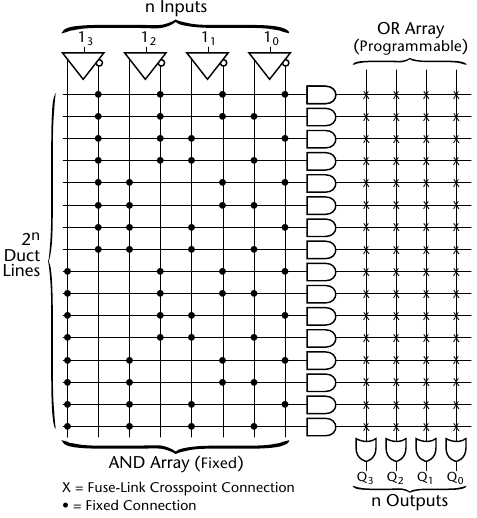

В устройствах PROM (Programmable Read Only Memory) логическая матрица И является фиксированной, а матрица ИЛИ - программируемой.

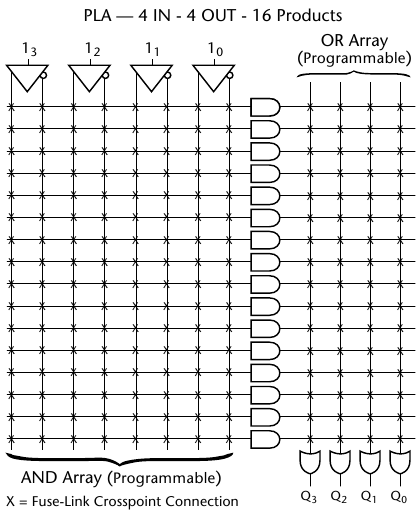

В устройствах PLA (ПЛМ) (Programmable Logic Array) обе логические матрицы являются программируемыми, что делает их наиболее гибкими. Расплатой за это являются снижение быстродействия и повышение цены.

В PLA каждый входной сигнал и его инверсное значение поступают на И-матрицу по горизонтальным линиям. Вертикальные линии матрицы И, которые являются входами элементов И, принимают только тот сигнал, где есть пересечение горизонтальных и вертикальных линий. ПЛМ позволяют реализовать n логических функций от m аргументов. Изготовленная на заводе ПЛМ содержит матрицы со всеми возможными связями (на рис. показаны точками): матрица И позволяет получить k конъюнкций входных сигналов, а матрица ИЛИ — n дизъюнкций термов. В этом случае программирование заключается в разрушении излишних связей. В другом варианте в исходной ПЛМ все связи отсутствуют, а программирование заключается в их создании. Гибкость, предоставляемая структурой PLA, когда обе матрицы являются программируемыми, не всегда используется. Поэтому часто используют более простую структуру PAL.

В устройствах PAL (ПМЛ) (Programmable Array Logic) программируемой является логическая матрица И, а матрица ИЛИ является фиксированной. Эти устройства сочетают гибкость, свойственную PLА, с быстродействием, свойственным PROM.

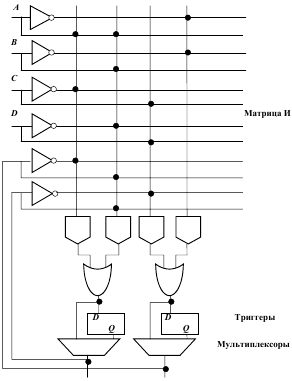

PAL-приборы очень удобны для проектирования комбинационной логики. Но они не могут быть использованы для проектирования последовательностных схем без применения внешних триггеров. Поэтому в приборах PLD (простые PLD – simple PLD) добавлены триггеры, как показано на рис. С помощью мультиплексоров, добавляемых на каждый выход, осуществляется выбор выхода (комбинационный или последовательностный).

С момента своего создания функциональные возможности ПЛМ и ПМЛ были расширены благодаря следующим усовершенствованиям:

• введению двунаправленных, обратных и межэлементных связей, что позволяет наращивать число термов функций;

• введению элементов памяти, что позволяет проектировать на основе ПЛМ и ПМЛ синхронные цифровые автоматы;

• программированию выходных буферов для выдачи выходных сигналов в прямом или инверсном виде;

• использованию мультиплексоров для выбора альтернативных путей прохождения сигналов, репрограммируемых точек связи и памяти конфигурации, позволяющих разработчикам неоднократно программировать функциональность и связность частей ПЛМ и ПМЛ.

Результатом эволюции ИС указанных типов стали сложные программируемые логические устройства (СПЛУ, Complex Programmable Logic Devices, CPLD).

БМК.

Подобно ПЛМ и ПМЛ, БМК позволяют с малыми экономическими затратами реализовать нестандартную схемную логику. Созданная по этой технологии ИС называется матричной большой интегральной схемой (МаБИС).

Использование БМК основано на том факте, что любое сложное устройство состоит из стандартных функциональных частей, таких как логические или схемотехнические элементы, буферы, усилители и т. д. Для обеспечения требуемой функциональности предусматривается включение в структуру БМК избыточного числа таких частей без их коммутации. Окончательная же функциональность определяется на заключительных этапах производства МаБИС с помощью создания нескольких слоев коммутации, наносимых на стандартную заготовку.

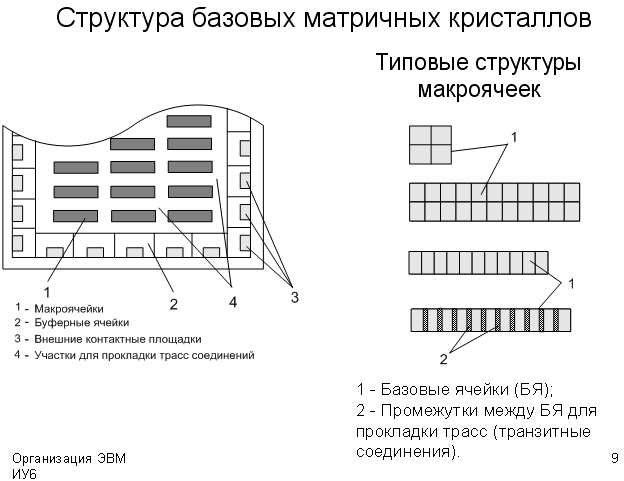

Заготовка БМК состоит из макроячеек, содержащих регулярно повторяющиеся базовые ячейки. Состав и взаимное расположение базовых ячеек определяются возможностью максимально эффективной реализации стандартных компонентов (функциональных ячеек). Между макроячейками имеются свободные участки, необходимые для прокладки трасс межсоединений. На периферии БМК размещаются буферные ячейки, содержащие усилители, шинные формирователи и т. д. В непосредственной близости от буферных ячеек располагаются контактные площадки для электрического соединения внутренних цепей с выводами микросхемы.

При совершенствовании функциональных возможностей БМК были использованы следующие принципы:

• наращивание числа базовых ячеек в макроячейках и числа

макроячеек на БМК;

• усложнение блоков ввода/вывода (добавление буферов, шин-

ных формирователей, введение двунаправленных выводов и выво-

дов с третьим состоянием);

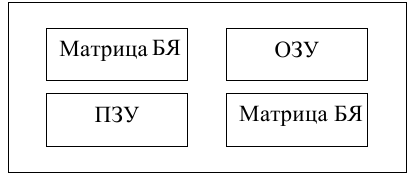

• введение в структуру БМК законченных функциональных

блоков (ОЗУ, ПЗУ и т. д.);

• применение программируемых точек связи совместно с реали-

зацией матриц коммутации и памяти конфигурации, что позволяет

перепрограммировать функциональность и связность частей БМК.

Совершенствование технологии изготовления БМК привело к появлению программируемых пользователем вентильных матриц (ППВМ, Field Programmable Gate Arrays, FPGA).

Технология на основе метода базовых матричных кристаллов (БМК, БИС на БМК, МаБИС, gate arrays) имеет следующие отличительные особенности:

- проектирование основано на использовании заранее подготовленных кристаллов (по заказной технологии) с уже имеющимися элементами чаще всего в виде матрицы одинаковых элементов, а также ряда элементов коммутации и ввода/вывода и т.п.;

- все схемы и элементы БМК прошли полную аттестацию (по электрическим и топологическим параметрам), нет только соединений между элементами, необходимы одна-две операции по выполнению соединений с помощью одного-двух слоев металлизации;

- проектирование схем на БМК можно выполнить или в фирме-разработчике БМК по запросу заказчика, или непосредственно пользователем под конкретную схему;

- БМК поставляются с библиотекой параметров элементов матриц и коммутаций;

- БМК могут быть на основе вентильных матриц для цифровых ИМС или на основе аналоговых матриц кристаллов и функциональных элементов для аналоговых ИМС;

- достоинствами технологии являются низкие стоимость проектирования и изготовления изделий на БМК, малые сроки проектирования и изготовления (1 - 2 месяца);

- недостатки: несколько большая площадь кристалла (по сравнению с заказными и на основе стандартных ячеек), неполное использование кристалла (лишние элементы, избыточность БМК), несколько худшие технические характеристики (по сравнению с заказными).

Развитие полузаказных БИС привело к появлению разновидностей БМК:

канальные,

бесканальные

и блочные архитектуры.

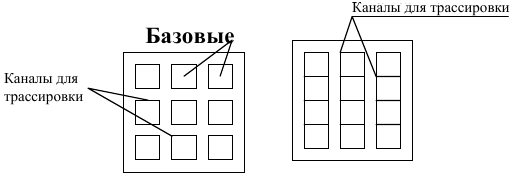

Канальные БМК

Это БМК первого поколения. Представляют совокупность регулярно расположенных на кристалле базовых ячеек, между которыми имеются свободные для создания соединений каналы.

Здесь каналы и вертикальные и горизонтальные. Могут быть отдельно вертикальные каналы.

Такие БМК имеют низкую плотность упаковки, т.к. площадь тратится на межсоединения. Канальная структура характерна для биполярных БМК из-за значительной мощности рассеивания.

Бесканальные БМК.

Эти БМК повышают уровень интеграции. Не имеют фиксированных каналов. Любая область может быть использована как для создания логической схемы, так и для создания межсоединений. Характерны для КМОП-схемотехники.

Бесканальные БМК реализуются в вариантах “море вентилей”, и ”море транзисторов”. Первый содержит массив законченных логических элементов, второй – массив транзисторов.

Так как в бесканальных БМК, называемых иногда универсальными, положеположение трассировочных каналов и ячеек на рабочем поле не является жестким и при проектировании конкретной МАБИС площадь кристалла может перерасперераспределяться между трассировочными каналами и функциональными ячейками, потери площади кристалла снижаются.

Блочные БМК.

Рост уровня интеграции ведет к возвозможностям реализации на одном кристалле все более сложных устройств и систем. Это вызвало к жизни блочные структуры БМК, архитектура которых упрощает построение комбинированных устройств, содержащих как блоки логической обработки данных, так и память или другие специализирован-специализированные блоки. При этом в БМК реализуются несколько блоков-подматриц, каждый из которых имеет как бы структуру БМК меньшей размерности. Между блоками располагаются трассировочные каналы. На перифепериферии блоков изготовляются внутренние буферные каскады для формирования достаточно мощных сигналов, обеспечивающих передачу сигналов.

Тип обрабатываемых сигналов (цифровые, аналоговые) влияет на качество и состав схемных элементов базовых ячеек. В связи с этим БМК подразделяются на цифровые, аналоговые и цифроаналоговые. Аналоговые и цифроаналоговые БМК, появившиеся позднее цифровых и менее распространенные, имеют состав базовых ячеек, позволяющий получать на их основе такие схемы, как операционные усилители, аналоговые ключи и компараторы и т. д.