- •Логічні ел-ти ттл/ттлш: базовий логічний елт. Аналіз амплітудно-передаточної (амплітудної або статичної) хар-ки. Статичні та динамічні параметри.

- •1.2 Логічни ел-ти з трьома станами виходу. Принцип дії. Впорядкування роботи декількох ел-тів на одну спільну лінію інтерфейсу (магістральні інтерфейси)

- •1.3 Логічн ел-ти моп/кмоп: базовий лог ел-т. Аналіз амплітудно-передаточної (амплітудної або статичної) хар-ки. Статичні та динамічні параметри.

- •1.4 Тригери: класифікація та коротка характеристика різних типів тригерів. Особливості схемотехнічної реалізації та функціонування.

- •1.5 Регістри: призначення та класифікація. Паралельні та послідовні регістри. Особливості схемотехнічної реалізації та функціонування.

- •1.6 Лічильники: призначення та класифікація. Асинхронні лічильники. Особливості схемотехнічної реалізації та функціонування.

- •1.7. Синхронні лічильники: особливості схемотехнічної реалізації та функціонування.

- •1.8. Дешифратори: визначення, класифікація, способи побудови та функціонування. Линейный или одноступенчатый дешифратор.

- •1.9 Шифратори. Визначення, принципи побудови та особливості функціонування. Клавіатурні, пріоритетні шифратори, кодоперетворювачі.

- •1.10. Мультиплексори: визначення, принципи побудови та функціонування.

- •1.11. Демультиплексори: визначення, принципи побудови та функціонування.

- •1.12. Суматори комбінаційного типу: призначення, класифікація та принципи побудови.

- •1.13. Накопичуючі суматори та особливості їхнього функціонування.

- •1.14 Моделювання аналогових та цифрових схем за допомогою пакетів ewb і micro-cap: послідовність дій при моделюванні. Одержання та оформлення результатів.

- •Мультиметр

- •Генератор слов

- •Логический анализатор

- •Логический преобразователь

- •Осциллограф.

- •Разработка схем цифровых устройств

- •5.1. Вывод элементов схем на рабочую поверхность

- •Монтаж схем

- •1.15 Особливості та принципи побудови пристроїв з використанням «жорсткої» та «програмованої» логіки.

- •1.16 Основні функції алгебри логіки та логічні елементи для їх реалізації. Закони алгебри логіки.

- •1.17 Синтез логічних схем в базисах (і, або, ні), і-ні, або-ні.

- •1. Абстрактный синтез

- •2. Схемный синтез

- •1.18 Типи даних та структури команд в мп intel (на прикладi 486)

- •1.19. Архітектура системного інтерфейсу сучасних пк. Призначення компонент. Режими передачі інформації по системним шинам.

- •1.20. Розподілення системних ресурсів між компонентами пк. Технологія PnP та її реалізація в шинах pci та isa/eisa.

- •1.21. Засоби кешування мп. Призначення та характеристики. Типи кеш-пам'яті. Режими роботи при читанні/записуванні інформації.

- •1.22. Призначення та організація системної пам'яті. Фізична організація мікросхем пзп, статичного та динамічного озп. Типи динамічної пам’яті (fpm, edo, bedo, sdram).

- •1.23. Архітектура та принцип роботи годинника реального часу rtc та cmos пам'яті. Можливості програмування.

- •1.24. Архітектура системного таймера та призначення каналів таймера. Режими роботи каналів таймера. Можливості програмування.

- •1.25. Архітектура та організація підсистеми dma (кпдп) в пк. Керуюча інформація та програмування.

- •1.26. Організація переривань в пк, пріоритети при обробці переривань. Режими роботи та програмування.

- •1.27. Архітектура та принцип роботи підсистеми клавіатури. Призначення компонент. Та можливості програмування.

- •1.28. Архітектура відеосистеми пк. Управління відеосистемою. Режими. Структура відеопам'яті.

- •1.29. Логічна організація дискових накопичувачів зовнішньої пам'яті. Основні області (boot, fat, root, data area).

- •1.30. Архітектура та управління контролером нжмд. Структура команд.

- •1.31. Архітектура та управління com-портом. Призначення регістрів.

- •1.32. Архітектура та управління lpt – портом в режимах ecp epp.

- •1.33. Архітектура scsi шини.

- •1.34. Архітектура usb шини.

- •2.1 Методи відокремлення каналів у багатоканальних системах передачі даних.

- •2.2 Перетворення, кодування, модуляція. Призначення цих процесів при передаванні даних. Теорема котєльнікова (найквіста).

- •2.3 Модуляція. Різновиди модуляції. Швидкість маніпуляції.

- •2.4 Кількість інформації. Ентропія. Надмірність.

- •2.5 Класифікація завад. Властивості флуктуаційних завад.

- •2.6 Амплітудна маніпуляція. Модулятор та детектор. Спектр сигналу та потрібна смуга перепускання каналу.

- •2.7 Частотна маніпуляція. Модулятор, детектор.

- •Фазова маніпуляція. Спектр сигналу та потрібна смуга перепускання каналу. Відносна фазова маніпуляція та детектування.

- •2.9. Різновиди фазової маніпуляції: двфм, твфм, кам.

- •2.11. Класифікація похибкостійких кодів. Вирази для розрахунку віроємності невиявленої помилки для кодів із сталою вагою та для кодів з контролем за паритетом

- •2.12. Первичные коды и способы расширения кодировочной таблицы. Esc-последовательности принтеров.

- •2.13. Причины использования модуляции при передаче данных. Разновидности модуляции и необходимые полосы пропускания линий связи.

- •2.14. Геометрическая интерпретация сигналов и помех. Идеальный приёмник котельникова и другие варианты построения приёмников двоичных сигналов.

- •2.15. Синхронизация в аппаратуре передачи данных и в устройствах считывания магнитных записей, способы кодирования, которые повышают надёжность синхронизации битов.

- •Параллельный метод

- •Последовательный метод

- •2.16. Модемы как периферийные устройства. Система команд хейза. Модемы серии mnp. Особенности модемов классов mnp-5,7,10. Команды модема.

- •2.17. Методы магнитного записывания информации и их применение.

- •2.18. Частотный и модифицированный частотный методы записи информации. Формат сектора на гибком диске. Способы позиционирования головок в дисковых устройствах магнитного записывания информации.

- •2.19. Елементи формату сектору, що забезпечують бітову та байтову синхронізацію під час зчитування інформації з гнучких дисків.

- •2.22. Cтандарт багаторівневого керування мережею (модель взаімодії відкритих систем – open system interconnection, osi). Поняття протоколу, інтерфейсу, стеку протоколів.

- •2.24. Протоколи канального рівня: асинхронні, синхронні (символьно-орієнтовані, біт-орієнтовані). Протоколи з встановленням з’єднання та без встановлення.

- •Синхронные символьно-ориентированные и бит-ориентированные протоколы

- •Передача с установлением соединения и без установления соединения

- •2.25 Локальна мережа ethernet. Топології, стандарти, доступ до мережі, структура кадру, розрахунок продуктивності, колізії, домен колізій та організація роботи мережі.

- •Максимальная производительность сети Ethernet

- •Форматы кадров технологии Ethernet

- •Глобальные связи на основе сетей с коммутацией каналов

- •Isdn - сети с интегральными услугами

- •2.28.Протокол ip та його функції. Структура ip-пакету та його параметри. Маршрутизація в ip-мережах. Фрагментація ip–пакетів. Зборка фрагментів.

- •Источники и типы записей в таблице маршрутизации:

- •Фрагментация ip-пакетов

- •2.29. Тенденції розвитку мікропроцесорної техніки. Структура та режими функціонування сучасних мікропроцесорів.

- •2.30. На базі існуючих технічних рішень провести розробку структурної схеми мікропроцесора.

- •2.31. Сегментація пам’яті в захищеному режимі. Розробка дескрипторів сегментів. Формування лінійної адреси при звертанні до пам’яті.

- •2.32. Обробка переривань в захищеному режимі. Види виключень. Формування дескриптивної таблиці переривань.

- •5.9. Приклад обробки пеpеpивань в захищеному режимi

- •5.9.1. Опис програми p_int

- •2. 34 Захист пам’яті. Рівні привілеїв. Особливості захисту сегментів даних, стеку, коду та пристроїв введення/виведення.

- •2.35. Апаратні засоби підтримки багатозадачної роботи мікропроцесора. Структура аблиці стану задач. Алгоритми та механізми переключення задач.

- •2.36.Алгоритми та механізми переключення задач

- •2.37. Сторінкова організація пам’яті. Розробка покажчиків таблиць та сторінок формування фізичної адреси для 4к-, 2м- і 4м-байтних сторінок.

- •3.1. Засоби захисту носіїв інформації. Записування за межами поля форматування. Зміна довжини сектора. Чергування секторів.

- •3.5. Процеси. Контекст процесу. Стани процесів та переходи між ними. Системні виклики для забезпечення життєвого циклу процесу.

- •3.6. Керування пам’яттю. Основні задачі. Моделі пам’яті. Системні виклики для роботи з пам’яттю.

- •3.7. Операційні системи. Склад ос. Вимоги до сучасних ос. Архітектурні напрямки побудови ос.

- •Монолитные системы

- •Многоуровневые системы

- •Модель клиент-сервер и микроядра

- •3.8. Монопольні ресурси. Проблема тупиків. Дисципліни розподілу ресурсів. Пошук тупиків та їх знищення.

- •3.9. Паралельне виконання процесів. Формулювання задачі «виробники-споживачі» та методи її вирішення.

- •3.10. Засоби взаємодії процесів. Порівняльна характеристика базових механізмів ipc.

- •3. 12 Субд. Основні функції. Види субд.

- •3.13 Реляційні бази даних. Основні поняття, властивості відношень, модель даних, реляційні операції і обчислення. Базовые понятия реляционных баз данных.

- •1. Тип данных

- •2. Домен

- •3. Схема отношения, схема базы данных

- •4. Кортеж, отношение

- •1.Отсутствие кортежей-дубликатов

- •2. Отсутствие упорядоченности кортежей

- •3. Отсутствие упорядоченности атрибутов

- •3.14.Колірні простори rgb та cmyk. Сфера застосування та та причини їх розходження. Одержання кольорів одного простору через значення кольорів іншого.

- •3.16 Провести порівняння технологій взаємодії процесів у локальній мережі. Поштові скриньки. Іменовані канали. Вилучений виклик процедур. Гнізда.

- •3.17 Провести порівняння методів побудови багаторівневих програмних засобів. Динамічні бібліотеки. Com і activex. Провайдери. Служби. Драйвера.

- •3.18 Загальні вимоги і архітектури інтерфейсу користувача . Можливості, переваги і недоліки діалогових, однодокументних і багатодокументних прикладень.

- •3.19 Типи даних та структури команд в мп Intel.

- •3.20 Організація переривань в пк, пріоритети при обробці переривань. Режими роботи та програмування.

- •3.21 Архітектура відеосистеми пк. Управління відеосистемою.

- •3.22 Режими відеосистеми. Структура відеопам'яті.

- •3.23 Логічна організація дискових накопичувачів зовнішньої пам'яті. Основні області (boot, fat, root, data area).

- •3.24 Двійкова логіка. Булеві функції однієї та двох змінних. Кількість булевих функцій n-змінних. Суперпозиція булевих функцій.

- •3.25. Тестова діагностика мереж пк. Утиліта ping: організація роботи, типи повідомлень. Поясніть можливий приклад роботи утиліти.

- •Технические характеристики системной платы

- •3.27. Відеосистема пк. Основні експлуатаційні характеристики. Отримання інформації про відеосистему пк та результатів тестування з допомогою програми класу checkit. Пояснити можливі результати.

- •Возможные тесты видеосистемы:

- •3.28. Реалізація анімації зображення в web-сторінках з використанням додаткових графічних файлів і без них (тільки текстом html-файлу).

- •3.29. Колір – як засіб керування психікою і поведінкою людини. Реалізація колірної гармонії у графічному зображенні.

- •Понятие цветовой гармонии :

- •3.30. Спектральна характеристика людського ока і причина використання rgb системи в моніторах. Технічні і психофізіологічні обмеження відтворення кольору.

- •3.31 Реляційні бази даних. Транзакції та цілісність баз даних. Ізольованість користувачів. Журнал змін. Транзакции и целостность баз данных

- •3.32 Мова запитів sql. Команда select і структура запитів на вибірку.

- •3.33 Мова запитів sql. Робота з записами і таблицями. Додавання, видалення, модифікація.

- •3.34. Архітектури побудови систем клієнт-сервер. Варіанти побудови серверних прикладень. Варіанти побудови клієнтських прикладень.

- •3.35. Драйвери. Призначення, структура. Механізм роботи драйвера. Приклади драйверів.

- •3.36. Керування процесорним часом. Модель планувальника та диспетчера процесорного часу. Пріоритети процесів.

- •3.37. Керування процесорним часом. Витісняючі та невитісняючі дисципліни планування процесорного часу.

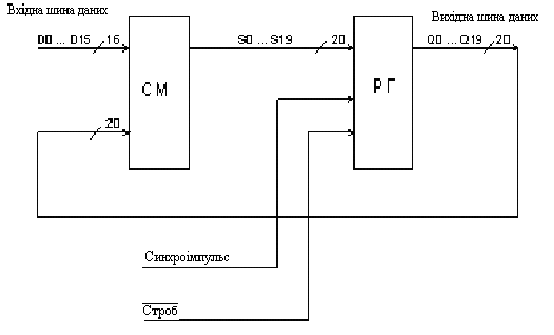

1.13. Накопичуючі суматори та особливості їхнього функціонування.

Накапливающий сумматор (НС) обычно представляет собой совокупность сумматора комбинационного типа и регистра (который хранит результаты суммирования как текущие, так и окончательные). Работает такой сумматор по формуле Si = Si-1 + A, ( формула 1.1) где

Si –текущая сумма,

Si-1 –предыдущая(на предыдущем цикле суммирования),

А – очередное текущее слагаемое.

Результат замещает старое значение суммы. Очередное прибавление слагаемого тактируется синхроимпульсами. Учитывая такие особенности функцио-нирования накапливающие сумматоры называются иногда аккумуляторами. На схемах сумматоры обозначаются SM. В российских сериях интегральных микросхем(ИМС), соответственно – ИР(например-К155ИМ3). В американских

сериях они отдельно не обозначаются: SN40S08N. Интегральные микросхемы содержат,как правило, четырехразрядные комбинационные сумматоры. Чаще всего применяют четырехразрядные сумматоры комбинационного типа. Помимо выходных разрядов суммы и выхода переноса в сумматорах предусмотрен вход расширения С для обьединения сумматоров с целью повышения разрядности.

Многоразрядные сумматоры можно построить, прибегнув к обьединению синхронизирующих входов, а также соединению соответствующих входов и выходов переноса нескольких базовых сумматоров.

Эти сумматоры являются ядром арифметико-логических устройств(АЛУ) , без которых, в свою очередь, не было бы процессоров. По сути, эти устройства является интегральными микросхемами, без которых не обходится ни один компьютер в целом, ни сколько-нибудь сложное цифровое устройство, где необходимо выполнять арифметичесие операции.

Накапливающие сумматоры применяются также, например, для формирования адреса ОЗУ, в генераторах сигналов произвольной формы.

На основании формулы 1.1, описывающе по сути алгоритм работы НС можно предложить структурную схему, приведенную на рис 1.1. Схема работает следующим образом: Перед началом суммирования регистр устанавливается в нулевое состояние по входу R. После поступления слов в сумматор происходит обработка результата, то есть проверяется перенос и происходит собственно суммирование. С выходов сумматора результат суммы поступает на регистр (РГ), который служит для хранения информации и задержки сигнала на один такт. Естественно, сигналы через него будут проходить в том случае, если открыт вход синхронизации. Затем с выходов регистра сигналы поступают в качестве второго слагаемого(20-ти разрядного) на сумматор. Такой цикл повторяется до тех пор, пока не прекратится подача последовательности кодов либо сумма не превысит разрядность 20 (в этом случае сумматор сбрасывается в 0.

1.14 Моделювання аналогових та цифрових схем за допомогою пакетів ewb і micro-cap: послідовність дій при моделюванні. Одержання та оформлення результатів.

Программно-прикладной пакет (ППП) EWB предназн для разработки схем цифров устр-в на цифровых эл-тах и анализа их работы в динамике и статике с возможностью

моделирования различных режимов работы. Пакет позволяет получать

несколько вар-тов реализации схемных решений при разработке одного и того же цифров устр-ва, что позволяет выбрать оптимальный алгоритм работы.

В программно-прикладном пакете «Electronics

WorkBench 3.0E» пользователю предоставлена возможность использовать в своей работе 7 приборов (Мультиметр, Генератор Слов, Логич Анализатор, Логич преобразователь).