- •1.Процессор

- •1.1. Арифметико-логическое устройство

- •1.2. Устройство управления

- •1.3. Основные принципы работы современных процессоров

- •1.4. Регистры процессора

- •1.4.1. Регистры общего назначения

- •1.4.2.Указатель команд

- •1.4.3. Сегментные регистры

- •1.4.4. Регистр состояния микропроцессора Intel 8086

- •1.4.5. Управляющие регистры

- •1.4.6. Прочие регистры

- •1.5. Представление команд в эвм

- •1.6. Основные стадии выполнения команд

- •2. СисТемная шина

- •2.1. Шины

- •2.2. Шина данных. Разрядность шины

- •2.3. Адресная шина. Разрядность шины

- •2.4. Шина управления

- •2.5. Цикл шины

- •2.6. Системные и локальные шины

- •2.7. Стандарты шин

- •3. Многоуровневая организация памяти

- •3.1. Регистровая память

- •3.2. Буферная память

- •3.2.1. Кэширование памяти

- •3.2.2. Принципы кэширования

- •3.2.3. Кэш прямого отображения

- •3.2.4. Наборно-ассоциативный кэш

- •3.2.5. Ассоциативный кэш

- •3.3. Оперативная память

- •3.3.1. Логическое распределение оперативной памяти

- •3.3.2. Стандартная оперативная память

- •3.4.Страничная и сегментная организация памяти. Виртуальная память

- •3.4.1. Режимы процессора

- •3.4.2. Организация памяти

- •3.4.3. Концепция виртуальной памяти

- •3.4.4. Страничная организация памяти

- •3.4.5. Сегментация памяти

- •3.4.6. Механизм замены (своппирования) страниц

- •3.5. Защита информации и памяти

- •3.6. Внешняя память

- •3.6.1. Классификация накопителей

- •3.6.2. Логическая структура дисков

- •3.6.3. Флоппи-диски

- •3.6.4. Сменные диски

- •3.6.5. Стриммер

- •3.6.6. Магнитооптические накопители

- •3.6.7.Накопители на гибких магнитных дисках Бернулли

- •3.6.8. Накопители на гибких магнитных дисках Zip

- •4. Система ввода-вывода

- •4.1.Принципы организации обменов данными

- •4.1.1. Структура с одним общим интерфейсом

- •4.1.2. Структура с каналами ввода-вывода

- •4.1.3. Основные параметры интерфейсов

- •4.1.4. Параллельная и последовательная передача данных

- •4.1.5. Методы передачи информации между устройствами эвм

- •4.2. Индивидуальные каналы

- •4.2.1. Основные типы каналов ввода-вывода

- •4.3. Ввод-вывод с отображением на память

- •4.4. Порты ввода-вывода

- •4.4.1. Параллельный порт

- •4.4.2. Последовательный порт

- •Адреса и прерывания последовательных портов

- •4.4.3. Развитие параллельного и последовательного интерфейсов

- •5. Организация прерываний

- •5.1 Механизм прерываний

- •5.1.1. Назначение системы прерываний

- •5.1.2. Порядок обработки прерывания

- •5.1.3. Характеристики системы прерывания

- •5.1.4. Приоритетное обслуживание запросов прерывания

- •5.1.5. Программное управление приоритетом

- •5.2. Организация системы прерываний микропроцессора х86

- •5.2.1. Аппаратные прерывания. Контроллер прерываний

- •5.2.2. Особенности обработки аппаратных прерываний

- •5.2.3. Внутренние прерывания

- •5.2.4. Таблица векторов прерываний

- •5.2.5. Процедуры прерываний

- •1. Пример выполнения упражнения тренинга на умение № 1

- •2. Пример выполнения упражнения тренинга на умение № 2

- •3.Пример выполнения упражнения тренинга на умение № 3

- •4. Пример выполнения упражнения тренинга на умение № 4

- •5. Пример выполнения упражнения тренинга на умение № 5

- •6. Пример выполнения упражнения тренинга на умение № 6

2.4. Шина управления

Линии шины управления на системной плате служат для управления различными компонентами ПК. По выполняемой ими функции их можно сравнить с переводной стрелкой на железнодорожных путях.

С помощью небольшого числа линий шина управления обеспечивает такое функционирование системы, чтобы в каждый данный момент времени только одна структурная единица ПК пересылала данные по шине данных или осуществляла адресацию памяти.

К шине может быть подключено много приемных устройств. Сочетание управляющих и адресных сигналов определяет, для кого именно предназначаются данные на шине. Управляющая логика возбуждает специальные стробирующие сигналы, чтобы указать получателю, когда ему следует принимать данные.

Управляющая логика активизирует в каждый конкретный момент только одно устройство, которое становиться ведущим. Когда устройство активизировано, оно помещает свои данные на шину. Все другие микросхемы в этот промежуток времени должны блокироваться с помощью соответствующего сигнала на линии управления.

2.5. Цикл шины

Микропроцессор взаимодействует с внешней средой с помощью шины адреса/данных/состояния и нескольких управляющих сигналов. Собственно взаимодействие заключается в выполнении одной из двух операций: МП либо выводит (записывает) данные, либо вводит (считывает) данные или команды. В каждой из этих операций процессор должен указывать то устройство, с которым он будет взаимодействовать; другими словами, процессор должен адресовать ячейку памяти либо порт ввода или вывода.

Для передачи данных или выборки команды процессор инициирует так называемый цикл шины. Кроме процессора, цикл шины могут инициировать и другие устройства, например, арифметический сопроцессор.

Цикл шины представляет собой последовательность событий, в течение которой процессор выдает адрес ячейки памяти или периферийного устройства, а затем формирует сигнал записи или считывания, а также выдает данные в операции записи. Выбранное устройство воспринимает данные с шины в цикле записи или помещает данные на шину в цикле считывания. По окончании цикла шины устройство фиксирует записываемые данные или снимает считываемые данные.

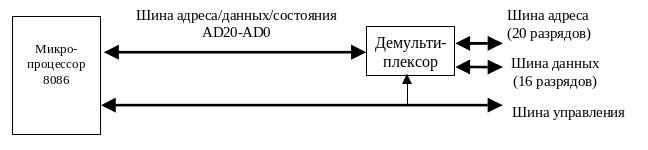

Рассмотрим цикл шины микропроцессора 8086, который имеет совмещенную 20-разрядную шину адреса/данных/состояния и шину управления (рис. 4).

Рис. 4. Шины микропроцессора 8086

Цикл шины микропроцессора 8086 состоит минимум из четырех тактов синхронизации, называемых также состояниями T, которые идентифицируются спадающим фронтом сигнала синхронизации CLC. В первом такте (T1) процессор выдает на шину адреса/данных/состояния AD20-AD0 адрес устройства, которое будет источником или получателем информации в текущем цикле шины. Во втором такте (T2) процессор снимает адрес с шины и либо переводит тристабильные буферы линий AD15-AD0 в высокоимпедансное состояние, подготавливая их к выводу информации в цикле считывания, либо выдает на них данные в цикле записи.

Управляющие сигналы, инициирующие считывание, запись или подтверждение прерываний, всегда выдаются в такте T2. В максимальной конфигурации системы сигнал записи формируется в такте T3, чтобы гарантировать стабилизацию сигналов данных до начала действия этого сигнала.

В такте T2 старшие четыре линии адреса/состояния переключаются с режима выдачи адреса на режим выдачи состояния. Сигналы состояния предназначены в основном для диагностических целей, например, идентифицируют сегментный регистр, который участвует в формировании адреса памяти.

В течение такта T3 процессор сохраняет информацию на линиях состояния. На шине данных в цикле записи сохраняются выводимые данные, а в цикле считывания производится опрос вводимых данных.

Тактом T4 заканчивается цикл шины. В этом такте снимаются все управляющие сигналы и выбранное устройство отключается от шины.

Таким образом, цикл шины для памяти или периферийного устройства представляет собой асинхронное действие. Устройство может управлять циклом шины только путем введения состояний ожидания.

Процессор выполняет цикл шины в том случае, когда ему необходимо осуществить запись или считывание информации. Если циклы шины не требуются, шинный интерфейс реализует холостые состояния Ti, в течение которых процессор сохраняет на линиях состояния сигналы состояния от предыдущего цикла шины.