- •1.Процессор

- •1.1. Арифметико-логическое устройство

- •1.2. Устройство управления

- •1.3. Основные принципы работы современных процессоров

- •1.4. Регистры процессора

- •1.4.1. Регистры общего назначения

- •1.4.2.Указатель команд

- •1.4.3. Сегментные регистры

- •1.4.4. Регистр состояния микропроцессора Intel 8086

- •1.4.5. Управляющие регистры

- •1.4.6. Прочие регистры

- •1.5. Представление команд в эвм

- •1.6. Основные стадии выполнения команд

- •2. СисТемная шина

- •2.1. Шины

- •2.2. Шина данных. Разрядность шины

- •2.3. Адресная шина. Разрядность шины

- •2.4. Шина управления

- •2.5. Цикл шины

- •2.6. Системные и локальные шины

- •2.7. Стандарты шин

- •3. Многоуровневая организация памяти

- •3.1. Регистровая память

- •3.2. Буферная память

- •3.2.1. Кэширование памяти

- •3.2.2. Принципы кэширования

- •3.2.3. Кэш прямого отображения

- •3.2.4. Наборно-ассоциативный кэш

- •3.2.5. Ассоциативный кэш

- •3.3. Оперативная память

- •3.3.1. Логическое распределение оперативной памяти

- •3.3.2. Стандартная оперативная память

- •3.4.Страничная и сегментная организация памяти. Виртуальная память

- •3.4.1. Режимы процессора

- •3.4.2. Организация памяти

- •3.4.3. Концепция виртуальной памяти

- •3.4.4. Страничная организация памяти

- •3.4.5. Сегментация памяти

- •3.4.6. Механизм замены (своппирования) страниц

- •3.5. Защита информации и памяти

- •3.6. Внешняя память

- •3.6.1. Классификация накопителей

- •3.6.2. Логическая структура дисков

- •3.6.3. Флоппи-диски

- •3.6.4. Сменные диски

- •3.6.5. Стриммер

- •3.6.6. Магнитооптические накопители

- •3.6.7.Накопители на гибких магнитных дисках Бернулли

- •3.6.8. Накопители на гибких магнитных дисках Zip

- •4. Система ввода-вывода

- •4.1.Принципы организации обменов данными

- •4.1.1. Структура с одним общим интерфейсом

- •4.1.2. Структура с каналами ввода-вывода

- •4.1.3. Основные параметры интерфейсов

- •4.1.4. Параллельная и последовательная передача данных

- •4.1.5. Методы передачи информации между устройствами эвм

- •4.2. Индивидуальные каналы

- •4.2.1. Основные типы каналов ввода-вывода

- •4.3. Ввод-вывод с отображением на память

- •4.4. Порты ввода-вывода

- •4.4.1. Параллельный порт

- •4.4.2. Последовательный порт

- •Адреса и прерывания последовательных портов

- •4.4.3. Развитие параллельного и последовательного интерфейсов

- •5. Организация прерываний

- •5.1 Механизм прерываний

- •5.1.1. Назначение системы прерываний

- •5.1.2. Порядок обработки прерывания

- •5.1.3. Характеристики системы прерывания

- •5.1.4. Приоритетное обслуживание запросов прерывания

- •5.1.5. Программное управление приоритетом

- •5.2. Организация системы прерываний микропроцессора х86

- •5.2.1. Аппаратные прерывания. Контроллер прерываний

- •5.2.2. Особенности обработки аппаратных прерываний

- •5.2.3. Внутренние прерывания

- •5.2.4. Таблица векторов прерываний

- •5.2.5. Процедуры прерываний

- •1. Пример выполнения упражнения тренинга на умение № 1

- •2. Пример выполнения упражнения тренинга на умение № 2

- •3.Пример выполнения упражнения тренинга на умение № 3

- •4. Пример выполнения упражнения тренинга на умение № 4

- •5. Пример выполнения упражнения тренинга на умение № 5

- •6. Пример выполнения упражнения тренинга на умение № 6

3.2.4. Наборно-ассоциативный кэш

Наборно-ассоциативная архитектура кэша позволяет каждому блоку кэшируемой памяти претендовать на одну из нескольких строк кэша, объединенных в набор (set). Можно считать, что в этой архитектуре есть несколько параллельно и согласованно работающих каналов прямого отображения, где контроллеру кэша приходится принимать решение о том, в какую из строк набора помещать очередной блок данных.

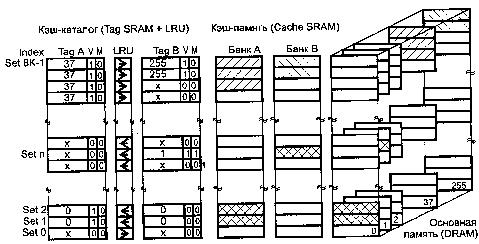

В простейшем случае каждый блок памяти может помещаться в одну из двух строк (Two Way Set-Associative Cache – двухканальный наборно-ассоциативный кэш). Такой кэш должен содержать два банка памяти тегов (рис. 7).

Рис. 7. Двухканальный наборно-ассоциативный кэш

Номер набора (индекс), в котором может отображаться затребованный блок данных, однозначно определяется средней частью адреса (как номер строки в кэше прямого отображения). Строка набора, отображающая требуемый блок, определяется сравнением тегов (как и в ассоциативном кэше), параллельно выполняемым для всех каналов кэша. Кроме того, с каждым набором должен быть связан признак, определяющий строку набора, подлежащую замещению новым блоком данных в случае кэш-промаха. Кандидатом на замещение обычно выбирается строка, к которой дольше всего не обращались (алгоритм LRU– Least Recently Used). При относительно большом количестве каналов (строк в наборе) прибегают к некоторому упрощению – алгоритм Pseudo-LRU для четырех строк (Four Way Set Associative Cache) позволяет принимать решения, используя всего 3 бита. Возможно также применение алгоритма замещения FIFO (первым вошел – первым вышел) или даже случайного (random) замещения, что проще, но менее эффективно.

Наборно-ассоциативная архитектура широко применяется для первичного кэша современных процессоров. Объем кэшируемой памяти определяется так же, как и в предыдущем варианте, но здесь фигурируют объем одного банка (а не всего кэша) и разрядность относящихся к нему ячеек тега.

3.2.5. Ассоциативный кэш

В отличие от предыдущих у полностью ассоциативного кэша любая его строка может отображать любой блок памяти, что существенно повышает эффективность использования его ограниченного объема. При этом все биты адреса кэшированного блока, за вычетом битов, определяющих положение (смещение) данных в строке, хранятся в памяти тегов. В такой архитектуре для определения наличия затребованных данных в кэш-памяти требуется сравнение со старшей частью адреса тегов всех строк, а не одной или нескольких, как при прямом отображении или наборно-ассоциативной архитектуре. Естественно, последовательный перебор ячеек памяти тегов отпадает – на это может уйти слишком много времени. Остается параллельный анализ всех ячеек, что является сложной аппаратной задачей, которая пока решена только для небольших объемов первичного кэша в некоторых процессорах. Применение полностью ассоциативной архитектуры во вторичном кэше пока не предвидится.

3.3. Оперативная память

3.3.1. Логическое распределение оперативной памяти

Логическое распределение оперативной памяти определяется не только применяемой операционной системой, но и особенностями аппаратной реализации IBM-совместимых PC. Знание строения ОЗУ необходимо для программной оптимизации системы.

Можно выделить пять важнейших логических областей оперативной памяти:

Стандартная оперативная память (Conventional Memory);

ЕМS-память (Expanded Memory Specification) – дополнительная память;

UMA (Upper Memory Area) – верхняя память;

HMA (High Memory Area);

XMS (Extended Memory Specification) – расширенная память