- •Лабораторная работа № 1 Изучение общей структуры арифметико-логического устройства эвм

- •Подготовка к работе

- •Программа работы

- •Методические указания к работе

- •Лабораторная работа № 2 Синтез управляющего устройства эвм на основе автоматов Мура и Мили

- •Подготовка к работе

- •Программа работы

- •Методические указания к работе

- •Лабораторная работа № 3 Изучение архитектуры и функциональных возможностей арифметико-логического устройства на базе вычислительной секции к1804вс1

- •Подготовка к работе

- •Программа работы

- •Методические указания к работе

- •Методические указания к работе

- •Литература: [1, c.277–316; 7, c.154–158; 8, c.355-358] Библиографический список

Методические указания к работе

К п.1. Тренажер МТ1804 изготовлен на базе микропроцессорного комплекта ИС К1804 с разрядно-модульной организацией. Основным элементом тренажера является процессорная секция (АЛУ) реализованная на ИС К1804ВС1. Это четырехразрядная секция с возможностью объединения с целью построения процессоров ЭВМ произвольной разрядности.

Структурная схема секции К1804ВС1 приведена на рис. 6. Основным элементом является АЛУ, имеющее 4-разрядные входы R, S и выход F. Кроме того, АЛУ вход переноса в младший разряд C0 и выходы:

C4 – перенос из старшего разряда результата;

V – признак переполнения;

Z – признак нулевого результата;

N – признак отрицательного результата;

P, G – выходы распространения и генерации переноса, для схемы ускорения переноса (аналогичны выходам X и Y сумматоров).

Вся вычислительная секция управляется 9-разрядной микрокомандой I8,..,I0. Разряды микрокоманды (МК) I5 I4 I3 управляют операцией выполняемой АЛУ (см. табл. 136).

рис. 6. Структура ИС К1804ВС1

табл. 136

I5

I4

I3

Операция АЛУ

0

0

0

R+S+C0

0

0

1

S – R – 1+C0

0

1

0

R – S – 1+C0

0

1

1

RVS

1

0

0

R&S

1

0

1

1

1

0

RS

1

1

1

![]() &S

&S

![]()

содержимое регистров A и B;

входные линии секции DI0,…,DI3 ;

нулевой операнд;

содержимое рабочего регистра Q.

Младшие три разряда I2 ,I1, I0 управляют мультиплексором МП1 (см. табл. 147).

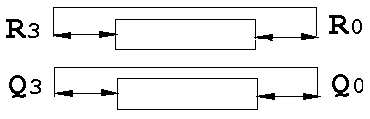

Регистровое запоминающее устройство (РЗУ) содержит 16 четырехразрядных регистров (ячеек памяти) R0 ,..R15 .РЗУ имеет две группы адресных входов A0,…,A3 B0,…,B3 и две группы выходов, подключенных к буферным регистрам A и B. Благодаря такой конструкции из РЗУ можно считывать содержимое сразу двух регистров по адресу A и B.

табл. 147

I2

I1

I0

Источник

операндов АЛУ

R

S

0

0

0

A

Q

0

0

1

A

B

0

1

0

0

Q

0

1

1

0

B

1

0

0

0

A

1

0

1

D

A

1

1

0

D

Q

1

1

1

D

0

Блок рабочего регистра Q включает в себя непосредственно регистр Q и сдвигатель СД2.

Результат операции F , выполненной АЛУ может быть выдан на линии DO0,…,DO3 , через мультиплексор МП0 или записан в РЗУ (со сдвигом или без него), или помещен в регистр Q. Управление приемником результата осуществляется старшими разрядами микрокоманды I8,I7,I6 (см. табл. 158).

табл. 158

I8

I7

I6

Загрузка

Выход Y

0

0

0

F

Q

F

0

0

1

Нет загрузки

F

0

1

0

F

B

A

0

1

1

F

B

F

1

0

0

F/2B

Q/2Q

F

1

0

1

F/2

B

F

1

1

0

2F

B 2Q

Q

F

1

1

1

2F

B

F

Поля микрокоманд, приведенные в табл.20, имеют следующее назначение:

7 – адрес перехода на микрокоманду (в данной лабораторной работе не используется);

6 – управление следующим адресом (в данной лабораторной работе не используется);

MS1, MS2 – биты управления операциями сдвига (назначение MS2 и MS1 приведено в табл. 19);

5 – управление приемником результата (табл. 158);

4 – источник операнда (табл. 147);

3 – входной перенос C0 и операция АЛУ (табл. 136);

2 - адрес регистра по каналу А;

1 – адрес регистра по каналу В;

0 - входные непосредственные данные DI3-DI0.

Запись микрокоманды в микропрограммную память осуществляется потетрадно в меню Просмотр/программа.

табл. 19

MS2 |

MS1 |

Тип сдвига |

Обозначения сдвигов |

0 |

0 |

арифметический сдвиг одинарной длины При сдвиге вправо “0” помещается в старший разряд, влево – в младший разряд. |

|

0 |

1 |

циклический сдвиг одинарной длины |

|

1 |

0 |

циклический сдвиг двойной длины |

|

1 |

1 |

арифметический сдвиг двойной длины При сдвиге вправо в старший разряд вдвигается значение выходного переноса С4. При сдвиге влево в младший разряд вдвигается “0”. |

|

табл. 160

Положение мультиплексора |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

||

№ бита |

31 30 29 28 |

27 26 25 24 |

23 |

22 21 20 |

19 |

18 17 16 |

15 14 13 12 |

11-8 |

7-4 |

3-0 |

Назначение бита |

BR3 BR2 BR1 BR0 |

P3P2P1P0 |

MS2 |

I8 I7 I6 |

MS1 |

I2 I1 I0 |

C0 I5 I4 I3 |

A3-A0 |

B3-B0 |

D3-D0 |

К п.2. Составление микрокоманды арифметической операции рассмотрим на примере.

Пусть необходимо реализовать операцию R9R1-Q-1. Помимо данной операции необходимо предварительно загрузить некоторые значения в регистры R1, Q.

Зададимся R1=7, Q=2.

Составим три микрокоманды:

загрузки R1 значением 7;

загрузки Q значением 2;

вычисления R9=R1-Q-1.

Составленные микрокоманды, в соответствии с форматом табл. 160, приведены в табл. 171.

табл. 171

Адрес |

Номер тетрады микрокоманды |

Выполняемая |

|||||||

памяти |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

операция |

0000 |

- |

- |

0011 |

0111 |

0011 |

- |

0001 |

0111 |

R1=7 |

0001 |

- |

- |

0000 |

0111 |

0000 |

- |

- |

0010 |

Q=2 |

0010 |

- |

- |

0011 |

0000 |

0010 |

0001 |

1001 |

- |

R9=R1-Q-1 |

Загрузка микрокоманд в память тренажера осуществляется в последовательности:

в поле "Адрес" набрать адрес ячейки памяти с микрокомандой;

выполнить микрокоманду нажав клавишу F8 (шаг);

К п.3. Микрокоманды, реализующие одинарный циклический сдвиг влево и двойной циклический сдвиг вправо регистра R9 приведены в табл. 182.

табл. 182

Адрес |

Номер тетрады микрокоманды |

Выполняемая |

|||||||

памяти |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

операция |

0000 |

- |

- |

0111 |

1011 |

0011 |

- |

1001 |

- |

Один. сдв.R9 |

0001 |

- |

- |

1100 |

0011 |

0011 |

- |

1001 |

- |

Дв. сдвиг R9 |

0010 |

- |

- |

0011 |

0000 |

0111 |

0101 |

1001 |

- |

R9= |

Предварительно в регистр R9 загружают то или иное значение (см. п.2). Одинарный циклический сдвиг влево состоит в том, что старший бит регистра перезаписывается в младший и все биты сдвигаются влево.

Одинарный циклический сдвиг вправо состоит в том, что младший бит регистра перезаписывается в старший и все биты сдвигаются вправо.

При двойном сдвиге перезапись осуществляется через дополнительный четырехразрядный рабочий регистр Q.

Повторить МК несколько раз, записывая показания с выхода 1804ВС1. Объяснить результаты, используя структурную схему 1804ВС1.

К п.4. Логические операции выполняются аналогично п.2.

Литература: [1, c.277–316; 7, c.132–145; 8 ,c.351–355] .

Лабораторная работа № 4

Организация выполнения микропрограмм в микропроцессорах с разрядно-модульной организацией

Продолжительность работы – 4 часа.

Цель работы. Получение навыков составления микропрограмм (МП) для микропроцессорного комплекта К1804.

Описание лабораторного стенда. микротренажер МТ1804.

Подготовка к работе

Изучить следующие вопросы: управление адресом следующей микрокоманды (МК) в устройстве управления К1804ВУ1; организация циклов, выполнение подпрограмм и организация ветвлений в МПК 1804.

Составить микропрограммы (МП) в соответствии с заданиями табл.28-31, выданными преподавателем.

Подготовить тетрадь для отчета по лабораторной работе.

Программа работы

Ознакомится с МП, использующей команды условных, безусловных переходов и приведенной в табл. 193. Прокомментировать каждую из тетрад, приведенной МП.

табл. 193

Адрес |

Номер тетрады |

Выполняемая Адрес |

||||||||

памяти |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

операция |

след.МК |

0000 |

|

0010 |

0011 |

0111 |

0011 |

|

0100 |

0111 |

R4 = 7 |

Продолж. |

0001 |

|

0010 |

0011 |

0111 |

0011 |

|

0101 |

0101 |

R5 = 5 |

Продолж. |

0010 |

|

0010 |

0001 |

0001 |

0100 |

0101 |

0100 |

|

R4 & R5 |

Продолж. |

0011 |

0110 |

1100 |

0001 |

|

|

|

|

|

Нет загрузки |

Переход, если F=0 |

0100 |

|

0010 |

0011 |

0011 |

0001 |

|

0100 |

|

R4 = R4 – 1 |

Продолж. |

0101 |

0111 |

0001 |

0011 |

0101 |

0110 |

0101 |

0101 |

1111 |

R5 =

|

Перех.на 7 |

0110 |

|

0010 |

0011 |

0001 |

0101 |

0101 |

0100 |

|

R4 = R4 & |

Продолж. |

Изменить приведенную микропрограмму таким образом, чтобы вместо R4 и R5 использовались другие регистры АЛУ, и переход осуществлялся по другому условию. Вариант задания взять из табл. 204.

Модифицировать значения в МП таким образом, чтобы условие в команде перехода в одном случае не выполнялось, а в другом выполнялось. Затем ввести МП в микротренажер и выполнить. Записать последовательность выполнения микрокоманд в МП в случае выполнения и не выполнения условия

Ознакомится с МП, использующей команды организации циклов и приведенной в табл. 215. Прокомментировать каждую из тетрад, приведенной МП.

табл. 204

№ варианта |

Регистры вместо R4 и R5 |

Условие перехода |

№ варианта |

Регистры вместо R4 и R5 |

Условие перехода |

1. |

R1, R2 |

|

4. |

R5, R6 |

|

2. |

R2, R3 |

|

5. |

R6, R7 |

|

3. |

R3, R4 |

|

6. |

R7, R8 |

|

табл. 215

Адрес |

Номер тетрады |

Выполняемая Адрес |

|||||||||

памяти |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

операция |

след.МК |

|

0000 |

|

0010 |

0000 |

0111 |

0011 |

|

0000 |

1101 |

Q = 13 |

Продолж. |

|

0001 |

|

0010 |

0011 |

0111 |

0011 |

|

1001 |

1011 |

R9 = 11 |

Продолж. |

|

0010 |

|

0010 |

0011 |

0101 |

1001 |

1001 |

0000 |

0010 |

R0 = R9 – 2 |

Продолж. |

|

0011 |

|

1001 |

0001 |

|

|

|

|

|

Нет операции |

Загр. стек |

|

0100 |

|

0010 |

1110 |

0011 |

0011 |

|

1001 |

|

2R,2Q=R,Q |

Продолж. |

|

0101 |

|

0010 |

0011 |

0011 |

0001 |

|

0000 |

|

R0 = R0 – 1 |

Продолж. |

|

0110 |

|

1000 |

0001 |

|

|

|

|

|

Нет операции |

Окончить цикл если F=0 |

|

Изменить приведенную микропрограмму таким образом, чтобы вместо R9 и R0 использовались другие регистры АЛУ и число повторений цикла равнялось номеру варианта. Регистры замены R9, R0 и вариант задания взять такие же, как в п.2.

Затем ввести МП в микротренажер и выполнить. Записать последовательность выполнения микрокоманд в МП.

Ознакомится с МП, использующей команды работы с подпрограммами и приведенной в табл. 226. Прокомментировать каждую из тетрад, приведенной МП.

Изменить приведенную микропрограмму таким образом, чтобы вместо R0 и R1 использовались другие регистры АЛУ, а подпрограмма размещалась по адресу 9+(№ варианта). Регистры замены R0, R1 и вариант задания взять такие же, как в п.2. Затем ввести МП в микротренажер и выполнить. Записать последовательность выполнения микрокоманд в МП.

Примечание: все МП в лабораторной работе выполнить в автоматическом и пошаговом режиме, контролируя выход микросхем К1804ВУ1 и К1804ВС1. Результаты записать и сделать выводы.

табл. 226

Адрес |

Номер тетрады |

Выполняемая Адрес |

|||||||||

памяти |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

операция |

след. МК |

|

0000 |

|

0010 |

0011 |

0111 |

0011 |

|

0000 |

0110 |

R0 = 6 |

Продолж. |

|

0001 |

|

0010 |

0011 |

0111 |

0011 |

|

0001 |

1010 |

R1 = 10 |

Продолж. |

|

0010 |

1010 |

0101 |

0011 |

0100 |

0011 |

0000 |

1001 |

|

R9 = R0 |

Перех.к п/п по адр. 10 |

|

0011 |

|

0010 |

0011 |

0100 |

0011 |

1001 |

0000 |

|

R0 = R9 |

Продолж. |

|

0100 |

1010 |

0101 |

0011 |

0100 |

0011 |

0001 |

1001 |

|

R9 = R1 |

Перех.к п/п по адр. 10 |

|

0101 |

|

0010 |

0011 |

0100 |

0011 |

1001 |

0001 |

|

R1 = R9 |

Продолж. |

|

0110 |

|

0010 |

0001 |

|

|

|

|

|

|

|

|

....... |

...... |

...... |

...... |

...... |

...... |

...... |

...... |

...... |

...... |

...... |

|

1010 |

|

0110 |

0011 |

0101 |

0110 |

1001 |

1001 |

1111 |

R9 =

|

Возврат из п/п |

|