- •Введение

- •Лабораторная работа 1 моделирование цифровых схем в пакете «electronics workbench»

- •1.1.Теоретические сведения

- •1.1.1.Цифровые схемы и основные логические элементы

- •1.1.2.Пакет «Electronics Workbench»

- •1.1.3.Генератор слов (Word Generator)

- •1.1.4.Анализатор логических сигналов (Logic analyzer)

- •1.2.Задание к работе

- •1.3.Содержание отчета

- •1.4.Контрольные вопросы

- •Лабораторная работа 2 арифметические схемы

- •2.1.Теоретические сведения

- •2.1.1.Сумматоры

- •2.1.2.Вычитатели

- •2.1.3.Задержка переключения элементов

- •2.2.Задание к работе

- •2.3.Содержание отчета

- •2.4.Контрольные вопросы

- •Лабораторная работа 3 триггеры rs-типа

- •3.1.Теоретические сведения

- •3.1.1.Общая характеристика триггеров

- •3.1.2.Асинхронный rs-триггер

- •3.1.3.Синхронный rs-триггер

- •3.1.4.Динамический синхронный rs-триггер

- •3.2.Задание к работе

- •3.3.Содержание отчета

- •3.4.Контрольные вопросы

- •Лабораторная работа 4 триггеры типов d, t и jk

- •4.1.Теоретические сведения

- •4.2.Задание к работе

- •4.3.Содержание отчета

- •4.4.Контрольные вопросы

- •Лабораторная работа 5 счетчики

- •5.1.Теоретические сведения

- •5.1.1.Асинхронный счетчик

- •5.1.2.Вычитающий счетчик

- •5.1.3.Счетчик по модулю n

- •5.1.4.Реверсивный счетчик

- •5.2.Задание к работе

- •5.3.Содержание отчета

- •5.4.Контрольные вопросы

- •Библиографический список

- •644046, Г. Омск, пр. Маркса, 35

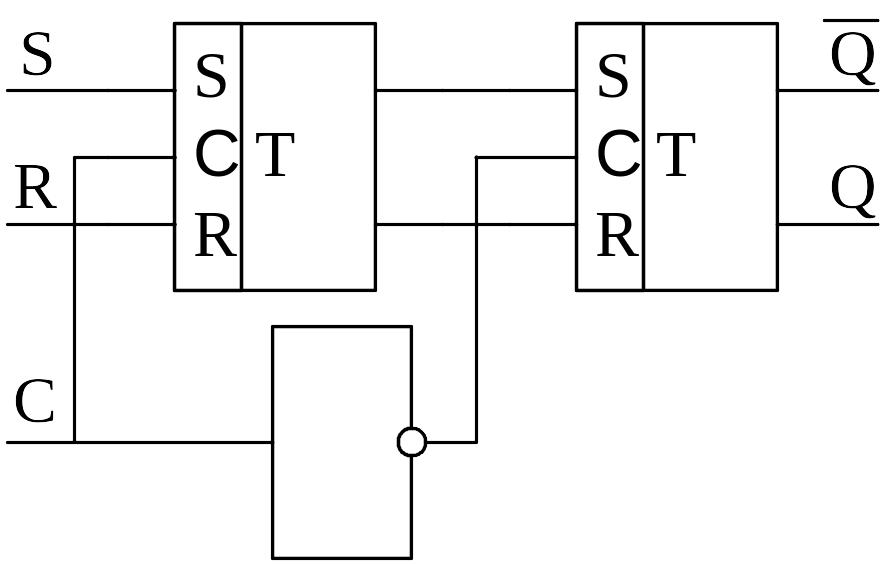

3.1.4.Динамический синхронный rs-триггер

Синхронный триггер, рассмотренный в п. 3.1.3, управляется по уровню, т. е. запоминание информации происходит при высоком уровне сигнала (логической единицы) на входе синхронизации (C). В динамических синхронных триггерах запоминание происходит по фронту управляющего сигнала (при переключении его из логической единицы в логический ноль или наоборот). Такой подход имеет некоторые преимущества. Во-первых, переключение по фронту более помехоустойчиво. Во-вторых, динамические триггеры можно подключать в цепочку (например, для создания счетчиков или регистров).

Схема динамического синхронного RS-триггера приведена на рис. 3 .15, а.

|

|

а |

б |

Рис. 3.15. Динамический синхронный RS-триггер: а – схема; б – временная диаграмма |

|

Для анализа работы RS-триггера необходимо использовать временные диаграммы, пример построения которых в пакете «Electronics Workbench» приведен на рис. 3 .15, б.

Как видно из рис. 3 .15, б, по временным диаграммам можно проследить последовательность изменения сигналов. В частности, по приведенной в примере диаграмме можно сделать вывод, что рассматриваемый триггер запоминает состояние входных сигналов, которое было во время последнего заднего фронта синхроимпульса.

Обозначение синхронного триггера, срабатывающего по переднему фронту, приведено на рис. 3 .16

|

Рис. 3.16. Обозначение динамического синхронного RS-триггера |

3.2.Задание к работе

|

Рис. 3.17. Схема асинхронного RS-триггера на элементах «и-не» |

3.3.Содержание отчета

В отчете необходимо привести все исследуемые схемы и результаты их моделирования, ответы на контрольные вопросы и выводы по работе.

3.4.Контрольные вопросы

Чем отличаются триггеры с разными способами управления?

Создайте схему синхронного триггера, отличающуюся от рассмотренной в теоретической части.

Что может произойти с асинхронным триггером при подаче на него запрещенной комбинации значений входных сигналов (рассмотреть обе предложенные схемы)?

Создайте схему синхронного триггера, имеющего дополнительные входы для безусловного сброса и установки.

Реализуйте схему динамического синхронного триггера, срабатывающего по другому фронту (по сравнению с рассмотренным).

Какие типы триггеров встроены в пакет «Electronics Workbench»?

На каких элементах реализован встроенный асинхронный RS-триггер в пакете «Electronics Workbench»?

Лабораторная работа 4 триггеры типов d, t и jk

Цель работы: изучение принципов построения и работы триггеров типов D, T и JK.

4.1.Теоретические сведения

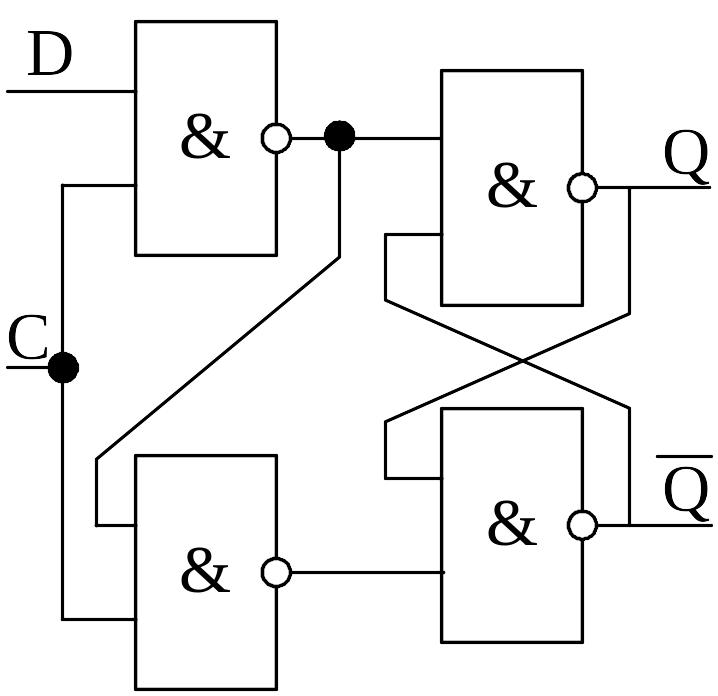

4.1.1.D-триггер

|

Рис. 4.18. Схема D-триггера |

D-триггер имеет один информационный вход D (от англ. delay – задержка). Его схема приведена на рис. 4 .18.

В случае, если на вход C подается логический ноль, то на выходе левых элементов устанавливается логическая единица и триггер находится в состоянии хранения. В случае, если на вход С подается логическая единица, то триггер запоминает состояние на входе D.

4.1.2.JK-триггер

|

Рис. 4.19. Схема JK-триггера |

4.1.3.T-триггер

T-триггер имеет только один информационный вход. При подаче на этот вход сигнала (обычно сигналом является передний или задний фронт импульса) T-триггер переключает свое состояние. Схема T-триггера проста, поэтому в работе предлагается создать ее самостоятельно.