- •Введение

- •Лабораторная работа 1 моделирование цифровых схем в пакете «electronics workbench»

- •1.1.Теоретические сведения

- •1.1.1.Цифровые схемы и основные логические элементы

- •1.1.2.Пакет «Electronics Workbench»

- •1.1.3.Генератор слов (Word Generator)

- •1.1.4.Анализатор логических сигналов (Logic analyzer)

- •1.2.Задание к работе

- •1.3.Содержание отчета

- •1.4.Контрольные вопросы

- •Лабораторная работа 2 арифметические схемы

- •2.1.Теоретические сведения

- •2.1.1.Сумматоры

- •2.1.2.Вычитатели

- •2.1.3.Задержка переключения элементов

- •2.2.Задание к работе

- •2.3.Содержание отчета

- •2.4.Контрольные вопросы

- •Лабораторная работа 3 триггеры rs-типа

- •3.1.Теоретические сведения

- •3.1.1.Общая характеристика триггеров

- •3.1.2.Асинхронный rs-триггер

- •3.1.3.Синхронный rs-триггер

- •3.1.4.Динамический синхронный rs-триггер

- •3.2.Задание к работе

- •3.3.Содержание отчета

- •3.4.Контрольные вопросы

- •Лабораторная работа 4 триггеры типов d, t и jk

- •4.1.Теоретические сведения

- •4.2.Задание к работе

- •4.3.Содержание отчета

- •4.4.Контрольные вопросы

- •Лабораторная работа 5 счетчики

- •5.1.Теоретические сведения

- •5.1.1.Асинхронный счетчик

- •5.1.2.Вычитающий счетчик

- •5.1.3.Счетчик по модулю n

- •5.1.4.Реверсивный счетчик

- •5.2.Задание к работе

- •5.3.Содержание отчета

- •5.4.Контрольные вопросы

- •Библиографический список

- •644046, Г. Омск, пр. Маркса, 35

Е. А. АЛЬТМАН, А. А. СИМАКОВ

МОДЕЛИРОВАНИЕ ЦИФРОВЫХ СХЕМ

ОМСК 2005

Министерство транспорта Российской Федерации Федеральное агентство железнодорожного транспорта

Омский государственный университет путей сообщения

––––––––––––––––

Е. А. Альтман, А. А. Симаков

МОДЕЛИРОВАНИЕ ЦИФРОВЫХ СХЕМ

Утверждено редакционно-издательским советом университета

в качестве методических указаний к лабораторным работам по дисциплине «Архитектура ЭВМ и систем»

Омск 2005

УДК 681.323 (076.5)

ББК 32.973.2-04я.73

А58

Моделирование цифровых схем: Методические указания к лабораторным работам по дисциплине «Архитектура ЭВМ и систем» / Е. А. Альтман, А. А. Симаков; Омский гос. ун-т путей сообщения. Омск, 2005. 25 с.

В методических указания рассматриваются основные логические элементы, способы построения на их основе произвольных цифровых схем и методы моделирования схем с использование пакета «Electronics Workbench».

Приведены способы построения комбинационных схем сумматоров и вычитателей, анализируется влияние задержек переключения элементов на работу схем. Описывается работа синхронного, асинхронного и динамического RS‑триггеров, изучаются метод анализа цифровых схем с помощью временных диаграмм, схемы D, T и JK-триггеров. На примере счетчиков и регистров исследуются цифровые схемы на основе триггеров.

Методические указания предназначены для студентов 3-го курса специальности 071900 – «Информационные системы и технологии», изучающих дисциплину «Архитектура ЭВМ и систем».

Библиогр.: 2 назв. Табл. 1. Рис. 20.

Рецензенты: |

канд. техн. наук, доцент А. П. Косоротов; канд. техн. наук, доцент С. А. Лунев. |

-

©

Омский гос. университет путей сообщения, 2005

ОГЛАВЛЕНИЕ

Лабораторная работа 1 МОДЕЛИРОВАНИЕ ЦИФРОВЫХ СХЕМ В ПАКЕТЕ «ELECTRONICS WORKBENCH» 6

Лабораторная работа 2 АРИФМЕТИЧЕСКИЕ СХЕМЫ 11

Лабораторная работа 3 ТРИГГЕРЫ RS-ТИПА 15

Лабораторная работа 4 ТРИГГЕРЫ ТИПОВ D, T И JK 20

Лабораторная работа 5 СЧЕТЧИКИ 21

Библиографический список 24

Введение

В настоящее время во всех сферах человеческой деятельности широкое распространение получили электронные цифровые схемы. Прежде всего это относится к микропроцессорным устройствам и электронным вычислительным машинам (компьютерам).

Методические указания содержат пять лабораторных работ (первые три рассчитаны на 2 ч аудиторных занятий, последние две – на 4), в которых рассматриваются цифровые схемы и методы их анализа, изучаются основные принципы работы цифровых устройств методом моделирования схем в пакете «Electronics Workbench».

В каждой лабораторной работе приводятся теоретические сведения, задание к работе, содержание отчета и контрольные вопросы для самопроверки.

При самостоятельной подготовке к лабораторным работам, которая проводится до начала аудиторных занятий, студентам необходимо внимательно изучить теоретические сведения, пользуясь рекомендуемой литературой и данными методическими указаниями, и определить, какие результаты должны получиться в результате моделирования. На лабораторных занятиях студенты моделируют схемы, сравнивают результаты моделирования с теоретическими и делают выводы по работе.

По результатам работы студенты оформляют отчет в соответствии с требованиями методических указаний, и утвержденных стандартов предприятия (университета).

При защите работы в установленный срок (на следующем аудиторном занятии) допускается выполнение отчетов в электронном виде.

Лабораторная работа 1 моделирование цифровых схем в пакете «electronics workbench»

Цель работы: получение навыков моделирования цифровых схем в пакете «Electronics Workbench» и оформления результатов моделирования; изучение основных логических элементов.

1.1.Теоретические сведения

1.1.1.Цифровые схемы и основные логические элементы

Цифровые схемы предназначены для обработки логических сигналов.

Логические сигналы могут принимать только два значения – логический ноль или логическая единица. Например, если на вход цифровой схемы подается сигнал напряжением больше 3 В, то он интерпретируется как логическая единица, если меньше – как логический ноль. После вычисления логической функции на выходе схемы выставляется напряжение в соответствии с полученным результатом. Уровни напряжения, которые соответствуют логическим нолям и единицам, зависят от типа микросхем.

Цифровые схемы в общем случае имеют по нескольку входов и выходов. Одним из способов описания цифровых схем являются таблицы истинности – таблицы, в которых для каждой из возможных комбинаций входных сигналов указываются соответствующие выходные.

|

|||||||||||||||

Рис. 1.1. Пример оформления таблицы истинности |

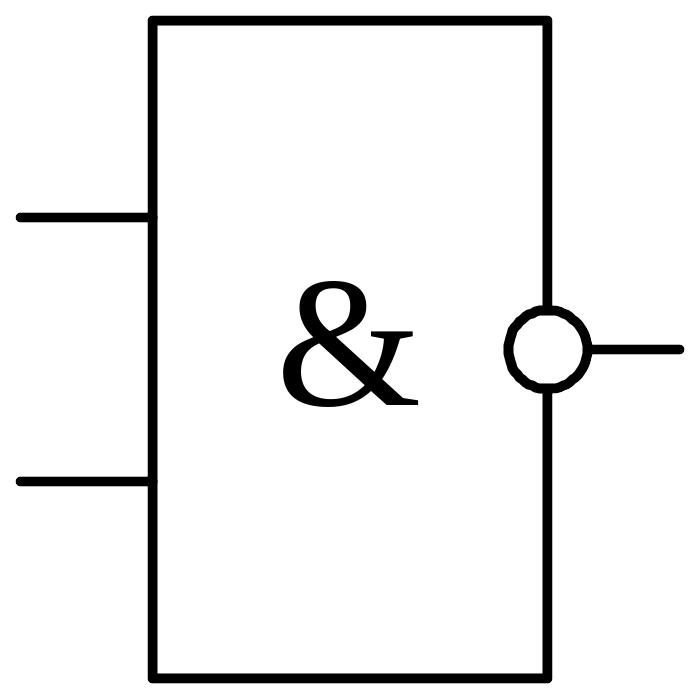

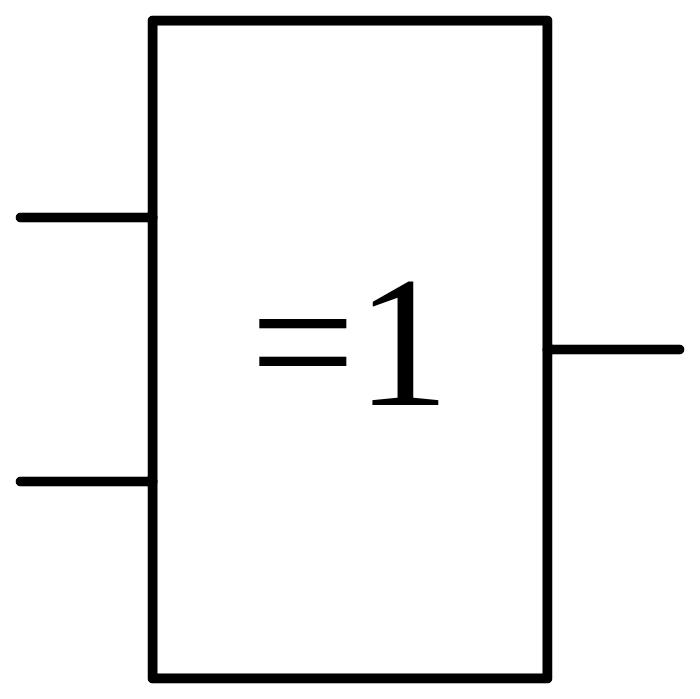

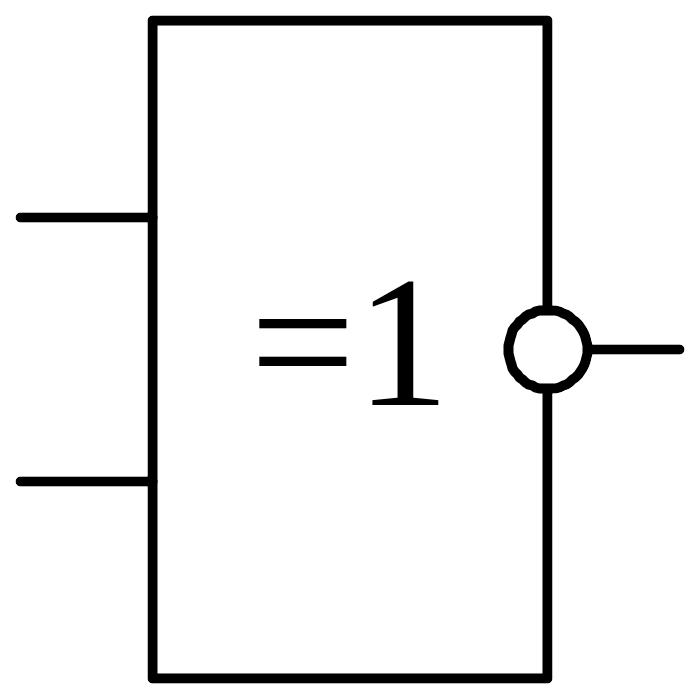

Все цифровые схемы строятся на базе небольшого числа относительно простых основных логических элементов. Названия, обозначения на схемах и таблицы истинности для основных логических элементов приведены в табл. 1 .1.

Таблица 1.1

Основные логические элементы

Международное |

Русское |

Таблица истинности |

|||||

название |

обозначение |

название |

обозначение |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

||||

not |

|

не |

|

1 |

1 |

0 |

0 |

and |

|

и |

|

0 |

0 |

0 |

1 |

or |

|

или |

|

0 |

1 |

1 |

1 |

nand |

|

и-не |

|

1 |

1 |

1 |

0 |

nor |

|

или-не |

|

1 |

0 |

0 |

0 |

xor |

|

исключающее или |

|

0 |

1 |

1 |

0 |

xnor |

|

исключающее или-не |

|

1 |

0 |

0 |

1 |