4. Репрограмувальні постійні запам’ятовувальні пристрої.

В залежності від методу стирання старої інформації розрізняють репрограмовані ПЗП з електричним та ультрафіолетовим стиранням (ПЗП типу ЕРROM та ЕЕРROM).

Мікросхеми з ультрафіолетовим стиранням – ЕРROM використовують явище зміни структури польового переходу при впливі на нього доволі високою напругою. Ці зміни зберігаються протягом досить тривалого часу. При цьому можливе стирання записаної інформації шляхом опромінення кристалу мікросхеми пам'яті через спеціальний отвір у вигляді скляного віконця. Таки ПЗП застосовували у перших поколіннях різноманітних контролерів заради надання можливості модернізації програм, записаних до них.

К

Рис. 6. Комірка пам’яті ПЗП з

ультрафіолетовим та електричним стиранням.

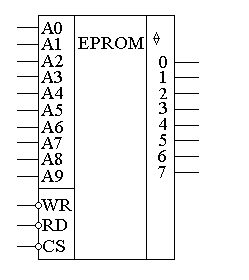

омірка пам’яті репрограмованого ПЗП (рис. 6) являє собою МОН - транзистор, в якому затвор виконується із полікристалічного кремнію. Потім в процесі виготовлення мікросхеми цей затвор окислюється і в результаті він буде оточений оксидом кремнію – якісним діелектриком. В такій комірці при повністю стертому ПЗП заряду в плаваючому затворі немає, і тому транзистор струм не проводить. При програмуванні мікросхеми на другий затвор, який знаходиться над плаваючим затвором, подається висока напруга і в плаваючий затвор за рахунок тунельного ефекту індукуються заряди. Після зняття програмуючої напруги на плаваючому затворі індукований заряд залишається, тобто транзистор залишається в провідному стані. Заряд на плаваючому затворі може зберігатися десятки років.Структурна схема даного ПЗП не відрізняється від попереднього масочного ПЗП. Єдине, що замість перемички використовується описана вище комірка. При опромінюванні мікросхеми, ізолюючі властивості оксиду кремнію втрачаються і заряд із плаваючого затвора витікає в об’єм напівпровідника і транзистор запам’ятовуючої комірки переходить в закритий стан. Час стирання мікросхеми коливається в межах 10 – 30 хвилин. Кількість циклів запису - стирання знаходиться в діапазоні від 10 до 100 разів, після чого мікросхема виходить з ладу. Репрограмовані ПЗП зображаються на принципових схемах як показано на рис. 7.

М

Рис. 7. УГП РПЗП.

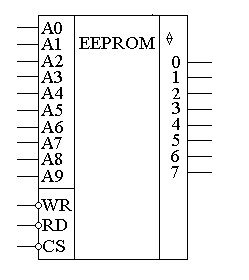

ікросхеми з електричним стиранням - ЕЕРROM (УГП зображено на рис. 8) використовують той самий ефект, що й ПЗП з ультрафіолетовим стиранням, але стирання відбувається за допомогою імпульсу відносно високої напруги на відповідний вхід мікросхеми. У багатьох ПЗП цього типу навіть передбачена часткова заміна інформації. Такі мікросхеми знайшли своє застосування там же де й мікросхеми з ультрафіолетовим стиранням. Але треба прийняти до уваги, що вони значно дорожчі ніж останні.

Рис. 8. УГП ПЗП з електричним стиранням.

FLASH пам’ять.

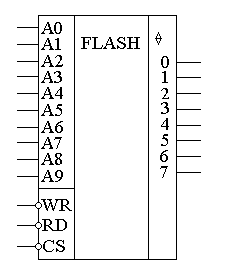

Зараз набув дуже широкого розповсюдження новий клас ПЗП з електричним стиранням, який отримав назву флеш-пам'яті (від англійського flash – спалах, блискавка). Його в певній мірі можна розглядати як симбіоз ОЗП та ПЗП, через те, що він має швидкодію, що наближується до показників ОЗП, і в той же час є енергонезалежним ЗП ЕЕРROM (УГП зображено на рис. 9).

С

Рис. 9. УГП FLASH- пам’яті.

права у тому, що комірки пам'яті у ОЗП та ПЗП мають вигляд двомірного масиву, що дозволяє читати і писати кожен біт окремо. На відміну від них, флеш-пам'ять, яка вперше була запропонована компанією TOSHIBA виготовлена у вигляді блоків місткістю від 512 б до 256 Кб. Такі блоки записуються та стираються за один машинний такт, через що вони працюють набагато швидше ніж ПЗП з електричним стиранням. Крім того, для запису даних до флеш-пам'яті не потрібна додаткова напруга, що дає змогу робити це там, де вона встановлена. В той же час для запису ПЗП з електричним стиранням потрібне спеціальне обладнання. Нажаль цей тип пам'яті не придатний для використання у якості ОЗП, якщо передбачається побайтовий запис інформації. Справа в тому, що для зміни одного байту потрібно переписати в буфер увесь блок, де утримається цей байт, потім стерти вміст блоку, змінити вміст байта, після чого провести запис зміненого в буфері блоку. Така схема значно знижує швидкість запису невеликих об’ємів інформації в довільні ділянки пам’яті, але ж значно збільшує швидкодію при послідовному запису даних великими порціями. Її життєвий цикл суттєво менший за цикл мікросхем ОЗП – усього лиш 100-300 тисяч циклів перезапису. Флеш-пам'ять використовують для запису програми BIOS (таким чином спрощується її модернізація – upgrade), там де неможливо використовувати накопичувачі на жорстких дисках. Цей тип пам'яті випускають у вигляді так-званих флеш-карт з обсягом до одиниць Гб, які застосовуються у сучасних кишенькових комп'ютерах, цифрових фотокамерах та диктофонах, електронних органайзерах.Організація FLASH пам’яті.

Комірка FLASH- пам’яті складається із МОН транзистора з плаваючим затвором, тобто за технологією виготовлення подібна комірці пам’яті ЕРROM та ЕЕРROM ПЗП. Але ж за рахунок застосування надтонкого шару діелектрика запис та стирання (інжекція заряду методом СНЕ (channel hot electrons) або його екстракція методами тунелювання) здійснюється без застосування підвищених напруг. Одна комірка зберігає один біт інформації (в сучасних розробках два, так звані багаторівневі комірки MLC) і, як правило, наявність заряду сприймається як логічний 0, відсутність як логічна 1.

При читанні, в відсутності заряду на плаваючому затворі, під дією додатного поля на керуючому затворі, утворюється n-канал між витоком і стоком, і виникає струм (логічна 1). При наявності заряду канал не з’являється і струм не виникає (логічний 0).

Архітектура (організація з’єднань між комірками) FLASH пам’яті.

Найбільш розповсюдженими на даний момент є мікросхеми з організацією NOR і NAND.

Архітектура NOR (NOТ OR, АБО-НІ).

Кожна комірка підключена до двох перпендикулярних ліній – бітів (bit line) та слів (word line) (рис. 10). Усі комірки пам’яті NOR, згідно правилам, підключені до своїх бітових ліній паралельно. Суть логічної операції NOR – в переході лінії бітів у стан 0, якщо хоча б один з транзисторів-комірок, приєднаних до неї, проводить струм. Селекція комірки здійснюється за допомогою лінії слів.

Інтерфейс паралельний. Довільне читання та запис. Швидкий довільний доступ, можливість запису побайтно. Відносно повільний запис і стирання.

Рис. 10. Структура комірки FLASH- пам’яті.

Архітектура NAND (NOТ AND, ТА-НІ).

В цьому випадку бітова лінія переходить у стан 0, якщо всі транзистори, які підключені до неї проводять струм. Комірки приєднуються до бітової лінії серіями, що знижує швидкість операції читання (зменшується струм кожної комірки), але ж підвищується швидкість стирання та програмування. Для зменшення негативного ефекту низької швидкості читання, чіпи NAND мають внутрішній регістровий кеш. В цій архітектурі більш компактна упаковка ніж в паралельній архітектурі NOR.

Інтерфейс послідовний. Швидкий запис та стирання, невеликий розмір блока. Повільний довільний доступ, але ж невеликими блоками. Немає можливості запису побайтно.

Архітектури AND (ТА), DINOR (DIVIDED BIT-LINE NOR, АБО-НІ з розділеними розрядними лініями).

Типи пам’яті, які комбінують найкращі властивості властивостей NOR і NAND. Невеликий розмір блоку, мультиблочне стирання, зберігає комірки від пережигання.

У заключній частині заняття викладач підводить підсумки заняття, звертає увагу курсантів на основні питання, винесені на заняття, рекомендує, які питання буде доцільно додатково розглянути на самостійній підготовці та повідомляє перелік рекомендованої літератури. Крім того, слід підкреслити, що наступне заняття є семінарським та видати план його проведення.

Оперативні запам’ятовувальні пристрої статичного типу.

Статична пам'ять (Static RAM -- SRAM) отримала свою назву через те, що кожен занесений до неї біт інформації може знаходитись там необмежений час без будь-якого поновлення. Єдиною умовою збереження інформації у статичних ЗП є постійна наявність електроживлення мікросхем пам'яті, тому вони, як і усі інші типи оперативної пам'яті, відносяться до енергозалежних пристроїв. При зникненні напруги живлення, уся інформація, що знаходилась у комірці такого типу пам'яті буде стерта.

Основою побудови статичних ЗП є простіші RS-тригери, реалізовані не у ТТЛ технології (яка є дуже енерговитратною) а у МОН. Наявність бістабільного елементу дозволяє приймати та видавати дані на відповідні шини комп'ютеру у будь-який момент часу майже без затримки, тобто швидкодія таких ЗП є достатньо високою. Додаткова перевага статичних ОЗП полягає в тому, що при читанні інформація не руйнується, тобто не потрібно втрачати час на її відновлення на відміну від динамічних ОЗП.

Найбільш суттєвим недоліком таких ЗП є їх відносна складність у виготовленні, особливо коли мова йде про ЗП з великою інформаційною ємністю. Неважко підрахувати, що для виготовлення найпростішого тригеру потрібні принаймні два транзистори, декілька резисторів навантаження і хоча б два конденсатори (запам’ятовуючий елемент сучасної статичної пам’яті має принаймні шість транзисторів). Тому статичні ЗП у якості основного ОЗП не використовують. Але висока швидкодія цих ЗП дозволила використовувати їх у якості буферних пристроїв пам'яті. Головне завдання їх полягає у узгодженні між собою пристроїв ЕОМ, які мають суттєву різницю у швидкодії. До речі, пристрій пам'яті, які виконує таку функцію отримав назву кеш-пам'яті.

Схематичне зображення мікросхеми ОЗП інформаційною ємністю Nx8 ілюструє рис. 5. Такий ОЗП припускає читання/запис 8-розрядного коду. Для запису 0 або 1, що надходять на входи DIO7- DIO0, потрібно на адресні входи подати код адреси, а на входи CS і W/R відповідно сигнали дозволу і читання/запису (1/0). Подача пасивного рівня на вхід ОЕ переводить мікросхему у так званий високоімпедансний стан (третій стан), тобто відключає від інформаційного обміну по шині даних. Таким чином процесор може здійснити читання/запис інформації із статичного ОЗП за два такти, що і обумовлює високо швидкодію пам’яті цього типу ( цикл звертання -- одиниці нс).

Рис. 5. УГП восьмирозрядного ОЗП

Статичні ОЗП при невеликій інформаційній ємності будуються за структурою 2D, при великій -- 2DM )з використанням мультиплексора).

Оперативні запам’ятовувальні пристрої динамічного типу.

Елементарна комірка динамічної пам'яті (Dynamic RAM – DRAM) складається з одного конденсатора і замикаючого транзистора. Це дає можливість досягти набагато більшої щільності розміщення елементів і, у результаті, значно знизити вартість ОЗП. З іншого боку, дана технологія має ряд недоліків, головним з який є те, що заряд, що накопичується на конденсаторі, згодом губиться. Незважаючи на те, що при конструюванні конденсаторів комірки динамічної пам'яті використовується гарний діелектрик з електричним опором декілька тераОм (1012 Ом), заряд конденсатора губиться дуже швидко, тому що розміри одного конденсатора мікроскопічні, а ємність мізерна (порядку 10-15 Ф). При такій ємності на такому конденсаторі накопичується усього близько 40000 електронів! Середній час витоку заряду при сучасному дизайні комірок динамічної пам'яті складає сотні навіть десятки мілісекунд. Виходить, заряд кожного осередку потрібно відновлювати протягом даного відрізка часу, інакше інформація, що зберігається в пам'яті, буде загублена.

Лекція№9

Базова архітектура CISC МК.

В дійсний час, серед усіх 8-розрядних МК, сімейство MCS51 є безсумнівним чемпіоном з кількості різновидів і кількості компаній, що випускають його модифікації. Воно одержало свою назву від першого представника цього сімейства -- МК і8051, випущеного в 1980. Вдалий набір периферійних пристроїв, можливість гнучкого вибору зовнішньої або внутрішньої програмної пам'яті і невисока вартість забезпечили цьому МК успіх на ринку. З погляду технології МК і8051 був для свого часу дуже складним виробом -- у кристалі було використано 128 тис. транзисторів, що в 4 рази перевищувало кількість транзисторів у 16-розрядному мікропроцесорі 8086.

Важливу роль у досягненні такої високої популярності сімейства 8051 зіграла відкрита політика фірми Intel, спрямована на широке поширення ліцензій на ядро 8051 серед великої кількості провідних компаній - виробників світу.

У результаті на сьогоднішній день існує більш 200 модифікацій МК сімейства 8051, що випускаються майже 20-ю компаніями. Ці модифікації містять у собі кристали з найширшим спектром периферії: від простих 20-вивідних пристроїв з одним таймером до 100-вивідних кристалів з 10-розрядними АЦП, масивами таймерів-лічильників, апаратними 16-розрядними помножувачами і 64 Кб програмної пам'яті на кристалі. Основними напрямками розвитку є: збільшення швидкодії (підвищення тактової частоти і вдосконалення архітектури), збільшення обсягу ОЗП і FLASH- пам'яті на кристалі з можливістю внутрісхемного програмування, використання складних периферійних пристроїв.

Усі МК із сімейства MCS-51 мають загальну систему команд. Наявність додаткового устаткування впливає тільки на кількість регістрів спеціального призначення.

Склад та основні характеристики базової моделі сімейства МК MCS-51

Базовою моделлю сімейства МК MCS51 і основою для всіх наступних модифікацій є МК і8051. Це -- восьмирозрядний ОМК, що має:

- вбудований тактовий генератор;

- адресний простір пам'яті програм -- 64 КБ;

- адресний простір пам'яті даних -- 64 КБ;

- внутрішню (резидентну) пам'ять програм ПЗП -- 4 КБ;

- внутрішню (резидентну) пам'ять даних ОЗП -- 128 байт;

- додаткові можливості по виконанню операцій булевої алгебри (побітових операції);

- 32 двонапрямлені й індивідуально адресовані лінії введення/виведення (порти Р0-Р3);

- послідовний порт (Serial Port);

- 2 шістнадцатирозрядні багатофункціональні таймери/лічильники (Т/С 0, Т/С 1);

- повнодуплексний асинхронний прийомопередавач;

- векторну систему переривань із двома рівнями пріоритету і шістьма джерелами подій.

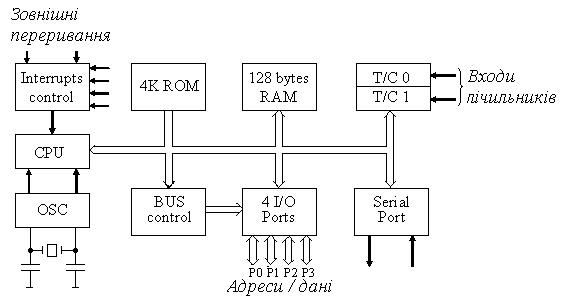

Спрощена структурна схема і8051 подана на рис. 2, призначення виводів мікросхеми -- на рис. 3.

Рис. 2. Структурна схема і8051

Bus control –блок керування; Interrupts control – система переривань; CPU – центральний процесор; OSC – генератор; ROM –ПЗП; RAM – ОЗП; I/O ports – порти введення-виведення.

Рис. 3. Призначення виводів I-8051.

Позначення сигналів на рис. 3:

Uss -- потенціал загального проводу ("землі");

Ucc -- основна напруга живлення +5 В;

XTAL1, XTAL2 -- виводи для підключення кварцового резонатора;

RESET -- вхід загального скидання МК;

PSEN -- дозвіл зовнішньої пам'яті програм;

ALE -- строб адреси зовнішньої пам'яті;

ЕА -- відключення внутрішньої програмної пам'яті;

P1 -- восьмибітний квазідвонапрямлений порт введення/виведення (кожен розряд порту може бути запрограмований як на введення, так і на виведення інформації);

P2 -- порт, аналогічний Р1; крім того, виводи цього порту використовуються для видачі адресної інформації при звертанні до зовнішньої пам'яті програм або даних;

РЗ -- аналогічний Р1; крім того, виводи цього порту можуть виконувати ряд альтернативних функцій, що використовуються при роботі таймерів, порту послідовного введення/виведення, контролера переривань, і зовнішньої пам'яті програм і даних;

P0 — восьмибітний двонапрямлений порт введення/виведення інформації.