- •Виды импульсных сигналов и их параметры.

- •Основные параметры характеризуют импульсы любой формы.

- •Производные параметры получают из основных путем пересчета.

- •Дополнительные параметры служат для характеристики специфических отличий конкретного импульса. Число этих параметров зависит от формы рассматриваемого импульса.

- •2. Экспоненциальная функция и её свойства.

- •3. Разделительная цепь при действии одиночного импульса: схема, выражения для

- •4. Прохождение последовательности прямоугольных импульсов через разделительную цепь.

- •5. Укорачивающие lcr и rc цепи: схемы, эпюры и аналитические выражения и

- •6. Влияние внутреннего сопротивления источника сигнала и емкости нагрузки на форму и параметры выходного сигнала укорачивающей цепи. Rc укорачивающая цепь

- •Влияние выходного сопротивления генератора импульсов на работу укорачивающей цепи

- •7. Дифференцирующие цепи: назначение, схема простейшей цепи,требования к

- •Дифференцирующая цепь.

- •8. Интегрирующие цепи: назначение, схема простейшей цепи, требования к постоянной времени, иц на оу интегрирующая цепь.

- •10. Фиксаторы вершины импульсов.

- •11. Последовательный диодный ограничитель: назначение, схема, принцип действия. Последовательный диодный ограничитель.

- •12. Ключевые схемы: понятие, классификация, схемы транзисторных ключей,

- •2. Транзисторные ключи.

- •2.1 Биполярные ключи

- •13. Назначение и суть метода заряда. Метод заряда.

- •Переходные характеристики ключа.

- •18. Основы Булевой алгебры: виды логических устройств, основные логические операции и их схемная реализация Логические устройства

- •Элементы булевой алгебры

- •Правила и теоремы Булевой алгебры

- •19. Понятие логических функций, способы их задания и описания.

- •20. Построение комбинационных логических схем по заданной переключательной

- •Логические функции

- •Построение комбинационной схемы

- •21. Минимизация логических функций: назначение, аналитический способ на примере трехканального приемника.

- •22. Минимизация логических функций с помощью диаграмм Вейча (циклов Карно). Минимизация логических схем

- •23. Логические элементы: классификация, основные характеристики и параметры Основные характеристики полупроводниковых логических элементов

- •Классификация л.Э.

- •24. Логические элементы ттл-логики, базовый элемент.

- •25. Генераторные устройства релаксационных колебаний, общие сведения.

- •4.1 Генераторы прямоугольных импульсов.

- •26. Триггеры: назначение, классификация.

- •4.1. Триггеры

- •34. Глин, общие сведения.

- •4.2 Глин

- •Способы генерирования лин.

- •35. Простейший глин с интегрирующей цепью: схема, принцип действия, коэффициен нелинейности.

- •36. Глин с токостабилизирующим двухполюсником: схема, принцип действия,

- •46. Устройства сравнения кодов. Цифровой компаратор (устройство сравнения кодов)

- •44. Шифраторы и дешифраторы

- •45. Мультиплексоры и демультиплексоры.

- •52. Запоминающие устройства, общие сведения.

- •51. Регистры: общие сведения, пример реализации параллельного и последовательного регистров (дополнить)

- •6.1 Последовательные (регистры …)

- •Регистр

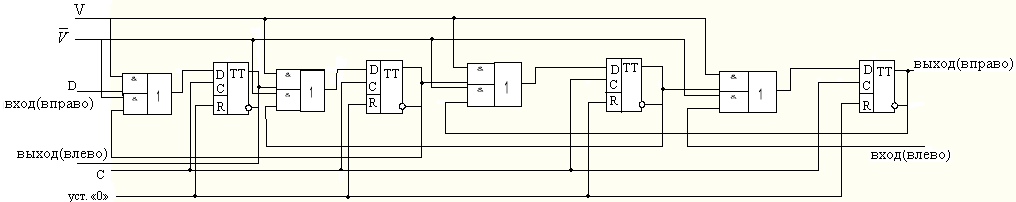

- •Регистр сдвига вправо.

- •55. Однократные пзу.

- •56. Репрограммируемые пзу. Постоянные запоминающие устройства (пзу). Диодная матрица.

- •Масочно-программируемые пзу.

- •Пзу, программируемые возбуждением тока.

- •Третья разновидность электрически программируемого пзу (эппзу).

- •Перепрограммируемые пзу.

- •30. Триггер с коллекторно-базовыми связями: схема, принцип действия. Мультивибраторы.

- •Мультивибраторы с коллекторно – базовыми связями.

- •31. Несимметричный триггер с эмиттерной связью: схема, принцип действия. Мультивибратор с эмиттерной связью.

- •33. Автоколебательный мультивибратор, схема 119гф2.

- •32. Ждущий мультивибратор схема 218гф2.

- •8 Вопрос

- •1.2.1 Фиксаторы уровня.

Регистр сдвига вправо.

Перед записью – устанавливают «0», все триггеры в «0» состоянии. Запись последовательно со входа по тактовым импульсам. Для записи N разряда числа необходимо N триггеров и N тактовых импульсов.

Считывание – последовательное – опять же N тактовыми импульсами вся информация выходит с одного выхода Q1; параллельное считывание необходимо вести после окончания N-ого тактового импульса до начала следующего N+1 импульса.

Регистр сдвига влево – получается путем подключения выхода 1-ог триггера Q1 ко входу 2-ог триггера, а выход 2-ого ко входу 3-ого и т.д. Запись начинается в том случае на чинная со старшего разряда. С помощью регистра сдвига можно осуществлять преобразование информации из последовательной формы в параллельную. Если предусмотреть запись информации параллельным кодом в регистр, то можно осуществить преобразование параллельного кода в последовательный.

. Реверсивный регистр – объединяет свойства регистров прямого и обратного сдвигов.

Отличие – дополнительная логика в межразрядных связях.

V – сигнал, управляющий направлением сдвига при V=1 – сдвиг вправо, при V=0 – влево.

Qi-1 – сигнал с выхода младшего разряда.

Qi+1 – сигнал с выхода старшего разряда.

55. Однократные пзу.

56. Репрограммируемые пзу. Постоянные запоминающие устройства (пзу). Диодная матрица.

Матрица содержит входные шины 1, 2, … С (слова) и выходные шины 1, 2, … Б (биты).

Хранимая в матрице информация фиксируется путем изъятия определенных диодов.

Например: пусть напряжение +5В («1») подается на входную шину (пусть 1), то, за счет проводимости диодов VD1, VD2, VD3 на выходную шину 1, 3, и 4 (биты) появится напряжение близкое к «1».

Входные шины могут выбираться последовательно или произвольно столько раз, сколько потребуется

Память «только для чтения» содержит в себе постоянно записанную информацию. Время, требуемое на опрос и считывание, называют временем обращения.

Недостаток: количество внешних выводов равно сумме входных шин и выходных шин С+Б. Для того, чтобы уменьшить число выводов, в чип с набором запоминания ячеек вводят вспомогательную схему: дешифратор и шифратор.

Благодаря

этому число выводов для матрицы 8

8

с 16 сокращается до 6 (3 входа + 3 выхода).

8

с 16 сокращается до 6 (3 входа + 3 выхода).

По способу замены информации в ПУЗ их можно разбить на 3 группы:

Масочно-программируемые ПЗУ – в них информация программируется изготовителем.

Программируемые током. Изготовителем выпускаются с идентичным состоянием элементов. Конструкция позволяет потребителю самому с помощью специального устройства запрограммировать необходимое число ячеек.

Перепрограммированные ПЗУ. Память может стираться и программироваться вновь.

Масочно-программируемые пзу.

Кроме диодной матрицы может быть использована транзисторная матрица, причем как на биполярной структуре, так и на полевых транзисторах.

VT1 и VT2 – нагрузочные транзисторы (на затворах постоянное смещение). Если адресуется шина слов 1, то шина битов 1 замыкается на земляной провод, а шина битов 2 подключается к Ес. Если же адресуется шина 2, то замыкаются обе шины битов.

Практическое программирование – подключение или отключение транзисторов может осуществляться двумя путями:

На стадии изготовления затвора и подключения его к соответствующей шине слов.

На стадии создания окисного слоя.