- •Серия «учебники и учебные пособия» Эрл д. Гейтс введение в электронику

- •Раздел 1 за 34

- •Глава 2 36

- •Техника безопасности

- •Меры предосторожности при работе с высоким напряжением

- •Раздел 1.

- •Глава 1. Основы электричества

- •3. Вопросы

- •4. Напряжение

- •4. Вопросы

- •5. Сопротивление

- •5. Вопросы

- •Глава 1. Самопроверка

- •Глава 2. Ток

- •1. Электрический заряд

- •V у заряд

- •1. Вопросы

- •2. Протекание тока

- •Шарики от л -

- •Пинг-понга V

- •Электронов.

- •3. Степенное представление чисел

- •Раздел 1 за

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 2

- •Глава 2. Самопроверка

- •Глава 3. Напряжение

- •2. Элементы и батареи

- •4. Приложенное напряжение и падение напряжения

- •4. Вопросы

- •5. Заземление как уровень отсчета напряжения

- •5. Вопросы

- •Глава 3. Самопроверка

- •Глава 4. Сопротивление

- •1. Сопротивления

- •6. Вопрос

- •Глава 4. Самопроверка

- •2. Вопросы

- •93 Глава 5 . Шь

- •Глава 5. Самопроверка

- •Глава 6. Электрические измерения - измерительные приборы

- •6. Отсчет показаний измерительного прибора

- •7. Вопросы

- •Глава 6. Самопроверка

- •1. Вопросы

- •2. Применение мощности (анализ цепей)

- •Раздел 1 за 34

- •Глава 2 36

- •2. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 7. Самопроверка

- •2. Параллельные цепи

- •3. Вопрос

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 8. Самопроверка

- •1. Вопросы

- •2. Вопросы

- •3. Вопросы

- •4. Применения магнетизма и электромагнетизма

- •157 Глава 9

- •4. Вопросы

- •Глава 9. Самопроверка

- •1. Вопросы

- •2. Катушки индуктивности

- •2. Вопросы

- •3. Постоянная времени l/r

- •3. Вопросы

- •Глава 10. Самопроверка

- •1. Вопросы

- •2. Конденсаторы

- •2. Вопросы

- •3. Вопросы

- •Глава 11. Самопроверка

- •Специальность — электрик

- •1. Получение переменного тока

- •Раздел 1 за 34

- •Глава 2 36

- •3. Вопросы

- •Глава 12. Самопроверка

- •1. Вопросы

- •2. Осциллографы

- •2. Вопросы

- •3. Частотомеры

- •3. Вопросы

- •Глава 13. Самопроверка

- •Раздел 1 за 34

- •Глава 2 36

- •3. Параллельные цепи переменного тока

- •4. Вопросы

- •Глава 14. Самопроверка

- •Раздел 1 за 34

- •Глава 2 36

- •2. Вопросы

- •Глава 15. Самопроверка

- •180 Градусов.

- •1. Вопросы

- •2. Вопросы

- •Глава 16. Самопроверка

- •1. Реактивное сопротивление

- •X 1114 Ом (индуктивное).

- •1. Вопросы

- •2. Вопросы

- •4. Вопрос

- •Глава 17. Самопроверка

- •Глава 18. Трансформаторы

- •1. Вопросы

- •3. Коэффициент трансформации

- •3. Вопросы

- •4. Вопросы

- •Глава 18. Самопроверка

- •Специальность — техник по электронике

- •Глава 19. Основы полупроводников

- •1. Полупроводниковые свойства германия и кремния

- •14 Электронов на орбитах

- •1. Вопросы

- •2. Вопросы

- •3. Проводимость в легированном германии и кремнии

- •3. Вопросы

- •Глава 19. Самопроверка

- •Глава 20. Диоды на основе р-n перехода

- •1. Вопросы

- •2. Смещение диода

- •3. Вопросы

- •5. Вопросы

- •Глава 20. Самопроверка

- •Глава 2 1 Як _________

- •Глава 21. Самопроверка

- •2. Вопросы

- •3. Основы работы транзистора

- •Щенный п-р-п транзистор. Щенный р-п-р транзистор.

- •4. Проверка транзисторов

- •5. Замена транзисторов

- •5. Вопросы

- •Глава 22. Самопроверка

- •1. Вопросы

- •2. Полевые транзисторы с изолированным затвором обедненного типа

- •I Подложка (п)

- •4. Вопросы

- •5. Проверка полевых транзисторов

- •5. Вопросы

- •Раздел 3

- •Глава 23. Самопроверка

- •120 Вольт

- •1. Вопросы

- •I, Управляющий электрод Рис. 24-10. Упрощенная схема конструкции триака.

- •1 120 В диак триак

- •Глава 24. Самопроверка

- •1. Введение в интегральные микросхемы

- •Шлифовка и полировка Установка для эпитаксиального

- •3. Корпуса интегральных микросхем

- •Глава 25. Самопроверка

- •3. Светоизлучающие устройства

- •Глава 26. Самопроверка

- •2. Вопросы

- •4. Вопросы

- •5. Умножители напряжения

- •5. Вопросы

- •6. Устройства защиты цепей

- •Глава 27. Самопроверка

- •Глава 28 Як

- •6. Вопросы

- •I j частоты

- •7. Вопросы

- •Выход Рис. 28-42. Блок-схема операционного усилителя.

- •8. Вопросы

- •Глава 28. Самопроверка

- •1. Основы генераторов

- •1. Вопросы

- •2. Генераторы синусоидальных колебаний

- •2. Вопросы

- •3. Генераторы несинусоидальных колебаний

- •3. Вопросы

- •Глава 29. Самопроверка

- •Глава 30. Цепи формирования сигнала

- •2. Цепи формирования сигнала

- •Диодныи ограничитель со смещением.

- •Перемене полярности диода и источника смещения в смещенном последовательном диодном ограничителе.

- •2. Вопросы

- •3. Цепи специального назначения

- •Глава 30. Самопроверка

- •Цифровые электронные цепи

- •2. Преобразование двоичных чисел в десятичные и наоборот

- •Раздел 1 за 34

- •Глава 2 36

- •2. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Раздел 1 за 34

- •Глава 2 36

- •3. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 31. Самопроверка

- •3. Вопросы

- •4. Элемент не-и

- •4. Вопросы

- •5. Элемент не-или

- •5. Вопросы

- •6. Элементы исключающее или и исключающее не-или

- •6. Вопросы

- •Гпава 32. Самопроверка

- •Глава 33. Простые логические цепи

- •1. Вопросы

- •Глава 33. Самопроверка

- •Глава 34. Последовательные логические цепи

- •1. Триггеры

- •2. Счетчики

- •2. Вопросы

- •0 0 0 0 Потеря данных

- •3. Вопросы

- •Раздел 1 за 34

- •Глава 2 36

- •Глава 34. Самопроверка

- •4. Вопросы

- •Глава 35. Самопроверка

- •1. Основы устройства компьютера

- •В память или ввод/вывод

- •Выбор ячейки памяти

- •1. Вопросы

- •2. Архитектура микропроцессора

- •Дешифратор команд

- •Манд • Указатель

- •2. Вопросы

- •Глава 36. Самопроверка

- •IPjNlPj”

- •Глава 1. Основы электричества

- •Глава 3. Напряжение

- •Глава 4. Сопротивление

- •Глава 5. Закон ома

- •Глава 6. Электрические измерения — измерительные приборы

- •Глава 7. Мощность

- •Глава 8. Цепи постоянного тока

- •Глава 9. Магнетизм

- •Глава 10. Индуктивность

- •Глава 11. Емкость

- •Глава 12. Переменный ток

- •Глава 13. Измерения переменного тока

- •Глава 14. Резистивные цепи переменного тока

- •Глава 15. Емкостные цепи

- •Глава 1c. Индуктивные цепи переменного тока

- •Глава 17. Резонансные цепи

- •Глава 18. Трансформаторы

- •Глава 19. Основы полупроводников

- •Глава 20. Диоды на основе р-п-перехода

- •Глава 21. Стабилитроны

- •Глава 22. Биполярные транзисторы

- •Глава 23. Полевые транзисторы

- •Глава 24. Тиристоры

- •Глава 25. Интегральные микросхемы

- •Глава 26. Оптоэлектронные устройства

- •Глава 27. Источники питания

- •Глава 28. Усилители

- •Глава 29. Генераторы

- •Глава 30. Цепи формирования сигнала

- •Глава 31. Двоичная система счисления

- •Глава 32. Основные логические элементы

- •Глава 33. Простые логические цепи

- •Глава 34. Последовательные логические цепи

- •Глава 35. Комбинационные логические схемы

- •Глава 36. Основы микрокомпьютеров

- •344007, Г. Ростов-на-Дону, пер. Соборный, 17 Тел.: (8632) 62-51-94

- •3. Вопросы

- •5. Вопросы

- •6. Вопросы

- •7. Мультиметры

- •1. Вопросы

- •2. Вопросы

- •2. Вопросы

- •2. Последовательные цепи переменного тока

- •1. Вопросы

- •2. Вопросы

- •4. Меры предосторожности при работе с моп транзисторами

- •2. Вопросы

- •3. Двунаправленные диодные тиристоры

- •3. Вопросы

- •4. Проверка тиристоров

- •4. Вопросы

- •1. Вопросы

- •3. Вопросы

- •1. Вопросы

- •2. Светочувствительные устройства

- •3. Вопросы

- •3. Вопросы

- •4. Регуляторы и стабилизаторы напряжения

- •1. Вопросы

- •3. Вопросы

- •4. Арифметические схемы Сумматор

- •I3. Вопросы

- •4. Цепи rlc

-

1. Вопросы

-

Какова функция диаграмм Вейча?

-

Сколько переменных может быть представлено на диаграмме Вейча?

-

Перечислите шаги при использовании диаграммы Вейча.

-

Упростите следующие выражения с помощью диаграмм Вейча.

а. ABC + АБС + ABC + ABC + ABC = Y.

б. ABCD + ABCD + ABCD + ABCD + ABCD +

ABCD + ABCD = Y.

в. AB + ABD + BCD + BC + ABCD = Y.

РЕЗЮМЕ

-

Диаграммы Вейча обеспечивают быстрый и легкий метод приведения сложных логических выражений к их простейшей форме.

-

Диаграммы Вейча могут быть составлены для двух, трех или четырех переменных.

-

Упрощенные логические выражения получаются из диаграмм Вейча путем объединения помеченных знаком X квадратов в группы из двух, четырех или восьми квадратов и последующего логического сложения объединенных выражений.

Глава 33. Самопроверка

-

Опишите процедуру использования диаграммы Вейча для упрощения логических выражений.

-

Упростите следующее Булево выражение с помощью диаграммы Вейча:

ABCD + A BCD + ACD + ABC + АВ + A BCD = Y.

Глава 34. Последовательные логические цепи

ЦЕЛИ

После изучения этой главы студент должен быть в состоянии:

-

Описать функции триггера.

-

Перечислить основные типы триггеров.

-

Нарисовать схематические обозначения триггеров.

-

Описать, как триггеры используются в цифровых цепях.

-

Описать, как работает счетчик и сдвиговый регистр.

-

Перечислить различные типы счетчиков и сдвиговых регистров.

-

Нарисовать схематические обозначения счетчиков и сдвиговых регистров.

-

Перечислить применения счетчиков и сдвиговых регистров.

Последовательные логические цепи состоят из цепей, требующих синхронизации и устройств памяти. Основным строительным блоком для последовательных логических цепей являются триггеры. Триггеры могут быть соединены вместе и образовывать счетчики, сдвиговые регистры и устройства памяти.

Триггеры принадлежат к категории цифровых цепей, которые называются мультивибраторами. Мультивибратор — это цепь с положительной обратной связью, имеющая два активных устройства, рассчитанных таким образом, что одно устройство проводит ток, в то время как другое устройство закрыто. Мультивибраторы могут хранить двоичные числа, импульсы счета, синхронизировать арифметические операции и выполнять другие полезные функции в цифровых системах.

Существуют три типа мультивибраторов: бистабильные, моностабильные и астабильные. Бистабильные мультивибраторы называются триггерами.

-

1. Триггеры

Триггер — это бистабильный мультивибратор, на выходе которого может быть либо высокое, либо низкое напряжение, то есть либо 1, либо 0. На выходе триггера остается высокое или низкое напряжение до тех пор, пока на вход не будет подан пусковой сигнал.

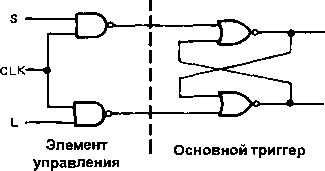

Основным

триггером является RS-триггер.

Он образован двумя прекрестно-связанными

элементами НЕ-ИЛИ или НЕ-И (рис. 34-1).

RS-триггер

имеет два выхода Q

и

Q

и

два управляющих входа, R

(Reset —

сброс) и S

(Set —

установка). На выходах триггера уровни

всегда противоположны или дополняющие:

если Q

=

1,

то Q

=

0 и наоборот.

Основным

триггером является RS-триггер.

Он образован двумя прекрестно-связанными

элементами НЕ-ИЛИ или НЕ-И (рис. 34-1).

RS-триггер

имеет два выхода Q

и

Q

и

два управляющих входа, R

(Reset —

сброс) и S

(Set —

установка). На выходах триггера уровни

всегда противоположны или дополняющие:

если Q

=

1,

то Q

=

0 и наоборот.

Рис. 34-1. Основная схема триггера.

Для того чтобы понять работу цепи, предположим что выход Q, вход R и вход S имеют низкий уровень сигнала. Низкий уровень выхода Q связан с одним из входов элемента 2 . На входе S также низкий уровень сигнала. На выходе элемента 2 высокий уровень. Этот высокий уровень связан со входом элемента 1, удерживая его выход на низком уровне. Когда на выходе Q появляется низкий уровень, говорят, что триггер находится в исходном состоянии (RESET). Он остается в этом состоянии неопределенно долго, до тех пор, пока на вход S элемента 2 не будет подан высокий уровень. Когда это произойдет, на выходе

элемента 2 появится низкий уровень, а он связан со входом элемента 1. Поскольку на входе R элемента 1 низкий уровень, на его выходе низкий уровень изменится на высокий. Этот высокий уровень связан со входом элемента 2, обеспечивая на выходе Q низкий уровень. Когда на выходе Q высокий уровень, говорят, что триггер находится в единичном (SET) состоянии. Он остается в этом состоянии до тех пор, пока на вход R не будет подан высокий уровень, переводящий триггер в исходное состояние.

«Недопустимое» или «неразрешенное» состояние имеет место, когда одновременно на оба входа, R и Э^подает- ся высокий уровень. В этом случае выходы Q и Q пытаются перейти в низкое состояние, но Q и Q не могут быть одновременно в одинаковом состоянии без нарушения работы триггера. При одновременном отключении высокого уровня со входов R и S, оба выхода пытаются перейти в состояние с высоким уровнем. Поскольку всегда логические элементы немного отличаются друг от друга, то один из них перейдет в состояние с высоким уровнем раньше. Это заставит другой элемент перейти в состояние с низким уровнем. В этом случае имеет место непредсказуемый режим работы и, следовательно, состояние выходов триггера не может быть определено.

На рис. 34-2 изображена таблица истинности для работы RS-триггера. На рис. 34-3 изображено упрощенное схематическое обозначение RS-триггера.

S Q

R Q

Входы

Выходы

S

R

Q

Q

0

0

NC

NC

0

1

0

1

1

0

1

0

1

1

?

?

NC

= не

изменяется

Рис.

34-2.

Таблица

истинности Рис.

34-3 Логическое

обо- для RS-триггера. значение

RS-триггера.

для его работы необходим дополнительный вход. Третий вход называется тактовым (или синхронизирующим) входом (CLK). На рис. 34-4 изображена логическая схема триггера с синхронизирующим входом. Сигнал высокого уровня на любом из входов входного блока триггера активизирует триггер, заставляя его изменить состояние. Входной блок, называемый «управляющим элементом», управляет или направляет тактовые импульсы на входы элементов триггера.

Рис.

34-5. Логическое Рис. 34-4. Логическая

схема обозначение тактируе-

тактируемого

RS-триггера. мого

RS-триггера.

Триггер с синхронизирующим входом управляется логическими состояниями входов R и S при наличии тактового импульса. Изменение состояния триггера происходит только по переднему фронту тактового импульса. Передний фронт тактового импульса — это переход в положительном направлении (от низкого к высокому), что означает возрастание амплитуды импульса от нулевого напряжения до положительного значения. Это называется запуск по положительному фронту (фронту импульса, запускающему цепь).

Пока уровень на тактовом входе низкий, уровни входов R и S могут изменяться, не влияя на состояние триггера. Входы R и S становятся чувствительными только в течение тактового импульса. Это называется синхронной работой. Триггер работает синхронно с тактовым сигналом. Синхронная работа важна в компьютерах и калькуляторах, когда каждый шаг выполняется в определенном порядке. На рис. 34-5 изображен логический символ, используемый для обозначения тактируемого RS-триггера.

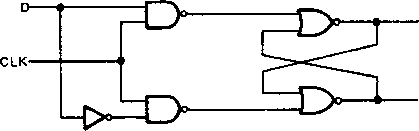

D-триггер полезен, когда должен быть сохранен только один бит данных (1 или 0). На рис. 34-6 изображена логическая схема D-триггера. Он имеет один вход для данных и вход для тактовых импульсов. D-триггер также называют триггером с задержкой. Вход D задерживает один тактовый импульс перед изменением уровня выхода (Q). Иногда D-триггер имеет вход PS (предустановка) и вход CLR (очистка). Когда на вход предустановки подан низкий уровень (0), он устанавливает выход Q в состояние 1. Когда на вход очистки подан 0, Q также устанавливается 0. D-триггеры, соединенные вместе, образуют сдвиговые регистры и регистры памяти. Эти регистры широко используются в цифровых системах.

Рис.

34-6. Логическая схема и обозначение

D-триггера.

CLK

CLK Наиболее

широко используемый триггер — это

JK-триггер.

Он обладает всеми особенностями

триггеров других типов. Логическая

схема и обозначение JK-триггера

показаны на рис. 34-7. J

и

К — это входы. Важная особенность

JK-триггера

состоит в том, что при подаче на оба

входа J

и

К высокого уровня сигнала, повторяющиеся

тактовые импульсы заставляют выход

переключаться или изменять состояние.

Два асинхронных входа, PS

(предустановка)

и CLR

(очистка),

блокируют синхронные входы, входы

данных J

и

К и вход тактовых импульсов. JK-триггеры

ши-

Наиболее

широко используемый триггер — это

JK-триггер.

Он обладает всеми особенностями

триггеров других типов. Логическая

схема и обозначение JK-триггера

показаны на рис. 34-7. J

и

К — это входы. Важная особенность

JK-триггера

состоит в том, что при подаче на оба

входа J

и

К высокого уровня сигнала, повторяющиеся

тактовые импульсы заставляют выход

переключаться или изменять состояние.

Два асинхронных входа, PS

(предустановка)

и CLR

(очистка),

блокируют синхронные входы, входы

данных J

и

К и вход тактовых импульсов. JK-триггеры

ши-

|

— |

J Q |

|

— |

CLK |

|

— |

* 01 |

роко используются во многих цифровых цепях, особенно в схемах счетчиков. Счетчики можно найти почти в каждой цифровой системе.

Защелка — это устройство, служащее временным буфером памяти. Оно используется для сохранения данных после удаления входного сигнала. D-триггер является хорошим примером защелки. Для защелки также могут быть применены другие типы триггеров.

Защелка используется на входах семисегментных индикаторов. Без защелки изображенная информация будет исчезать вместе с исчезновением входного сигнала. При наличии защелки информация сохранится на экране до тех пор, пока не будет обновлена.

На рис. 34-8 изображена 4-разрядная защелка. Это устройство содержит 4 D-триггера, заключенных в один корпус интегральной микросхемы. Входы Е (разрешение) подобны тактовому входу D-триггера. Данные фиксируются, когда уровень на входе разрешения становится низким, то

есть

равным 0. Когда уровень на входе

разрешения высокий, или 1,

уровни выходов повторяют уровни

входов. Это означает, что выход будет

изменяться при любом изменении состояния

входа; например, если на входе вы- Рис.

34-8.

Четырех- сокий

уровень, то на выходе

есть

равным 0. Когда уровень на входе

разрешения высокий, или 1,

уровни выходов повторяют уровни

входов. Это означает, что выход будет

изменяться при любом изменении состояния

входа; например, если на входе вы- Рис.

34-8.

Четырех- сокий

уровень, то на выходе

разрядная защелка. тоже появится высокий уро

вень; если на входе низкий уровень, то на выходе тоже появится низкий уровень. В таком состоянии защелка называется прозрачной.

34-1. Вопросы

-

Что такое триггер?

-

Каковы различные типы триггеров?

-

Что такое синхронизируемый триггер?

![]()

-

В чем отличие между асинхронным входом и синхронным входом?

-

Что такое защелка?