- •ОгЛыВление

- •Элементы цифровой техники, используемые в микропроцессорных устройствах

- •Общие сведения

- •Архитектура оперативного запоминающего устройства

- •Структура элементарной ячейки озу

- •Структура одноразрядного озу

- •Структура многоразрядного озу

- •Разновидности озу по доступу к информации

- •Архитектура постоянного запоминающего устройства

- •Структура элементарной ячейки пзу

- •Структура пзу

- •Увеличение объема и разрядности памяти

- •Увеличение объема памяти

- •Увеличение разрядности памяти

-

Структура пзу

ПЗУ выпускаются с разрядностью 4, 8, 16, 32 и т.д. Структура ПЗУ по своей сути очень схожа структуре ОЗУ. Исключением является отсутствие вывода WR – запись. Структурные элементы, обеспечивающие программирование ПЗУ не рассматриваются, т.к. к нормальному режиму работы не имеют отношения.

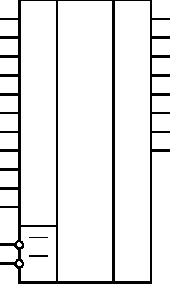

Для примера на Рис. 1 .20 представлена структура ПЗУ с организацией 4х4. В данной структуре непосредственно накопитель информации не раскрывается, т.к. тип ПЗУ (ROM, PROM, EPROM, EEPROM) не приводит к различию в структуре ПЗУ.

Рис. 1.20 Структура ПЗУ с организацией 4х8

Элементом, определяющим к какой ячейке памяти осуществляется обращение, является дешифратор. Фактически адресные сигналы A0 – A1 определяют ячейку памяти, к которой осуществляется обращение – дешифратор определяет прохождение сигнала запись RD к входу управления OE выходного буфера. Работа дешифратора разрешается сигналом CS – выборка кристалла (Chip Select).

Временная диаграмма процесса чтения информации из ячейки ПЗУ приведена на Рис. 1 .21. Для обеспечения чтения на линии адреса выставляется адрес (номер) ячейки памяти (момент времени t0), формируется сигнал CS – выборка кристалла (момент времени t1), а также сигнал чтение RD. При этом информация с выхода соответствующей ячейки памяти передается на линию данных. Считываемая информация на линии данных присутствует в течение действия сигнала RD (с момента времени tRD1 до момента времени tRD2).

Рис. 1.21 Временная диаграмма чтения из ячейки ПЗУ

На Рис. 1 .22 приведено условное графическое обозначение ПЗУ с организацией 2Кх8.

Рис. 1.22 Условное графическое обозначение ПЗУ емкостью 2Кх8

-

Увеличение объема и разрядности памяти

Увеличение объема памяти подразумевает увеличение количества ячеек памяти, а увеличение разрядности памяти подразумевает увеличение количества разрядов ячейки памяти. Увеличение объема памяти приводит к увеличению количества адресных линий, а увеличение разрядности памяти приводит к увеличению количества линий данных. Принципы увеличения объема и разрядности памяти одинаковы как для ОЗУ, так и для ПЗУ.

-

Увеличение объема памяти

Увеличение объема памяти осуществляется путем объединения микросхем памяти следующим образом. Выводы данных (D0 – Dn) и выводы адреса (A0 – An) соединяются параллельно по соответствующим разрядам. Выводы управления (RD, WR) также соединяются соответственно параллельно, а выводы CS каждой микросхемы памяти подключаются к выходам дешифратора старших разрядов адреса.

На Рис. 1 .23 приведен пример построения ОЗУ с организацией 6Кх8 на базе микросхем ОЗУ с организацией 2Кх8, а на Рис. 1 .24 приведен пример построения ПЗУ с организацией 6Кх8 на базе микросхем ПЗУ с организацией 2Кх8.

Рис. 1.23 Пример построения ОЗУ с организацией 6Кх8 на базе микросхем ОЗУ с организацией 2Кх8

Рис. 1.24 Пример построения ПЗУ с организацией 6Кх8 на базе микросхем ОЗУ с организацией 2Кх8

В обеих примерах дешифратор адреса обеспечивает обращение к соответствующей микросхеме памяти (ПЗУ или ОЗУ) в текущий момент времени, формируя сигнал CS только для одной из микросхем исходя из значения старшей части адреса. В схемах приведенных на Рис. 1 .23 и Рис. 1 .24, ячейки памяти с адресами 0000H – 07FFH расположены в микросхеме D1, ячейки памяти с адресами 0800H – 0FFFH расположены в микросхеме D2, ячейки памяти с адресами 1000H – 17FFH расположены в микросхеме D3.