- •Архитектура современных эвм

- •Содержание

- •1. Задание на курсовое проектирование

- •1.1. Исходные данные

- •2 . Структурная схема разрабатываемой системы

- •4. Форматы данных, команд и способы адресации

- •4.1. Форматы данных

- •4.2. Формат команд

- •7. Алгоритмы выполнения отдельных операций

- •7 Оп команд y1 y2 x1 y4 ram d fl a rd wr rg рд .1. Выборка команды

- •7.2. Обработка адресной части команды

- •7.3. Арифметические и логические операции

- •Память данных

- •7.6. Обработка запроса на прерывание.

- •8. Назначение сигналов

- •9. Заключение

7. Алгоритмы выполнения отдельных операций

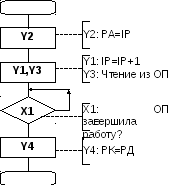

7 Оп команд y1 y2 x1 y4 ram d fl a rd wr rg рд .1. Выборка команды

Н Y3

Рис. 8

а

рис. 8 приведён фрагмент структуры

процессора, относящийся к выборке

команды, а на рис. 9 – соответствующая

ей микропрограмма.

а

рис. 8 приведён фрагмент структуры

процессора, относящийся к выборке

команды, а на рис. 9 – соответствующая

ей микропрограмма.

У

Рис. 9

7.2. Обработка адресной части команды

Рис. 10

РК

A

RG

ИР

ПА

Дш

0

1

2

3

DC

1

2

R60

X0

RG

R63

X3

RG

SE0

SE7

K

MUX

D0

.

.

D7

D8

E

E

СмИ

SM

D

РА

RG

D

E

Y8

Y7

Y5

Y6

X2

Aисп

Е сли

не используется прямая или непосредственная

адресация, то необходимо вычислить

исполнительный адрес при помощи

относительной адресации. Для реализации

относительной адресации в процессоре

предусмотрено 4 индексных регистра R60

– R63.

сли

не используется прямая или непосредственная

адресация, то необходимо вычислить

исполнительный адрес при помощи

относительной адресации. Для реализации

относительной адресации в процессоре

предусмотрено 4 индексных регистра R60

– R63.

На сумматоре производится сложение адресной части РК с индексом, находящимя в одном из индексных регистров R60 – R63. Для определения номера индексного регистра, в команде отведены поля ИР1, ИР2, ИР3. После этого исполнительный адрес заносится в РА. Структурная схема и микропрограмма приведены на рис. 10 и рис. 11.

7.3. Арифметические и логические операции

Рис. 11

РК

A3

RG

A1

INS

K

MUX

D1

SE3

SE2

РА

RG

D

E

Y9

RAM

D

END

A

RD

WR RG

РД

Y3

Y16

АЛУ

ALU

RG

RG3

Р3

ST

RG4

Р4

INS

RG2

Р2

D

E

RG1

Р1

D

E

FL

Y13

Y14

Y15

X3

A2

SE1

D2

D1

Y10

Y12

Y11

Y9,Y10:

РА=А1

X1:

ОП завершила работу?

Y13:

Р1=РД

Y3:

Чтение из ОП

Y9,Y11:

РА=А2

Y14:

Р2=РД

Y15:

Запуск АЛУ

X3:

АЛУ закончило

работу?

Y9,Y12:

РА=А3

Y16:

Запись в ОП

Рис. 12

X1

Память данных

В регистре команд уже находится очередная считанная команда в результате выборки команды. На первом этапе из памяти данных читается первый операнд, адрес которого находится в поле А1 регистра команд (то есть в текущей выполняемой команде). Операнд из РД передаётся в регистр Р1 АЛУ. Аналогично из памяти данных считывается второй операнд и заносится в Р2 АЛУ. Далее запускается устройство управления АЛУ. В соответствии с кодом операции, поступающим на АЛУ из РК, АЛУ выполняет требуемую микропрограмму. В процессе выполнения микропрограммы на Р4 АЛУ формируется результат операции, а на Р3 фиксируются признаки результата операции (равенство нулю, переполнение, перенос…). По завершении выполнения операции, АЛУ вырабатывает сигнал X1. После этого результат выполнения операции из Р4 помещается в ОП по адресу, указанному в поле А3 регистра команд.

7.4. Передача управления

7

Y17

В

Y17:

IP=Адрес

Рис. 13

РК

А

RG

INS

счётчик адресов команд просто записывается

адресная часть команды перехода.

счётчик адресов команд просто записывается

адресная часть команды перехода.

7

Flags

FL

RG

РК

КОП

RG

1

&

&

&

&

X4

П

X4:

Признак = 1 ?

Рис. 14

Команда безусловного

перехода

Нет

ри

помощи логической схемы происходит

проверка текущего признака. Если признак

= 1, то выполняется безусловный переход

ри

помощи логической схемы происходит

проверка текущего признака. Если признак

= 1, то выполняется безусловный переход

7

РК

RG

Y18

.5.

Ввод – вывод

.5.

Ввод – вывод

В

Рис. 15

A1

РА

RG

D

E

Y19

A2

КОП

РД

RG

D

E

соответствии с техническим заданием

необходимо реализовать ввод-вывод по

аналогии с ячейками памяти. Для этого

в адресном пространстве выделен диапазон

адресов для обращения к устройствам

ввода вывода. В одной из адресных частей

указывается адрес устройства ввода

вывода, а в другой – адрес слова, которое

необходимо передать в устройство или

считать из него.

соответствии с техническим заданием

необходимо реализовать ввод-вывод по

аналогии с ячейками памяти. Для этого

в адресном пространстве выделен диапазон

адресов для обращения к устройствам

ввода вывода. В одной из адресных частей

указывается адрес устройства ввода

вывода, а в другой – адрес слова, которое

необходимо передать в устройство или

считать из него.