lect3_m1_vt_mrtus_CS_niy37

.pdfЛекция 3. Синхронные триггеры

1.6. Синхронные триггеры

Синхронные (тактируемые) триггеры можно рассматривать как особый тип асинхронных триггеров, у которых существуют определённые ограничения на возможность действия входных сигналов. Это позволяет существенно упростить синтез и анализ синхронных триггеров. В синхронных триггерах допускается изменять функциональные входные сигналы только в течение времени, когда тактовые импульсы блокируют входные цепи и предотвращают изменения состояния триггера (предполагается, что синхронный триггер должен изменять свое состояние под действием тактового импульса). Важное достоинство синхронных триггеров - маскирование эффектов задержек, обусловленных задержками распространения логических элементов и линий передачи сигналов. Последнее обстоятельство позволяет считать, что логические элементы и линии имеют нулевую задержку, а выходы и состояния триггера можно рассматривать только в фиксированные моменты времени. Эти допущения существенно упрощают анализ и синтез любых синхронных устройств.

Рассмотрим, как проектируются простейшие триггеры, тактируемые потенциалом.

1.6.1. Синхронный RS-триггер

Пусть активный сигнал на C-, R- и S-входах - уровень «1». Необходимо построить схему в базисе И-НЕ. Функционирование триггера представлено в табл.1.17.

При С = 0 триггер сохраняет свое предыдущее значение, а при С = 1 работает как обычный асинхронный RS-триггер. Значения R* и S* заполняются с помощью табл.1.5.

Таблица 1.17

Таблица переходов синхронного RS-триггера

1 1 1

Номер |

Ct+1 |

Rt |

St |

Qt |

Qt+1 |

R*t+1 |

S*t+1 |

набора |

|||||||

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

8 |

1 |

0 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

10 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

11 |

1 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

12 |

1 |

1 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

15 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

Qt+1 |

S |

|

|

R* |

S |

|

|

|

|

|

|

||

1 |

1 |

1 |

0 |

1 |

1 |

1 |

C |

|

0 |

0 |

C |

|

0 |

|

|

|

|

|||

|

|

|

|

R |

1 |

R |

0 |

1 |

1 |

0 |

|

1 |

|

0 |

1 |

1 |

0 |

|

1 |

1 |

|

|

Q |

|

|

|

Q |

|

|

а |

|

|

|

б |

|

|

S* |

|

S |

|

|

|

|

|

|

|

|

|

|

|

C |

0 |

|

1 |

|

|

|

|

1 |

1 |

|

|

|

|

|

|

R |

||

|

|

|

1 |

|

1 |

|

|

|

|

|

|

||

|

|

|

1 |

|

1 |

|

|

|

|

|

Q |

|

|

|

|

|

|

в |

|

|

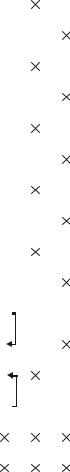

Рис.1.33. Карты Карно для синхронного RS-триггера

Рассмотрим карты Карно (рис.1.33). Из Карт Карно (рис.1.33,а) следует

Qt 1 S tCt 1 RtQt Ct 1Qt ,

откуда при С = 1 получим (1.1), а при С = 0 Qt+1 = Qt. Из карт Карно (рис.1.33,б и в) следует

R* |

|

|

|

|

|

|

|

|

|

|

; |

(1.36) |

|

C |

R |

CR |

|||||||||||

S* |

|

|

|

|

|

. |

(1.37) |

||||||

C |

S |

CS |

|||||||||||

Выражения (1.36) и (1.37) определяют структуру проектируемого триггера (рис.1.34).

R |

& |

R* |

& |

|

|

Q |

|||

|

|

|

||

|

|

|

|

C

|

& |

Q |

|

& |

|||

|

|

S

S*

Рис.1.34. Схема синхронного RS-триггера

1.6.2. Синхронный R-триггер

Пусть активный сигнал на входе С - 0, на входе RR - 0, на входе RS -1. Необходимо построить схему в базисе ИЛИ-НЕ. Функционирование триггера представлено в табл.1.18.

При С = 1 триггер сохраняет свое значение, а при С = 0 работает как обычный асинхронный R-триггер. Значения R* и S* заполняются с помощью табл.1.4.

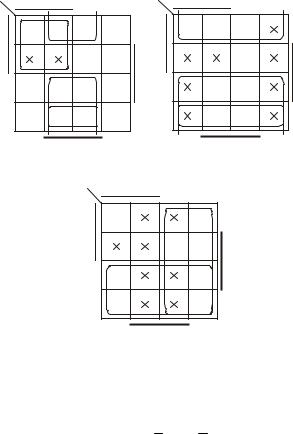

Построим карты Карно (рис.1.35). Из карты Карно (рис.1.35,а) следует

Qt+1 = Ct+1Qt + C t+1RtRRtS + RtRQt,

откуда при С = 0 получим Qt+1 = RR(RS + Qt), а при С = 1 Qt+1 = Qt. Из карт Карно (рис.1.35,б, в) следует

R* |

|

|

|

|

|

|

|

; |

|

|

(1.38) |

||||

C |

R |

C RR |

|||||||||||||

S* |

|

|

|

|

|

|

|

(1.39) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CRR RS C R R RS . |

|||||||||||||||

Выражения (1.38) и (1.39) определяют структуру проектируемого триггера, приведённую на рис.1.36.

Таблица 1.18

Таблица переходов синхронного R-триггера

|

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

Номер |

C |

RR |

RS |

Qt |

Qt+1 |

R* |

S* |

набора |

|||||||

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

2 |

0 |

0 |

1 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

1 |

|

1 |

|

|

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

8 |

1 |

0 |

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

10 |

1 |

0 |

1 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

11 |

1 |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

12 |

1 |

1 |

0 |

0 |

0 |

|

0 |

|

|

|

|

|

|

|

|

13 |

1 |

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

|

|

0 |

|

|

|

|

|

|

|

|

15 |

1 |

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

|

|

|

Qt+1 |

RS |

|

|

|

R* |

|

RS |

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

|

|

|

0 |

0 |

C |

|

|

|

RR |

C |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

|

|||

|

|

|

|

|

|

|

|

RR |

1 |

1 |

1 |

0 |

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

1 |

1 |

|

Q |

|

|

|

|

|

|

Q |

|

а |

S* |

|

RS |

|

|

|

б |

|

|

|

|

|

|

|

|

|

|

|

C |

|

0 |

|

|

0 |

|

|

|

|

0 |

|

|

0 |

|

|

|

|

|

|

|

|

RR |

||

|

|

|

|

1 |

|

|

0 |

|

|

|

|

|

|

|

|

||

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

в |

|

|

|

|

Рис.1.35. Карты Карно для синхронного R-триггера |

|||||||

RR |

1 |

R* 1 |

Q |

|

|

|

|

C |

|

|

|

|

1 |

|

|

1 |

|

|

|

1 |

|

1 |

Q |

|

S* |

|

|

RS |

|

|

|

Рис.1.36. Схема синхронного R-триггера

1.6.3. Синхронный D-триггер

Пусть активный сигнал на входе С - логическая 1. Необходимо построить схему в базисе И-НЕ. Функционирование триггера представлено в табл.1.19.

Таблица 1.19

Таблица переходов синхронного D-триггера

Номернабора C D Qt Qt+1 R* S*

0 |

0 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

2 |

0 |

1 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

3 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

4 |

1 |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

|

5 |

1 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

6 |

1 |

1 |

0 |

1 |

|

0 |

|

|

|

|

|

|

|

7 |

1 |

1 |

1 |

1 |

1 |

|

При С = 1 триггер передаёт входные данные D на выход Q, а при С = 0 сохраняет свое значение на выходе Q. Значения R* и S* заполняются с помощью табл.1.5.

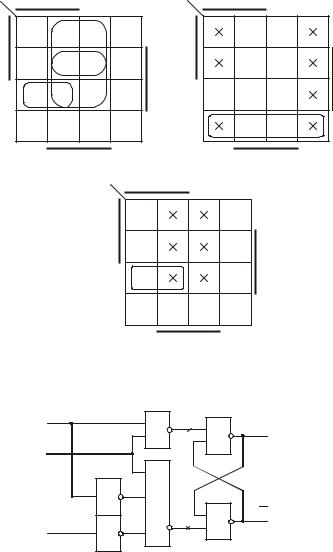

Построим карты Карно (рис.1.37).

Qt+1 |

|

D |

|

|

R |

* |

|

D |

|

S* |

|

D |

|

|

|

|

|

|

|

|

|

|

|

||||

C |

1 |

1 |

0 |

0 |

C |

1 |

1 |

0 |

C |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|||||

|

0 |

1 |

1 |

0 |

|

|

|

1 |

1 |

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Q |

|

|

|

|

|

Q |

|

|

Q |

|

|

|

|

а |

|

|

|

|

|

|

|

в |

|

|

|

|

|

|

|

|

|

|

б |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.1.37. Карты Карно для синхронного D-триггера

Из карты Карно (рис.1.37,а) следует

Qt+1 = Ct+1Dt + C t+1Qt,

откуда при С = 1 получим Qt+1 = Dt , а при С = 0 Qt+1 = Qt.

Из карт Карно (рис.1.37,б, в) следует |

|

|||||||||||

R* |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D C |

|

|

; |

(1.40) |

|||||

C |

D |

|||||||||||

S* |

|

|

|

|

|

. |

(1.41) |

|||||

C |

D |

CD |

||||||||||

Устраним инверсию D в выражении (1.40), записав R* в другом ви-

де:

R* |

|

CD . |

(1.42) |

C |

С учётом (1.41) выражение (1.42) примет вид

R* |

|

|

|

* |

|

. |

|

|

|

|

CS* |

(1.43) |

|||

C |

S |

Выражения (1.41) и (1.43) определяют структуру проектируемого триггера, приведённую на рис.1.38.

& |

R* & |

Q |

|

|

C |

& |

& |

Q |

|

S* |

||||

D |

|

|

||

|

|

|

Рис.1.38. Схема синхронного D-триггера (триггера-защёлки)

Синхронный D-триггер широко используется для построения регистров хранения, тактируемых потенциалом. Данная схема часто называется «триггер-защёлка».

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.1.39. Временные диаграммы D-триггера (триггера-защелки)

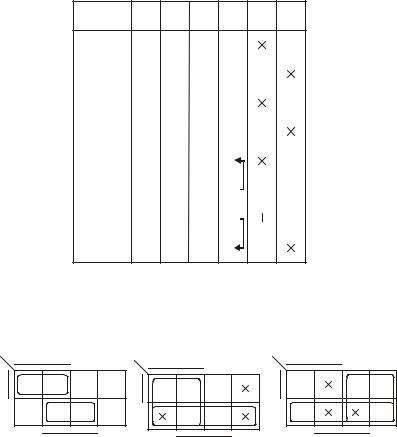

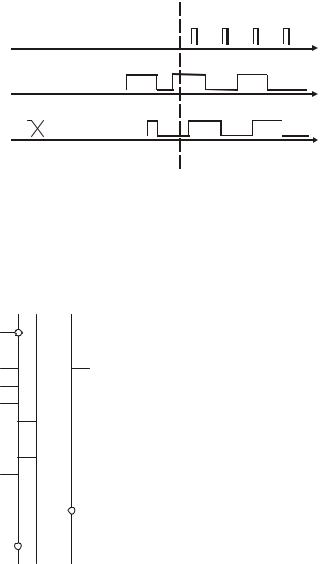

На рис.1.39 показаны временные диаграммы работы триггеразащёлки. Рекомендуемый режим синхронизации - справа от штриховой линии. Все триггеры, тактируемые потенциалом, являются прозрачными триггерами. Этот термин надо понимать следующим образом: при действии на тактовом входе активного уровня все изменения (в том числе и от помех) функциональных и информационных входов немедленно передают-

ся на выход. Поэтому длительность

|

|

|

активного |

уровня тактового сигнала |

R ТТ |

|

|||

|

должна быть минимальной, но доста- |

|||

|

|

Q |

точной для срабатывания триггера. |

|

|

|

|||

& |

|

Регистры, |

выполненные на прозрач- |

|

|

|

|||

Jных триггерах, также будут прозрач-

ными.

Пример синтеза тактируемого JK-триггера приведён в работах [2, 3]  C и здесь рассмотрен не будет. Современные JK-триггеры, выполняемые в

C и здесь рассмотрен не будет. Современные JK-триггеры, выполняемые в

&виде ИС, тактируются переходами и

|

|

|

K |

|

|

|

являются непрозрачными триггерами. |

|||

|

|

|

|

Q |

Функциональное обозначение наибо- |

|||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

лее сложного JK-триггера приведено |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

на рис.1.40, его часто называют уни- |

|

|

|

|

S |

|

|

|

||||

|

|

|

|

|

|

версальным JK-триггером. Характе- |

||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

ристическая таблица для него имеет |

|

Рис.1.40. Функциональное обозна- |

||||||||||

видтабл.1.20. |

||||||||||

чение универсального JK-триггера |

|

|||||||||

Универсальный |

JK-триггер |

|

|

Таблица 1.20 |

|||||||

может работать в четырёх режимах. |

Характеристическая таб- |

||||||||||

1. Асинхронный RS-триггер. |

|

|

лица |

||||||||

Здесь |

управление |

осуществляется |

для JK-триггера |

||||||||

по входам R и S, причём активными |

|

|

|

|

|

|

|

||||

Qt Qt+1 |

|

|

|

|

|

|

|||||

сигналами на них являются уров- |

|

|

|

|

|

|

|

||||

ни 0. На J-, K- и С-входах в этом |

00 |

|

0 |

|

|

|

|

||||

случае могут быть любые потенци- |

01 |

|

1 |

|

|

|

|

||||

алы. |

|

|

|

JK-триггер. |

|

|

|

|

|

||

2. |

Синхронный |

|

|

|

|

|

|

|

|||

10 |

|

|

1 |

|

|||||||

Здесь |

управление |

осуществляется |

|

|

|

||||||

|

|

|

|

|

|

|

|||||

отрицательным переходом на так- |

11 |

|

|

0 |

|

||||||

товом входе С. На входах JK уста- |

|

|

|

|

|

|

|

||||

Активный переход |

|

||||||||||

навливают необходимые потенциа- |

|

||||||||||

на С-входе: |

|

|

|

||||||||

|

|

|

|||||||||

лы: JK = 00 соответствует режиму |

|

|

|

||||||||

|

|

|

|

|

|

|

|||||

хранения, |

иногда |

его |

называют |

|

|

|

|

|

|

|

|

«режим блокировки тактового входа»; JK = 01 - установка триггера в |

|||||||||||

состояние |

0; JK |

= |

10 - установка |

триггера |

в состояние 1; |

||||||

JK = 11 - изменение состояния триггера на противоположное.

3.Синхронный D-триггер. В этом случае J = D, K = D .

4.Счётный триггер. В этом случае J = K = 1, а C = T.

Временная диаграмма, представленная на рис.1.41, в обобщённом виде отражает все перечисленные выше режимы работы универсального JK-триггера.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

J |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||||

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

||

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Рис.1.41. Временные диаграммы универсального JK-триггера