lect3_m1_vt_mrtus_CS_niy37

.pdf

J* |

x0 |

K* |

x0 |

|

0 |

|

|

0 |

|

x2 |

|

x2 |

1 |

0 |

0 |

0 |

|

||

0 |

x1 |

|

1 |

x1 |

|

|

|

||

1 |

1 |

|

1 |

0 |

|

Q |

|

|

Q |

|

а |

|

|

б |

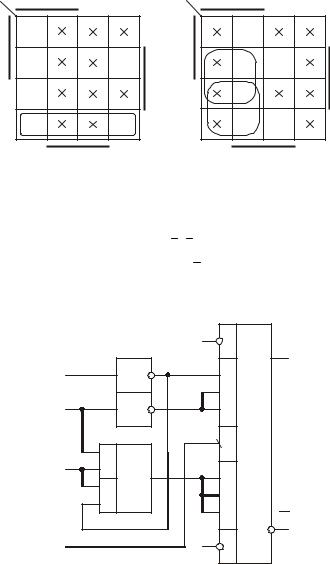

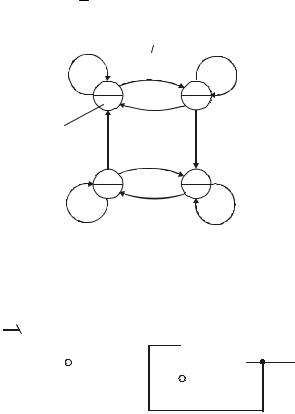

Рис.1.59. Карты Карно для функций возбуждения J*, K* |

||||

Рассмотрим карты Карно (рис.1.59). Из карт Карно (рис.1.59) следует

J *t x2 x1 ;

K*t x1x0 x2 x0 .

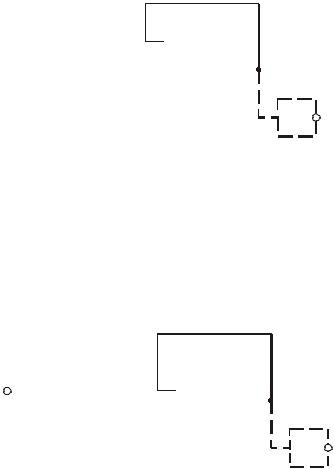

Окончательная схема триггерного устройства представлена на рис.1.60 (см. также примечание к примеру 1).

|

|

R |

ТТ |

Q |

x2 |

1 |

& |

|

|

x1 |

1 |

J |

|

|

|

|

|

||

x0 |

& 1 |

C |

|

|

& |

|

|

||

|

|

|

|

|

|

& |

K |

|

|

|

|

|

|

|

|

|

|

|

Q |

ТИ |

|

S |

|

|

|

|

|

|

|

Рис.1.60. Схема триггерного устройства на JK-триггере |

||||

1.7.Реализация триггеров на мультиплексорах

ипостоянных запоминающих устройствах

1.7.1.Реализация триггеров на мультиплексорах

Хотя мультиплексор является комбинационной схемой, возможность построения на нем триггера определяется двумя обстоятельствами. Во-первых, совпадением по форме уравнения, описывающего выходной сигнал мультиплексора, и характеристического уравнения триггера (уравнения следующего состояния). Во-вторых, возможностью организации ячейки памяти путём введения положительной обратной связи подключением сигнала с выхода мультиплексора на его информационные входы. Последнее можно осуществить только при использовании ИС мультиплексоров, так как элементы И и ИЛИ, на которых реализованы их схемы, выполнены как структуры И = И-НЕ-НЕ и ИЛИ = ИЛИ-НЕ-НЕ.

Если мультиплексор реализован, например, на пассивных диоднорезисторных схемах И и ИЛИ, то на нем нельзя организовать цель с положительной обратной связью и, следовательно, нельзя построить триггер.

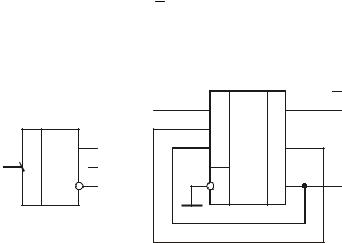

Рассмотрим простой |

пример. Пусть требуется построить на |

||||

МS 2→1, тактируемый высоким |

потенциалом D-триггер |

(триггер- |

|||

защелку). Характеристическое уравнение для него имеет вид |

|

||||

Qt 1 |

Ct 1Qt Ct 1Dt . |

(1.58) |

|||

Уравнение, описывающее МS 2→1, имеет вид |

|

||||

y |

a |

0 D0 |

a0 D1 , |

(1.59) |

|

где а0 - одноразрядный адрес мультиплексора; D0 и D1 - входные сигналы; у - выход мультиплексора.

Прежде всего отметим внешнее сходство уравнений (1.58) и (1.59). Учитывая, что Qt+1 и Qt это одна и та же точка схемы в разные моменты времени, делаем вывод, что тактовый сигнал С надо подавать на адресный вход мультиплексора, вход D0 нужно соединить с выходом мультиплексора, который и является выходом триггера, а на вход D1 надо подавать внешние входные данные D. Схема триггера приведена на рис.1.61. В данной схеме реализуется триггер только с прямым выходом

Q. Если нужно иметь и выход Q , то необходимо добавить инвертор.

|

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

D0 |

MS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||||

|

C |

|

|

|

D1 |

|

y |

|

Q |

|||

|

|

|

|

C |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

1 |

|

|

Q |

||

|

|

|

|

|

|

|

|

|

|

|

||

б

Рис.1.61. D-триггер (Сакт = 1) на мультиплексоре MS «из 2 в 1»

Пусть теперь требуется построить на МS 2→1 тактируемый низким потенциалом D-триггер (триггер-защёлку). Характеристическое уравнение для триггера такого типа имеет вид

|

t 1 |

|

|

t 1 |

|

t |

|

t 1 t |

|

|

|

Q |

C |

D |

C |

. |

(1.60) |

||||||

|

|

|

Q |

||||||||

Сравнивая (1.60) с уравнением (1.59) делаем вывод, что тактовый сигнал С надо подавать на адресный вход мультиплексора, на вход D0 надо подавать внешние входные данные D, а вход D1 нужно соединить с выходом мультиплексора, который и является выходом триггера, приведённого на рис.1.62.

|

D |

T |

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

|

D0 |

MS |

|

|

Q |

|||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|||||||

|

C |

|

|

C |

|

D1 |

|

y |

|

|||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

Q |

|||

|

|

|

|

|

|

|

|

|

|

|

||

б

Рис.1.62. D-триггер (Сакт = 0) на мультиплексоре MS «из 2 в 1»

Полученные D-триггеры являются прозрачными. Однако, чередуя триггеры с различными активными сигналами на тактовых входах, можно построитьнепрозрачныетриггеры, срабатывающиеот переходов 01 или10. Используя непрозрачные триггеры, можно реализовать сдвиговые регистры, кольцевые счётчики, счётчики с произвольным модулем счёта, пересчётные устройстваидругиепростейшиецифровыеавтоматы.

1.7.2. Реализация счётного триггера на ПЗУ

Реализация триггеров на ПЗУ, которые являются чисто комбинационными схемами, также основана на использовании положительной обратной связи, реализуемой соединением одного разряда выходного слова с одним адресным входом. Каждая положительная обратная связь соответствует одной элементарной запоминающей ячейке. Положительная обратная связь обеспечивается тем, что все полупроводниковые ПЗУ имеют выходные буферные усилители, выполненные по структуре НЕ-НЕ.

Первое, что нужно сделать при реализации триггера любого типа на ПЗУ, это определить минимальную необходимую конфигурацию ПЗУ. Под конфигурацией ПЗУ понимается количество и разрядность хранимых слов. Она может быть определена, если известно число входов проектируемого триггера, число элементарных запоминающих ячеек в составе его структуры и требуемая реализация его выхода (однофазная, когда доступен только прямой выход Q, и парафазная, когда

доступны Q и Q ).

Второе, что нужно сделать, - это оформить граф переходов проектируемого триггера и закодировать состояния его элементарных запоминающих ячеек, для чего надо выполнить все процедуры этапа абстрактного синтеза.

В дальнейшем все процедуры этапа структурного синтеза просто заменяются кодированием содержимого ПЗУ (точнее элементов связи между адресными и разрядными линиями) с использованием информации, заложенной в графе переходов.

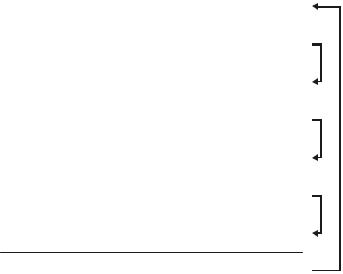

Рассмотрим пример проектирования на ПЗУ счётного триггера при выполнении следующих требований: триггер должен изменять состояние выхода на противоположное по переходу 10 на тактовом входе; выход триггера необходимо реализовать в парафазном виде. Определяем минимальную конфигурацию ПЗУ. При выполнении процедур абстрактного синтеза счётного триггера мы выяснили (см. раздел 1.5.6), что его структура содержит две элементарные запоминающие ячейки, следовательно, при использовании ПЗУ нужно организовать две положительные образные связи (соединить два разряда выходного слова с двумя разрядами адреса). Один из разрядов адреса будем использовать в качестве счётного входа Т, поэтому разрядность адреса будет равна трем (вход Т и два входа для обратной связи). Один из разрядов выходного слова, соединенный с разрядом адреса, можно использовать в ка-

честве выхода Q, а для выхода Q используем ещё один дополнитель-

ный разряд выходного слова. Итак, разрядность выходного слова должна равняться трем, а минимальная конфигурация ПЗУ будет 8х3, т.е. ПЗУ должно содержать восемь трёхразрядных слов. Схема счётного триггера на ПЗУ представлена на рис.1.63.

|

|

T |

a2 |

ROM |

Q |

|

|

|

Q2 |

||

TT |

Q |

|

a1 |

|

|

|

a0 |

|

Q1 |

||

|

|

|

|||

T |

Q |

|

|

|

Q |

|

|

cs |

|

||

|

|

|

|

Q0 |

а

б

Рис.1.63. Счётный триггер на ПЗУ

Теперь составим таблицу, обеспечивающую кодирование ПЗУ (табл.1.31). В таблице разряды выходного слова Q2, Q1, Q0 расположены неупорядоченно для удобства её заполнения, так как a1 = Q1 и a0 = Q0. Закодируем по адресу a2a1a0 = 000 выходное слово Q1Q0Q2 = 001. Если теперь соединить a1 c Q1 и a0 c Q0, то схема будет устойчивой, так как a1 = Q1 = 0 и a0 = Q0 = 0. Изменим теперь значение Т на 1, оставив значение а1а0 = 00, т.е. установим адрес 4. Из графа (см. рис.1.28) следует, что состояние Q1Q2 = 00 (в табл.1.31 оно обозначено соответственно как Q1Q0) перейдет в состояние 10. Закодируем по адресу 4 слово Q1Q0Q2 как 101. Если теперь соединить а1 с Q1 и а0 с Q0, то видно, что схема будет неустойчивой, так как а1 Q1. Оставляя адресную переменную Т = 1 без изменения, изменим набор а1а0 = 00 на набор 10, т.е. установим адрес 6 и закодируем по этому адресу то же слово, что и по адресу 4. Теперь строка с адресом 6 будет соответствовать устойчивому состоянию схемы. Стрелки справа от табл.1.31 отражают переходные процессы от неустойчивых состояний к устойчивым. Аналогично заполняются все строки в табл.1.31.

Таблица 1.31

Таблица кодирования ПЗУ

|

T t+1 |

Q1 |

Q0 |

a1 |

a0(Q) |

|

|

|

|

Номер |

|

Q |

|||||||

набора |

|

|

|

|

|

|

|

|

|

a2 |

a1 |

a0 |

Q1 |

Q0 |

Q2 |

||||

|

|||||||||

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

||

|

|

|

|

|

|

|

|

|

|

4 |

1 |

0 |

0 |

1 |

0 |

1 |

|

||

|

|

|

|

|

|

|

|

|

|

6 |

1 |

1 |

0 |

1 |

0 |

1 |

|

||

|

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

0 |

1 |

1 |

0 |

|

||

|

|

|

|

|

|

|

|

|

|

3 |

0 |

1 |

1 |

1 |

1 |

0 |

|

||

|

|

|

|

|

|

|

|

|

|

7 |

1 |

1 |

1 |

0 |

1 |

0 |

|

||

|

|

|

|

|

|

|

|

|

|

5 |

1 |

0 |

1 |

0 |

1 |

0 |

|

||

1 |

0 |

0 |

1 |

0 |

0 |

1 |

|

||

|

|

|

|

|

|

|

|

|

|

Для оператора, осуществляющего кодирование ПЗУ на программаторе, табл.1.31 надо представить с упорядоченным расположением разрядов адреса и выходного слова (табл.1.32).

Для любого специалиста табл.1.32 говорит о том, что в ней закодированы какие-то данные, и только разработчик знает, что, обеспечив соединения, указанные на рис.1.63,б, он получит счётный триггер, срабатывающий по переходу 10 на тактовом вводе и имеющий парафазный выход.

Таблица 1.32

Таблица кодирования ПЗУ с упорядоченными адресами

Номер |

a2 |

a1 |

a0 |

Q2 |

Q1 |

Q0 |

|

набора |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

2 |

0 |

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

3 |

0 |

1 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

4 |

1 |

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

5 |

1 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

6 |

1 |

1 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

7 |

1 |

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

1.7.3. Реализация синхронного JK-триггера на ПЗУ

Пусть требуется закодировать в ПЗУ синхронный JK-триггер при выполнении следующих требований: триггер должен срабатывать по отрицательному переходу на тактовом входе С, активные сигналы на J- и K-входах - потенциальные с уровнем 1 (для положительной логики); выход триггера - парафазный. Выполним процедуры абстрактного синтеза для того, чтобы узнать, сколько обратных связей должно использоваться для реализации этого CJK-триггера. Первичная таблица переходов (табл.1.33) имеет 16 строк, так как всего будет восемь наборов CJK и предполагается, что на каждом наборе триггер имеет два устойчивых состояния выхода (0 и 1), определяемых различными состояниями его внутренней структуры.

Таблица 1.33

ПервичнаятаблицапереходовсинхронногоJK-триггера(динами- ка)

Номер |

|

|

|

CJK |

|

|

|

||

|

|

|

|

|

|

|

|

||

набора |

|

|

|

|

|

|

|

|

|

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

||

|

|||||||||

|

|

|

|

|

|

|

|

|

|

1 |

(1), 0 |

3 |

5 |

7 |

9 |

11 |

13 |

15 |

|

|

|

|

|

|

|

|

|

|

|

2 |

(2), 1 |

4 |

6 |

8 |

10 |

12 |

14 |

16 |

|

|

|

|

|

|

|

|

|

|

|

3 |

1 |

(3), 0 |

5 |

7 |

9 |

11 |

13 |

15 |

|

|

|

|

|

|

|

|

|

|

|

4 |

2 |

(4), 1 |

6 |

8 |

10 |

12 |

14 |

16 |

|

|

|

|

|

|

|

|

|

|

|

5 |

1 |

3 |

(5), 0 |

7 |

9 |

11 |

13 |

15 |

|

|

|

|

|

|

|

|

|

|

|

6 |

2 |

4 |

(6), 1 |

8 |

10 |

12 |

14 |

16 |

|

|

|

|

|

|

|

|

|

|

|

7 |

1 |

3 |

5 |

(7), 0 |

9 |

11 |

13 |

15 |

|

|

|

|

|

|

|

|

|

|

|

8 |

2 |

4 |

6 |

(8), 1 |

10 |

12 |

14 |

16 |

|

|

|

|

|

|

|

|

|

|

|

9 |

1 |

3 |

5 |

7 |

(9), 0 |

11 |

13 |

15 |

|

|

|

|

|

|

|

|

|

|

|

10 |

2 |

4 |

6 |

8 |

(10), 1 |

12 |

14 |

16 |

|

|

|

|

|

|

|

|

|

|

|

11 |

1 |

3 |

5 |

7 |

9 |

(11), 0 |

13 |

15 |

|

|

|

|

|

|

|

|

|

|

|

12 |

1 |

3 |

5 |

7 |

10 |

(12), 1 |

14 |

16 |

|

|

|

|

|

|

|

|

|

|

|

13 |

2 |

4 |

6 |

8 |

9 |

11 |

(13), 0 |

15 |

|

|

|

|

|

|

|

|

|

|

|

14 |

2 |

4 |

6 |

8 |

10 |

12 |

(14), 1 |

16 |

|

|

|

|

|

|

|

|

|

|

|

15 |

2 |

4 |

6 |

8 |

9 |

11 |

13 |

(15), 0 |

|

|

|

|

|

|

|

|

|

|

|

16 |

1 |

3 |

5 |

7 |

10 |

12 |

14 |

(16), 1 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

2 |

|

|

|

|

||

11 |

|

3 |

14 |

4 |

12 |

13 |

|||||

9 |

|

|

|

5 |

10 |

|

|

|

6 |

16 |

15 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||

7 |

|

|

|

|

8 |

|

|

|

|

||

|

|

Рис.1.64. Диаграмма совместимых состояний |

|

|

|||||||

Оформляем диаграмму совместимых состояний (рис.1.64).

Из рис.1.64 видно, что структура СJK-триггера содержит две элементарные запоминающие ячейки, так как всего четыре различных состояния, следовательно, при реализации на ПЗУ будут необходимы две положительные обратные связи.

Далее оформляем сокращённую таблицу переходов (табл.1.34), выбрав четыре различных состояния с номерами 1, 2, 12 и 13.

|

Сокращённая таблица переходов |

Таблица 1.34 |

||||||

|

|

|

||||||

Номер |

|

|

|

CJK |

|

|

|

|

|

|

|

|

|

|

|

|

|

состояния |

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

1 |

(1), 0 |

(1), 0 |

(1), 0 |

(1), 0 |

(1), 0 |

(1), 0 |

13 |

13 |

2 |

(2), 1 |

(2), 1 |

(2), 1 |

(2), 1 |

(2), 1 |

12 |

(2), 1 |

12 |

12 |

1 |

|

1 |

1 |

2 |

(12), 1 |

2 |

(12), 1 |

13 |

2 |

2 |

2 |

2 |

1 |

1 |

(13), 0 (13), 0 |

|

По табл.1.34 строим граф переходов (рис.1.65).

Определяем минимальную конфигурацию ПЗУ. Адрес ПЗУ должен быть пятиразрядным: один разряд - вход С, второй разряд - вход J, третий разряд - вход K, четвертый и пятый разряды - для организации двух положительных обратных связей. Выходное слово ПЗУ должно быть трёхразрядным: два разряда для организации двух положительных обратных связей (один из которых - прямой выход Q триггера) и один раз-

ряд - инверсный выход Q . Итак, минимальная конфигурация ПЗУ 32×3. Схема CJK-триггера на ПЗУ представлена на рис.1.66.

000 |

|

CJK |

|

|

|

110 |

|

||

001 |

|

110 |

||

010 |

|

111 |

||

011 |

1 |

13 |

111 |

|

100 |

|

|||

00 |

10 |

|

||

101 |

|

|||

|

100 |

|

||

|

000 |

000 |

||

Q1Q2 |

101 |

|||

001 |

001 |

|||

|

||||

|

010 |

100 |

010 |

|

|

011 |

011 |

||

|

110 |

|||

|

|

|

||

|

12 |

2 |

000 |

|

101 |

01 |

11 |

001 |

|

|

|

010 |

||

111 |

|

101 |

||

|

011 |

|||

|

|

111 |

||

|

|

100 |

||

|

|

|

110 |

Рис.1.65. Граф переходов CJK-триггера на ПЗУ

|

|

|

|

Q |

C |

a4 |

ROM |

|

|

|

|

|

||||

|

J |

TT |

|

J |

a3 |

|

Q2 |

|

|

Q |

||||||

|

|

|

|

K |

|

|

|

|

|

|||||||

|

|

|

|

|

|

a2 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

a1 |

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

a0 |

|

|

|

|

|

|

|

K |

|

|

Q |

|

|

|

|

|

Q0 |

|

Q |

||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

cs |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б

Рис.1.66. CJK-триггер на ПЗУ

Оформляем таблицу, обеспечивающую кодирование ПЗУ (табл.1.35), используя граф переходов (см. рис.1.65). Для удобства её заполнения адресные переменные а4, а3, а2, а1, а0 сразу расположим упорядоченно, а выходные переменные в таком порядке: Q1, Q0, Q2. Неустойчивые состояния пометим звездочкой, а стрелкой укажем переход к устойчивому состоянию.