Электроника учебное пособие

.pdfтока. При этом различают положительную и отрицательную логики. В по- ложительной логике значению логической единицы ставят в соответствие большее, а значению логического нуля – меньшее значение напряжения или тока. В отрицательной логике наоборот – большему значению электрического сигнала соответствует значение логического нуля, а меньшему – значение логической единицы. Это определение справедливо для любой полярности используемого напряжения и любых направлений протекания тока.

При импульсном способе представления значению логической единицы может быть поставлен в соответствие сам факт наличия импульса или его положительный перепад, а значению логического нуля – отсутствие импульса или его отрицательный перепад.

Основное отличие двух способов заключается в требовании к моментам времени, когда можно измерять значения сигналов. При потенциальном способе представления значение логической переменной может быть определено в любой произвольный момент времени. При импульсном представлении это возможно только в строго определенные дискретные моменты времени. Таким образом, при потенциальном способе представления возможен как синхронный, так и асинхронный режим работы устройства. При импульсном представлении – лишь синхронный режим.

Для нормальной надежной работы реальных цифровых устройств необходимо, чтобы все логические элементы, входящие в его состав, удовлетворяли ряду фундаментальных свойств, например, таким как совместимость уровней входных и выходных сигналов, помехоустойчивость, нагрузочная способность, быстродействие и др.

Совместимость уровней входных и выходных сигналов. Для совмест-

ного использования большого числа логических элементов должно гарантироваться согласование уровней сигналов, представляющих значения логических переменных. Это означает, что установившиеся отклонения выходного напряжения логического элемента, вызванные влиянием различных внешних и внутренних факторов, не должны превышать некоторые наперед заданные значения, т.е.

U1min ≤ Ut1 ≤ U1max ,

Umin0 ≤ Ut0 ≤ Umax0 ,

141

где Ut – текущее значение выходного напряжения логического элемента.

Следовательно, формирование на выходе сигнала Umax0 < Ut < U1min недопустимо.

Для повышения надежности работы цифровых устройств допустимая область изменения входного сигнала логического элемента, распознаваемая как соответствующий логический уровень, должна быть шире выходной:

Uвых1,0 max < Uвх1,0max ,

Uвых1,0 min > U1вх,0min .

Помехоустойчивость логической схемы – это способность схемы переносить воздействие шумов (нежелательных паразитных сигналов) без влияния на выходные уровни напряжения.

Нагрузочная способность логического элемента характеризует его способность получать сигнал от нескольких источников информации и одновременно быть источником информации для других элементов. Для численной характеристики нагрузочной способности используют два коэффициента – коэффициент объединения по входу и коэффициент разветвления по выходу.

Коэффициент объединения по входу Kоб (fan-in) численно равен максимальному числу выходов однотипных логических элементов, которые одновременно могут быть подключены ко входу данного вентиля, не вызывая при этом искажений формы и амплитуды его сигнала.

Коэффициент разветвления по выходу Kраз (fan-out) численно равен

максимальному числу входов однотипных логических элементов, которые одновременно могут быть подключены к выходу данного вентиля, не вызывая при этом искажений формы и амплитуды его сигнала.

Типовые значения коэффициентов Kоб = 2 … 8, Kраз = 4 … 10.

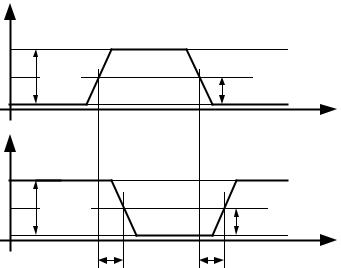

Быстродействие характеризуют временем задержки распространения сигнала tзр и максимальной рабочей частотой Fmax . Различают время

задержки распространения при переключении из состояния логической единицы в логический нуль (tзр10 ) и при переключении из состояния логи-

ческого нуля в логическую единицу (tзр01), а также среднее время задержки распространения tзр = 0,5(tзр10 + tзр01 ). Время задержки принято

142

определять по перепадам уровней 0,5 |

Uвх и 0,5 |

Uвых (рис. 13.1). Макси- |

|

мальная рабочая частота Fmax – это частота, при которой сохраняется но- |

|||

минальная работоспособность схемы. |

|

|

|

uвх |

|

|

|

U1 |

|

|

|

вх |

|

|

|

U0 |

Uвх |

|

0.5ΔUвх |

вх |

|

|

t |

uвых |

|

|

|

|

|

|

|

U1 |

|

|

|

вых |

|

|

|

U0 |

Uвых |

|

0.5ΔUвых |

вых |

|

|

t |

|

tзр10 |

tзр01 |

|

|

|

||

Рис. 13.1. Время задержки распространения |

|||

Основные логические операции могут быть реализованы с использованием различных схемотехнических решений. В настоящее время только некоторые из них находят широкое практическое использование. Рассмотрим наиболее распространенную классификацию реализаций логических элементов. Выделяют следующие классы логики:

∙резисторно-транзисторная логика (РТЛ);

∙диодно-транзисторная логика (ДТЛ);

∙транзисторно-транзисторная логика (ТТЛ);

∙эмиттерно-связанная логика (ЭСЛ);

∙логика на однотипных полевых транзисторах (n-МОП и p-МОП);

∙логика на комплементарных полевых транзисторах (КМОП).

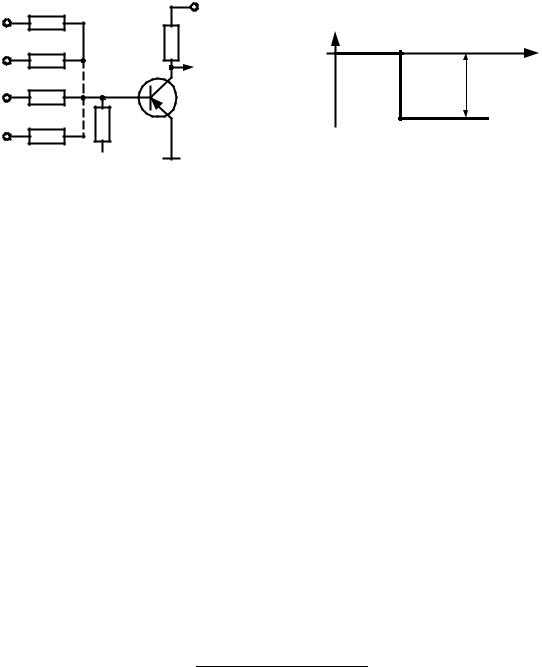

§ 13.1. РЕЗИСТОРНО-ТРАНЗИСТОРНАЯ ЛОГИКА

Схема РТЛ-элемента представлена на рис. 13.2 и характеризуется использованием входных резисторов Rб1 , Rб2 ,…, Rбn , образующих вместе с

143

цепью R – Eб логическую схему ИЛИ, включенную перед ключоминвертором на БТ с общим эмиттером. Схема РТЛ-элемента отличается от обычного транзисторного ключа с ОЭ лишь тем, что здесь вместо одного входного сопротивления базы Rб используют n таких резисторов, подключенных к одной точке – базе транзистора. Данную схему можно рассматривать как транзисторный ключ со многими входами. Кодировка входных сигналов имеет вид, представленный на рис. 13.3.

u |

вх1 |

Rб1 |

- E |

к |

|

|

|

||

uвх2 |

Rб2 |

Rк |

|

|

|

|

|

Vк |

|

uвхn |

Rбn |

R |

|

|

+ Eб

+ Eб

Рис. 13.2. РТЛ-элемент ИЛИ-НЕ

uвх

"0" |

E |

t |

|

|

|

|

"1" |

|

Рис. 13.3. Кодировка входных сигналов

Принцип работы. Если на все входы подать положительный потенциал, то потенциал базы оказывается высоким и при правильно выбранных параметрах положительным (благодаря наличию источника + Eб ). Транзистор при этом находится в закрытом состоянии, а потенциал коллектора принимает минимальное значение (Vк = 1).

Если хотя бы на один из входов подается единица, то потенциал базы понижается, транзистор отпирается и при правильно выбранных параметрах переходит в режим насыщения. Потенциал коллектора при этом становится близким к нулю (Vк = 0). При подаче логической единицы на большее число входов транзистор оказывается еще более насыщенным и попрежнему Vк = 0.

Таким образом, для нормального функционирования РТЛ-элемента должно выполняться условие запирания транзистора, когда

uвх 1 = uвх 2 = ... = uвх n = 0,

и условие насыщения при любых других сочетаниях входных сигналов. При выполнении указанных условий рассмотренный РТЛ-элемент

выполняет логическую операцию ИЛИ-НЕ

Vк = uвх 1 + uвх 2 + ... + uвх n .

144

Основные характеристики

1) Низкое быстродействие, которое объясняется двумя причинами. Во-первых, степень насыщения открытого транзистора зависит от числа входов, на которые поданы сигналы логической единицы. Если выбрать режим так, чтобы транзистор находился на грани насыщения при подаче логической единицы на один вход, то при подаче логической единицы на все входы степень насыщения возрастет приблизительно в n раз. Последнее обстоятельство приводит к увеличению задержки выключения транзистора.

Во-вторых, в данной схеме невозможно использовать конденсаторы для ускорения переходных процессов. Включение ускоряющих емкостей параллельно резисторам Rб привело бы к прямому прохождению перепадов напряжения с одного входа на другие, т.е. к нарушению развязки между входами.

2) Максимальное число входов (n) ограничено ростом степени насыщения в наиболее неблагоприятном случае. Кроме того, увеличение n может привести к нарушению условий нормального функционирования ключа – выполнение условий запирания и насыщения затрудняется.

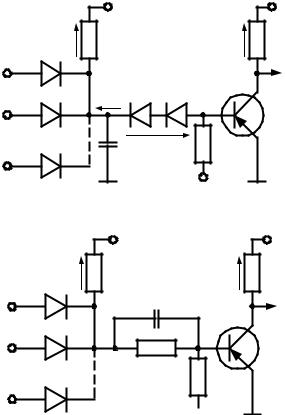

§ 13.2. ДИОДНО-ТРАНЗИСТОРНАЯ ЛОГИКА

Схема ДТЛ-элемента представлена на рис. 13.4 и характеризуется использованием входной диодной логической схемы И (диоды Д1, Д2 ,…,

Дn , резистор R0 и источник – E0 ) с транзисторным ключом-инвертором. Связь входной логической схемы и ключа-инвертора здесь осуществляется цепью из двух последовательно включенных диодов смещения Дсм1 и Дсм2 (рис. 13.4, а) или резистивно-емкостной связью (рис. 13.4, б).

Принцип работы. Кодировка входных сигналов имеет вид, представленный на рис. 13.3. При одновременной подаче сигнала логической единицы (“1”) на все входы uвх 1 = uвх 2 = ... = uвх n = 1 все входные диоды Д1, Д2 ,…, Дn оказываются закрытыми (см. рис. 13.4, а). Параметры цепи E0 , R0 , Дсм1, Дсм2 , Eб и R выбираются так, чтобы потенциал базы транзистора при этом был отрицательным, а транзистор находился в насыщен-

145

ном состоянии. Тогда выходной потенциал схемы принимает значение, близкое к нулю (Vк = 0).

|

|

iR0 |

- E0 |

|

|

- Eк |

|

|

R0 |

|

iRк |

Rк |

|

u |

вх 1 |

Д1 |

|

|||

|

|

|

|

|||

|

|

|

|

|

Vк |

|

uвх 2 |

Д2 |

iДсм Дсм1 |

Дсм2 |

|

||

|

|

|||||

uвх n |

Дn |

А |

|

R |

|

|

Uсм |

|

|||||

|

|

|

СА |

|

+ Eб |

|

|

|

|

|

|

|

|

а)

|

iR0 |

- E0 |

- Eк |

|

R0 |

iRк Rк |

|

u |

Д1 |

||

вх 1 |

|

С |

Vк |

u |

Д2 |

|

|

|

|

||

вх 2 |

|

|

|

u |

Дn |

А Rб |

R |

вх n |

|

|

|

+ Eб

+ Eб

б)

Рис. 13.4 ДТЛ-элемент И-НЕ: а – с диодной связью; б – с резистивно-емкостной связью

При подаче логического нуля на один или несколько входов соответствующие входные диоды открываются и потенциал точки А повышается. Однако падение напряжения на цепочке диодов смещения Дсм1 – Дсм2 остается практически постоянным независимо от состояния элемента.

Благодаря постоянству величины Uсм увеличение потенциала точки А при отпирании хотя бы одного входного диода приводит к равному по величине повышению потенциала базы. Падение напряжения на диодах смещения Uсм при этом компенсирует сумму падений напряжений на входном диоде и насыщенном транзисторе предшествующего элемента. Последнее при правильном выборе параметров схемы приводит к запиранию транзистора рассматриваемого элемента и изменению выходного напряжения до уровня, соответствующего логической единице. Таким обра-

146

зом, сигнал на выходе элемента представляет собой результат операции И-НЕ над входными переменными

Vк = uвх 1 uвх 2 ... uвх n .

Схема ДТЛ-элемента с резистивно-емкостной связью (см. рис. 13.4, б) представляет собой сочетание диодного элемента И и транзисторного ключа с резистивно-емкостной связью. Принцип работы данной схемы не отличается от рассмотренного выше, однако обладает рядом недостатков. Во-первых, реализация цепи Rб – С в интегральном исполнении представляется чрезвычайно сложной задачей в силу малых значений сопротивления Rб и больших значений емкости С. Во-вторых, требуемая величина перепада входного напряжения во второй схеме становится значительно большей. Так, при переходе элемента из закрытого в открытое состояние падение напряжения на резисторе Rб возрастает на некоторую величину uRб , потому что ток iR0 , который замыкался ранее в основном

через входные диоды, теперь протекает через Rб . Если увеличение тока через цепь связи в первой схеме не вызывало заметного увеличения падения напряжения на диодах смещения, то во второй схеме при использовании сопротивления Rб падение напряжения на элементе связи возрастает пропорционально току. Таким образом, перепад в точке А увеличивается на величину uRб , что требует увеличения входного логического перепада,

который при заданной величине входного тока приводит к росту потребляемой элементом мощности.

Основные характеристики

1)Быстродействие элемента, характеризующегося временными задержками включения и выключения здесь, как и в других схемах, определяется инерционностью транзисторов и перезарядом паразитных емкостей.

2)Задержка включения tз вкл определяется в основном временем перезаряда током iR0 суммарной паразитной емкости CA, включенной между

точкой А и “землей” до момента отпирания транзистора.

3) Задержка выключения tз выкл состоит из времени разряда емкостей коллектор-эмиттер Cкэ предыдущих элементов после открывания их тран-

147

зисторов от уровня − Eк до момента отпирания входных диодов и времени рассасывания избыточного заряда базы насыщенного транзистора.

4) Число входов (n) в схемах ДТЛ-элементов не ограничено в такой степени, как это имело место в схемах РТЛ-элементов, нарушением условий запирания и насыщения. Однако рост числа входов n связан с увеличением числа входных диодов и поэтому ведет к увеличению габаритов элемента.

§ 13.3. ТРАНЗИСТОРНО-ТРАНЗИСТОРНАЯ ЛОГИКА

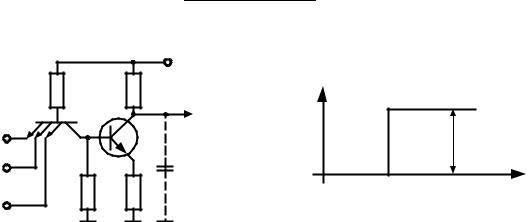

Схема ТТЛ-элемента с простым инвертором

Простейшая схема ТТЛ-элемента, представленная на рис. 13.5, разработана специально для изготовления в интегральном исполнении, а не на дискретных компонентах. При этом элементы данного типа выполняются исключительно на кремниевых n-p-n-транзисторах.

Следует отметить, что схема ТТЛ-элемента аналогична схеме ДТЛэлемента с диодной связью. Здесь роль входных диодов играют эмиттерные переходы, а роль диода смещения – коллекторный переход многоэмиттерного транзистора. При реализации ТТЛ-элементы обеспечивают существенный выигрыш по площади по сравнению с ДТЛ. Поэтому схемы ТТЛ, обладая этим преимуществом и сохраняя общие достоинства ДТЛэлементов, практически вытеснили последние и стали в настоящее время одним из распространенных типов базовых логических элементов (БЛЭ).

Принцип работы. Если на все входы элемента поданы сигналы логической единицы, соответствующие здесь высокому положительному уровню потенциала (рис. 13.6), то все транзисторные структуры, образующие многоэмиттерный транзистор, работают в активном инверсном режиме. При этом оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса источника напряжения Eк , через сопротивление R0 , ба- зу-коллектор транзистора T1 и на базу транзистора T2 . Таким образом, транзистор T2 перейдёт в режим насыщения, и на выходе установится низкий уровень напряжения логического нуля.

Если хотя бы на один из входов будет подаваться сигнал логического нуля, соответствующий эмиттерный переход транзистора T1 будет открыт, 148

и через него будет протекать ток по цепи от плюса источника питания Eк через резистор R0 , базу-эмиттер транзистора T1, общий провод – минус источника питания Eк . В цепи коллектора транзистора T1, а следовательно, и в цепи базы транзистора T2 ток будет отсутствовать. При этом транзистор T2 будет находиться в режиме отсечки, на выходе устанавливается высокий уровень напряжения логической единицы.

Таким образом, сигнал на выходе элемента представляет собой результат операции И-НЕ над входными переменными

|

|

Vк = uвх 1 uвх 2 ... uвх n . |

|||

|

|

|

Eк |

|

|

|

R0 |

Rк |

|

u |

вх |

uвх 1 |

|

|

Vк |

|

"1" |

uвх 2 |

T1 |

T2 |

|

E |

|

|

|

||||

|

Сн |

|

"0" |

||

uвх n |

R |

R |

|

t |

|

|

1 |

2 |

|

||

Рис. 13.5. ТТЛ-элемент И-НЕ |

|

Рис. 13.6. Кодировка входных |

|||

с простым инвертором |

|

|

сигналов |

||

Основные характеристики

1)Быстродействие элемента оказывается высоким из-за весьма быстрого включения и выключения схемы.

2)Число входов (n) в схемах ТТЛ-элементов с простым инвертором равно числу эмиттеров транзистора T1. Увеличение n связано с увеличени-

ем площади, занимаемой этим транзистором, а также увеличением числа выводов микросхемы.

3) Нагрузочная способность ТТЛ-элементов с простым инвертором считается плохой. При подключении нескольких нагрузок возрастают суммарная нагрузочная емкость Cн и постоянная времени, с которой эта емкость заряжается. Для того чтобы ускорить заряд емкости и повысить нагрузочную способность элемента, вместо простого инвертора, состоящего из одного транзистора, используют сложный инвертор.

149

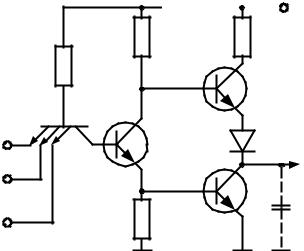

Схема ТТЛ-элемента со сложным инвертором

Схема ТТЛ-элемента со сложным инвертором, состоящим из трех транзисторов и диода, представлена на рис. 13.7.

|

Rк1 |

|

Rк2 |

Eк |

|

||

|

|

|

|

||||

|

R0 |

|

|

T3 |

|

|

|

|

|

|

|

|

|

||

uвх 1 |

T |

|

Д1 |

|

|

Vк |

|

uвх 2 |

2 |

|

|

|

|||

T1 |

|

|

|

|

|

||

|

|

|

|

|

|

||

uвх n |

R1 |

|

T |

4 |

С |

н |

|

|

|

|

|

||||

|

|

|

|

|

|

||

Рис. 13.7. ТТЛ-элемент И-НЕ |

|

|

|

|

|||

со сложным инвертором |

|

|

|

|

|

||

Принцип работы. Если на все входы элемента поданы сигналы логической единицы uвх 1 = uвх 2 = ... = uвх n = 1, соответствующие высокому положительному уровню потенциала, то эмиттерные переходы многоэмиттерного транзистора закрываются. Ток в этом случае протекает по цепи от плюса источника напряжения Eк , через сопротивление R0 , переход базаколлектор транзистора T1 и на базу транзистора T2 . Транзистор T2 переходит в режим насыщения. Ток через него, а следовательно, и ток базы транзистора T4 будет максимальным, и транзистор T4 перейдет в режим насыщения. На выходе схемы формируется низкий уровень логического нуля. При этом напряжение на коллекторе транзистора T2 и на базе транзистора T3 близко к нулю. Следовательно, транзистор T3 находится в закрытом состоянии. Диод Д1 в данной схеме используется для более надежного запирания транзистора T3.

Если хотя бы на одном из входов будет действовать сигнал уровня логического нуля, соответствующий эмиттерный переход будет открыт, и через него будет протекать ток по цепи от плюса источника напряжения

150