- •Организация памяти Характеристики устройств памяти

- •Иерархическая структура памяти эвм

- •Виды памяти Постоянная память пзу

- •Оперативная память

- •Физическая структура оп

- •Виды динамических запоминающих устройств.

- •Кэш-память

- •Стековая память

- •Защита памяти

- •Ключи защиты

- •Кольца защиты

- •Метод граничных регистров

- •Вопросы для самопроверки

- •4.4.4. Методы повышения пропускной способности оперативной памяти

- •4.4.5. Методы защиты памяти

- •4.4.6. Методы ускорения процессов обмена между оп и взу

- •Интерфейсы

- •Характеристики интерфейсов

- •Внутренние интерфейсы

- •Интерфейсы внешней памяти.

- •Универсальные последовательные интерфейсы.

- •Беспроводные интерфейсы

- •Вопросы для самопроверки

Вопросы для самопроверки

Дайте классификацию запоминающих устройств ПК.

Приведите определение статической и динамической оперативной памяти и укажите, где используются эти виды памяти.

Приведите логическую структуру ОП.

Каково назначение ПЗУ?

Дайте краткую характеристику накопителей на дисках разного типа.

4.4.4. Методы повышения пропускной способности оперативной памяти

Основными методами увеличения полосы пропускания памяти являются: увеличение разрядности или «ширины» памяти, использование расслоения памяти, использование независимых банков памяти, обеспечение режима бесконфликтного обращения к банкам памяти, использование специальных режимов работы динамических микросхем памяти.

Выборка широким словом

Прямой способ сокращения числа обращений к ОП состоит в организации выборки широким словом. Этот способ основывается на свойстве локальности данных и программ. При выборке широким словом за одно обращение к ОП производится одновременная запись или считывание нескольких команд или слов данных из «широкой» ячейки. Широкое слово заносится в буферную память (кэш-память) или регистр, где оно расформировывается на отдельные команды или слова данных, которые могут последовательно использоваться процессором без дополнительных обращений к ОП.

В системах с кэш-памятью первого уровня ширина шин данных ОП часто соответствует ширине шин данных кэш-памяти, которая во многих случаях имеет физическую ширину шин данных, соответствующую количеству разрядов в слове. Удвоение и учетверение ширины шин кэш-памяти и ОП удваивает или учетверяет соответственно полосу пропускания системы памяти.

Реализация выборки широким словом вызывает необходимость мультиплексирования данных между кэш-памятью и процессором, поскольку основной единицей обработки данных в процессоре все еще остается слово. Эти мультиплексоры оказываются на критическом пути поступления информации в процессор. Кэш-память второго уровня несколько смягчает эту проблему, т.к. в этом случае мультиплексоры могут располагаться между двумя уровнями кэш-памяти, т.е. вносимая ими задержка не столь критична. Другая проблема, связанная с увеличением разрядности памяти, заключается в необходимости определения минимального объема (инкремента) памяти для поэтапного её расширения, которое часто выполняется самими пользователями во время эксплуатации системы. Удвоение или учетверение ширины памяти приводит к удвоению или учетверению этого минимального инкремента. Кроме того, имеются проблемы и с организацией коррекции ошибок в системах с широкой памятью.

Примером организации широкой ОП является система Alpha AXP21064, в которой кэш второго уровня, шина памяти и сама ОП имеют разрядность 256 бит.

Расслоение обращений

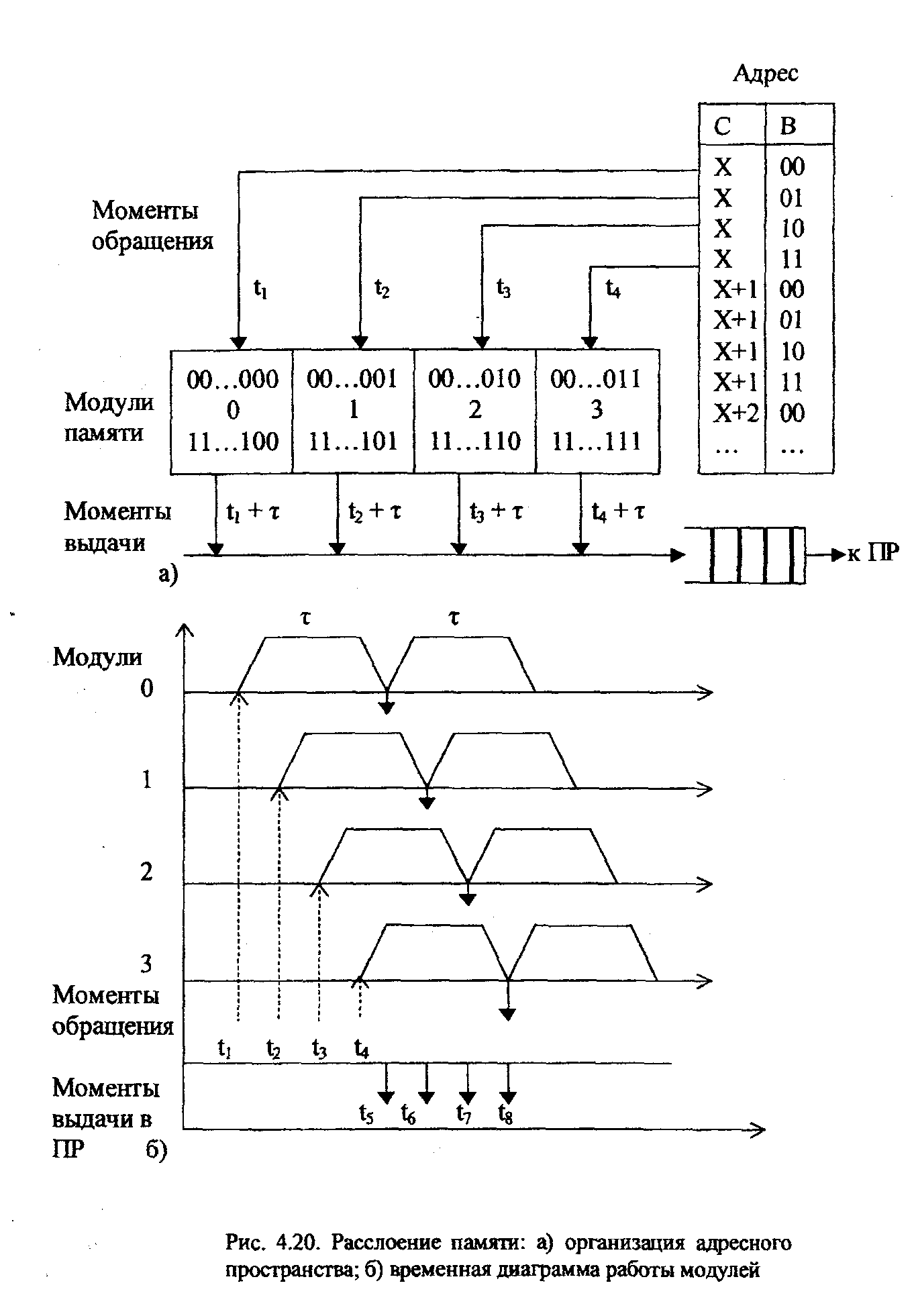

Другой способ повышения пропускной способности ОП связан с построением памяти, состоящей на физическом уровне из нескольких модулей (банков) с автономными схемами адресации, записи и чтения. При этом на логическом уровне управления памятью организуются последовательные обращения к различным физическим модулям. Обращения к различным модулям могут перекрываться, и таким образом образуется своеобразный конвейер. Эта процедура носит название расслоения памяти. Целью данного метода является увеличение скорости доступа к памяти посредством совмещения фаз обращений ко многим модулям памяти. Известно несколько вариантов организации расслоения. Наиболее часто используется способ расслоения обращений за счет расслоения адресов. Этот способ основывается на свойстве локальности программ и данных, предполагающем, что адрес следующей команды программы на единицу больше адреса предыдущей (линейность программ нарушается только командами перехода). Аналогичная последовательность адресов генерируется процессором при чтении и записи слов данных. Таким образом, типичным случаем распределения адресов обращений к памяти является последовательность вида а, а+ 1, а + 2,... Из этого следует, что расслоение обращений возможно, если ячейки с адресами а, а+ 1, а + 2,... будут размещаться в блоках 0, 1,2,... Такое распределение ячеек по модулям (банкам) обеспечивается за счет использования адресов вида

где В - к-разрядный адрес модуля (младшая часть адреса) и С - п-разрядный адрес ячейки в модуле В (старшая часть адреса).

Принцип расслоения обращений иллюстрируется на рис. 4.20,а. Все программы и данные «размещаются» в адресном пространстве последовательно. Однако ячейки памяти, имеющие смежные адреса, находятся в различных физических модулях памяти. Если ОП состоит из 4-х модулей, то номер модуля кодируется двумя младшими разрядами адреса. При этом полные т-разрядные адреса 0, 4, 8,... будут относиться к блоку 0, адреса 1, 5, 9, ... - к блоку 1, адреса 2, 6, 10,... — к блоку 2 и адреса 3, 7, 11,... - к блоку 3. В результате этого последовательность обращений к адресам 0, 1, 2, 3, 4, 5, ... будет расслоена между модулями 0,1,2,3,0,1,....

Поскольку каждый физический модуль памяти имеет собственные схемы управления выборкой, можно обращение к следующему модулю производить, не дожидаясь ответа от предыдущего. Так на временной диаграмме (рис. 4.20,6) показано, что время доступа к каждому модулю составляет т = 4Т, где Т = ti+1-ti - длительность такта. В каждом такте следуют непрерывно обращения к модулям памяти в моменты времени t1, t2, t3 ... .